СО со

4i)b

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодовый замок | 1980 |

|

SU924733A1 |

| Устройство для контроля и управления магистралью приборного интерфейса | 1986 |

|

SU1381514A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2001 |

|

RU2199148C1 |

| Устройство для диспетчерского управления автотранспортом | 1983 |

|

SU1218412A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ИСКАЖЕНИЯ ИНФОРМАЦИОННОГО ЦИФРОВОГО ПОТОКА | 2004 |

|

RU2273045C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для контроля знаний обучаемых | 1980 |

|

SU982061A1 |

| Устройство для контроля параметров сложных систем | 1984 |

|

SU1205084A1 |

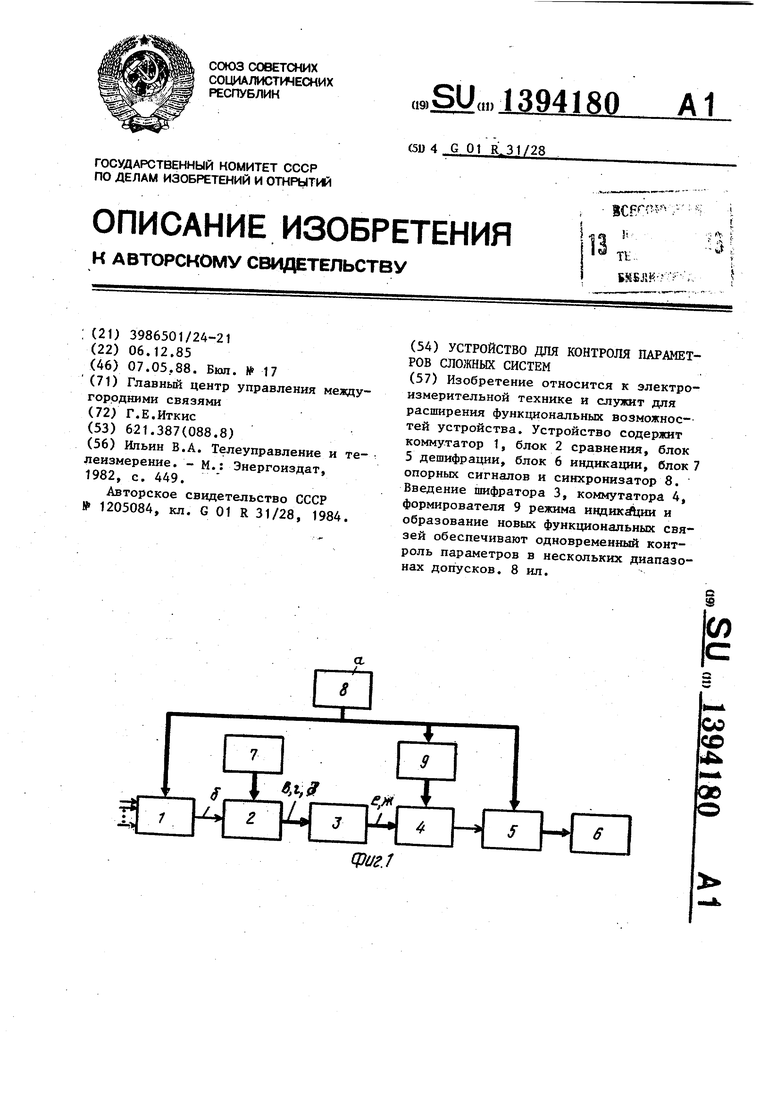

Изобретение относится к электроизмерительной технике и служит для расширения функциональных возможностей устройства. Устройство содержит коммутатор 1, блок 2 сравнения, блок 5 дешифрации, блок 6 индикации, блок 7 опорных сигналов и синхронизатор 8. Введение шифратора 3, коммутатора 4, формирователя 9 режима индик ини и образование новых функциональных связей обеспечивают одновременный контроль параметров в нескольких диапазонах допусков. 8 ил.

г/

Изобретение относится к электро- «змерительной технике и может быть яспользовано для оперативного контроля технических объектов по электричес КИМ сигналам от них.

Цель изобретения - расширение функциональных возможностей путем обеспечения одновременного контроля . параметров в нескольких диапазонах допусков.

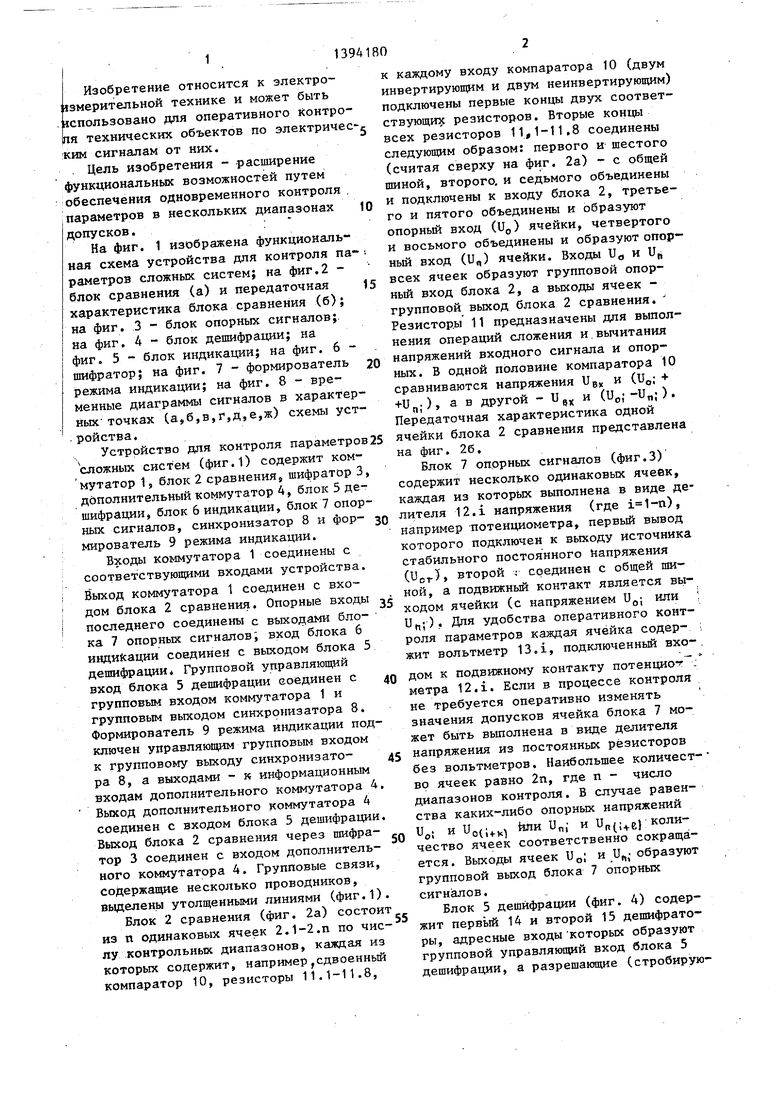

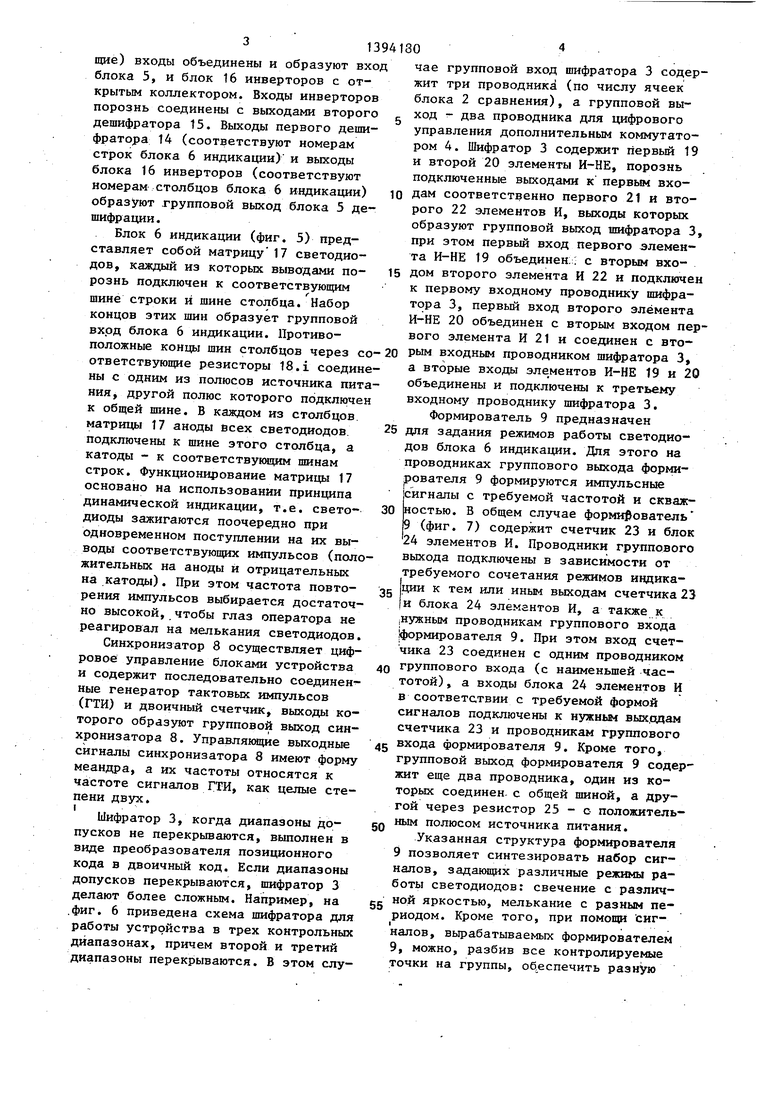

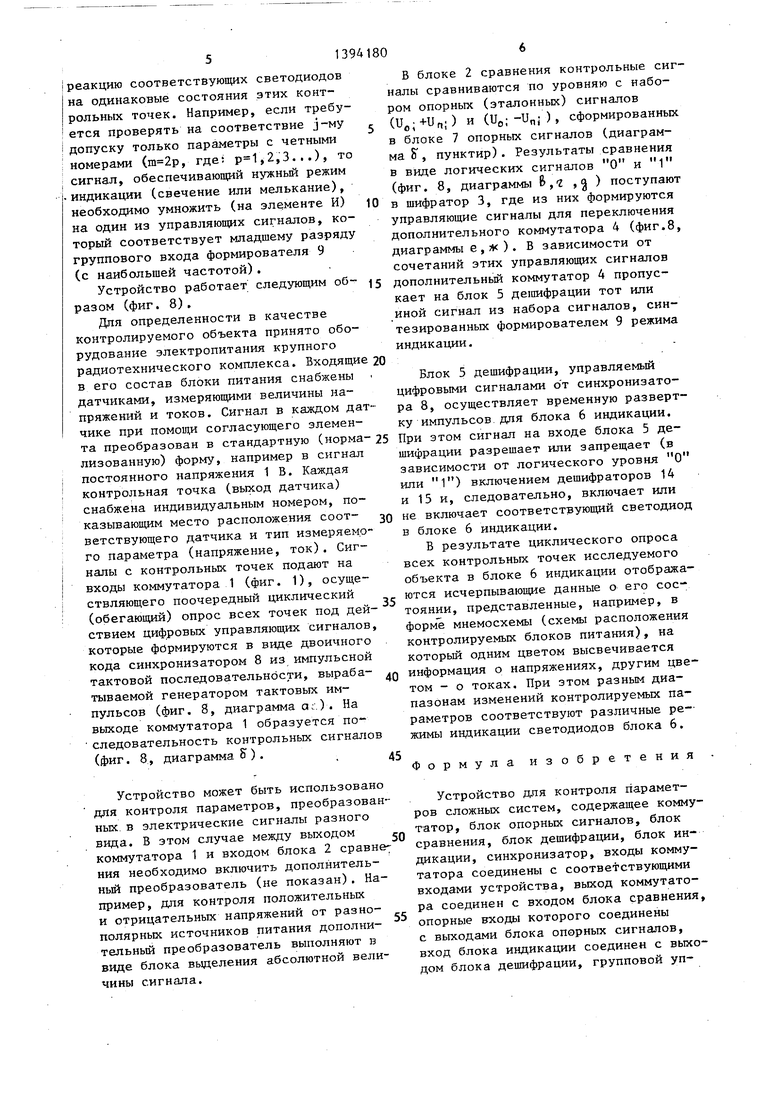

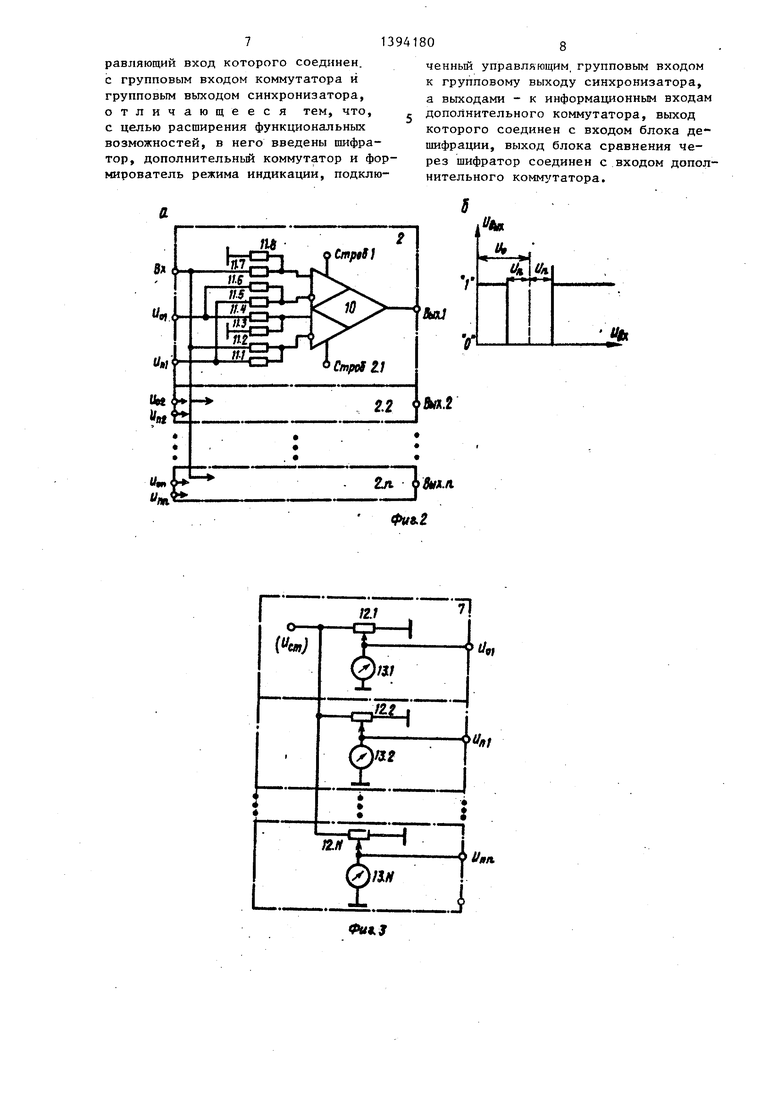

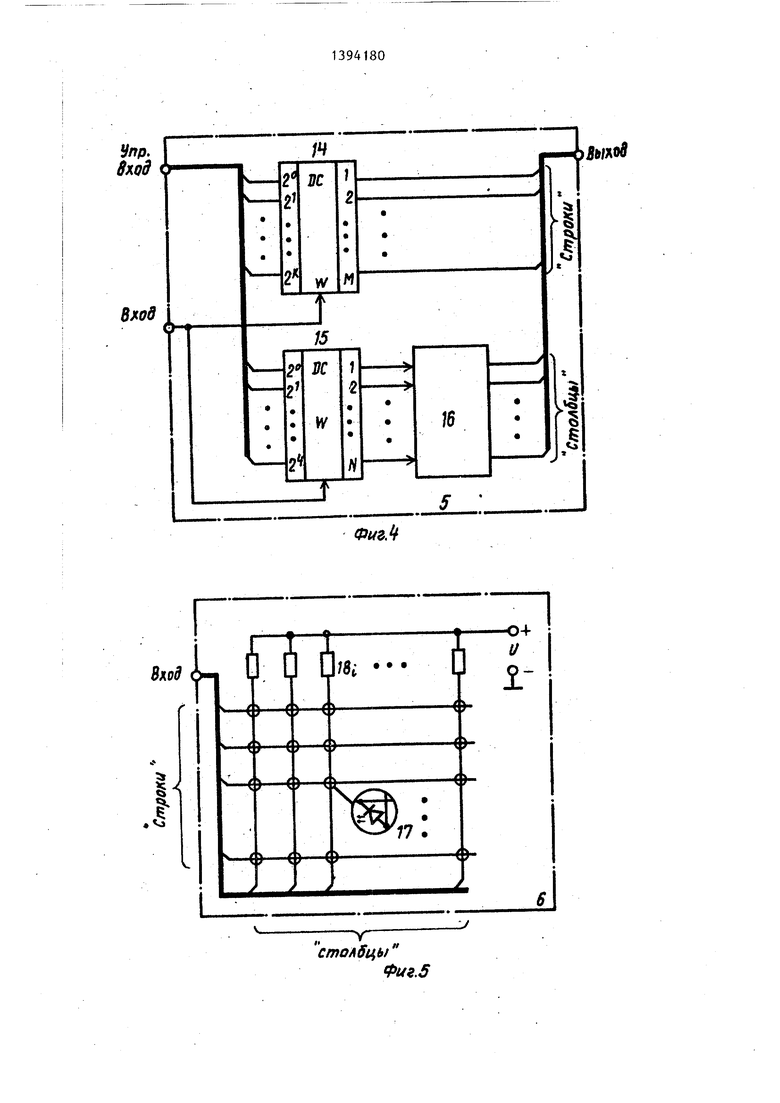

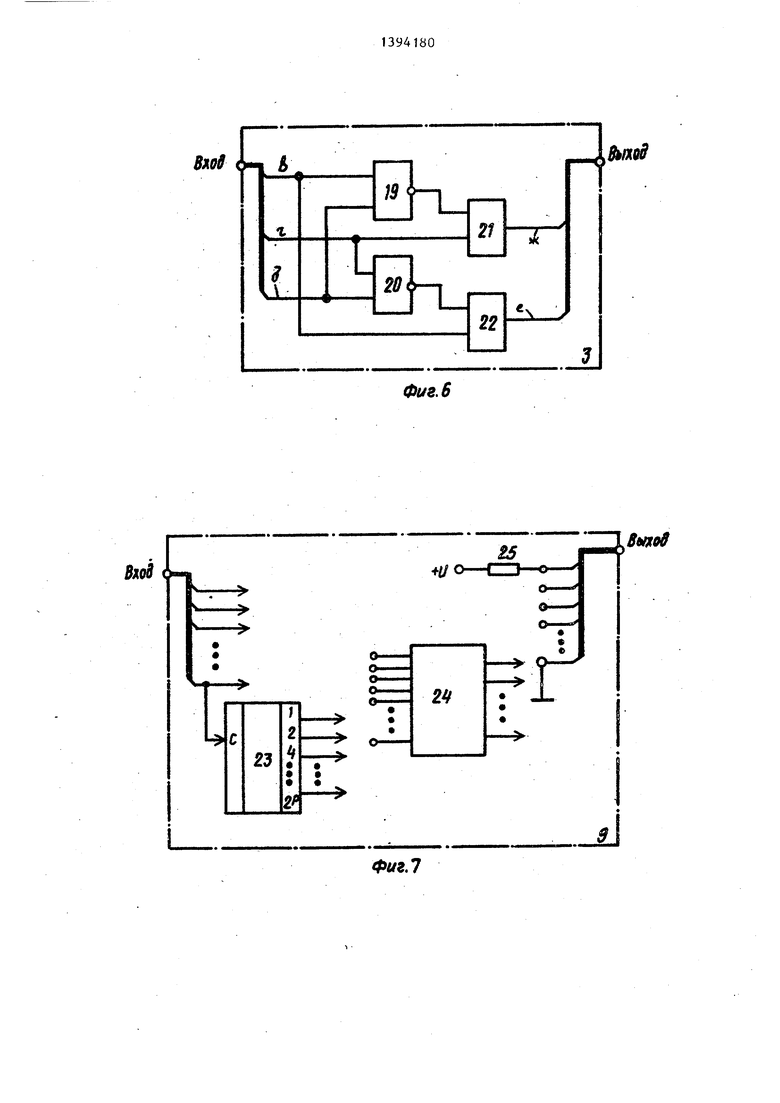

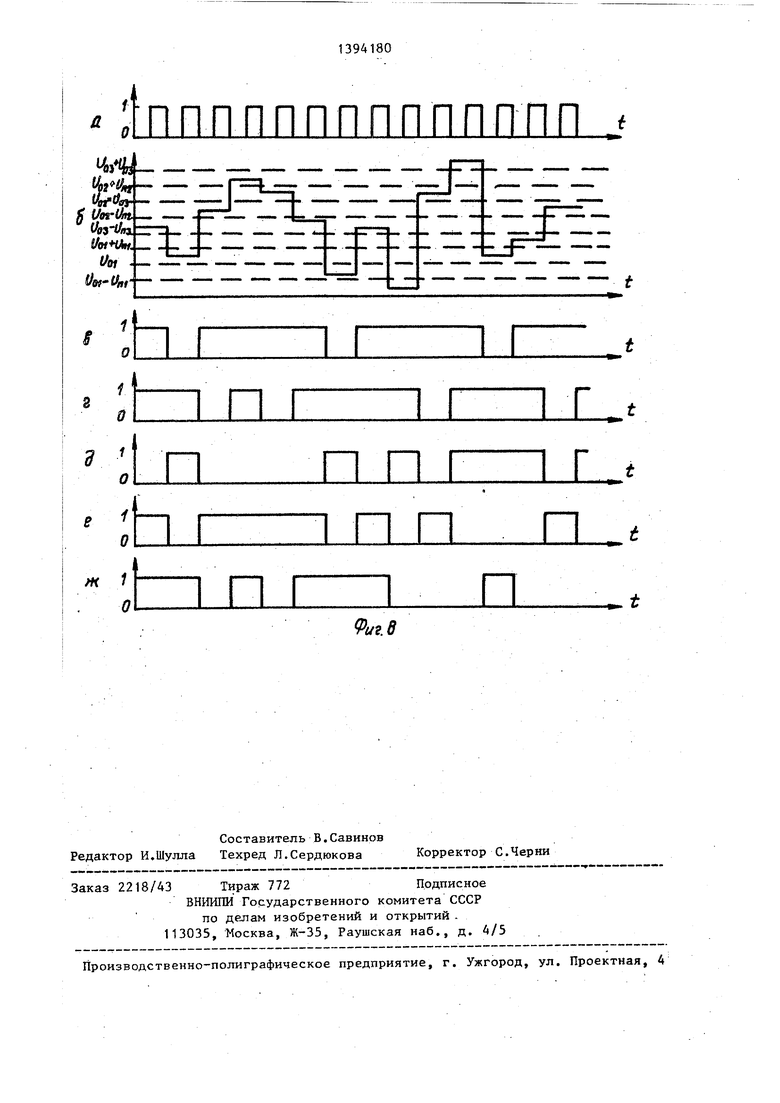

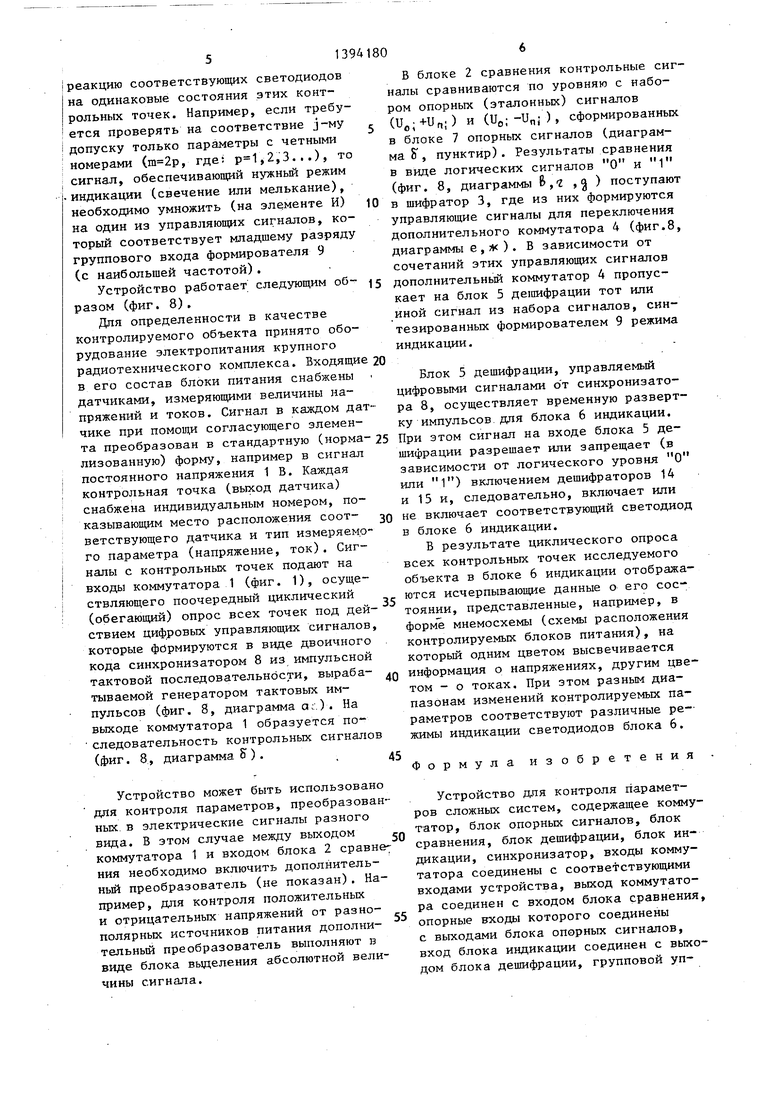

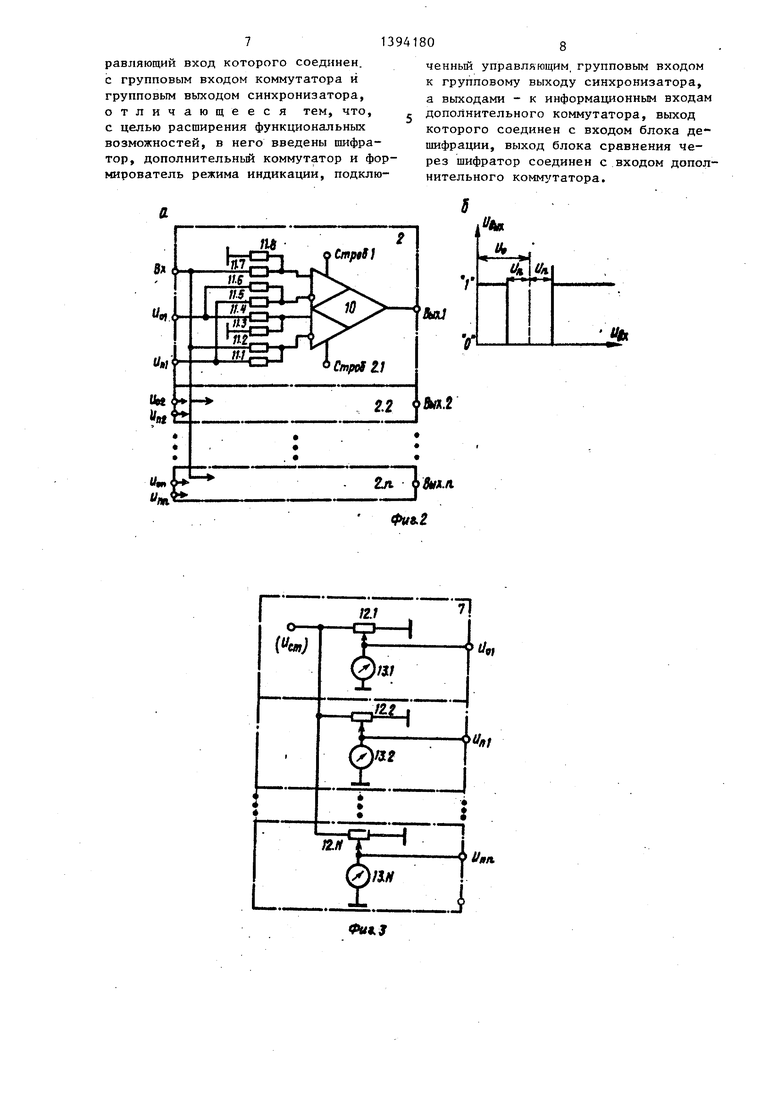

На фиг. 1 изображена функциональная схема устройства для контроля па- раметров сложных систем; на фиг.2 - блок сравнения (а) и передаточная характеристика блока сравнения (б); на фиг. 3 - блок опорных сигналов; на фиг. 4 - блок дешифрации; на фиг. 5 - блок индикации; на фиг. 6 - шифратор; на фиг. 7 - формирователь режима индикации; на фиг. 8 - временные диаграммы сигналов в характерных точках (а,б,в,г,д,е,ж) схемы устройства.

Устройство для контроля параметров сложных систем (фиг.1) содержит ком- мутатор 1J блок 2 сравнения, шифратор 3, дополнительный коммутатор 4, блок 5 дешифрации, блок 6 индикации, блок 7 опорных сигналов, синхронизатор 8 и фор- мирователь 9 режима индикации.

Входы коммутатора 1 соединены с соответствующими входами устройства. Выход коммутатора 1 соединен с входом блока 2 сравнения. Опорные входы последнего соединены с выходами блока 7 опорных сигналов; вход блока 6 индикации соединен с выходом блока 5 дешифрации Групповой управляющий вход блока 5 дешифрации соединен с групповым входом коммутатора 1 и групповым выходом синхронизатора 8. Формирователь 9 режима индикации подключен управляющим групповым входом к групповому выходу синхронизато- ра 8, а выходами - к информационным входам дополнительного коммутатора 4 Выход дополнительного коммутатора 4 соединен с входом блока 5 дешифрации. Выход блока 2 сравнения через шифра- тор 3 соединен с входом дополнительного коммутатора 4. Групповые связи, содержащие HecKOJtbKo проводников, выделены утолщенными линиями (фиг.1) Блок 2 сравнения (фиг. 2а) состоит из п одинаковых ячеек 2.1-2.П по числу контрольных диапазонов, каждая из которых содержит, например,сдвоенный компаратор 10, резисторы 11.1-11.8,

с д 5 j.

5

к каждому входу компаратора 10 (двум инвертирующим и двум неинвертирующим) подключены первые концы двух соответствующие: резисторов. Вторые концы всех резисторов 11,1-11.8 соединены следуюш 1м образом: первого и- шестого (считая сверху на фиг. 2а) - с общей шиной, второго, и седьмого объединены и подключены к входу блока 2, третьего и пятого объединены и образуют опорный вход (Up) ячейки, четвертого и восьмого объединены и образуют опор- ньй вход (11„) ячейки. Входы U и U, всех ячеек образуют групповой опорный вход блока 2, а выходы ячеек - групповой выход блока 2 сравнения. Резисторы 11 предназначены для выполнения операций сложения и вычитания напряжений входного сигнала и опорных. В одной половине компаратора 10 сравниваются напряжения UB,( и (Uj,; +и„;), а в другой - Ugx и (и.). Передаточная характеристика одной ячейки блока 2 сравнения представлена на фиг. 26.

Блок 7 опорных сигналов (фиг.3) содержит несколько одинаковых ячеек, каждая из которьк выполнена в виде делителя 12.1 напряжения (где ), например тютенциометра, первый вывод которого подключен к выходу источника стабильного постоянного Напряжения (Ujj,.), второй г соединен с общей шиной, а подвижньй контакт является выходом ячейки (с напряжением 1); или , Uf,;), Дпя удобства оперативного контроля параметров каждая ячейка содер- жит вольтметр 13.1, подключенный вхо-,

-

дом к подвижному контакту потенциот : метра 12.1. Если в процессе контроля не требуется оперативно изменять значения допусков ячейка блока 7 может быть вьшолнена в виде делителя напряжения из постоянных резисторов без вольтметров. Наибольшее количест- во ячеек равно 2п, где п - число диапазонов контроля. В случае равенства каких-либо опорных напряжений УО и Uo(i или и„; и количество ячеек соответственно сокращается . Выходы ячеек U QJ и и„ образуют групповой выход блока 7 опорных сигналов.

Блок 5 дешифрации (фиг. 4) содержит первь й 14 и второй 15 дешифраторы, адресные входы которых образуют групповой управляющий вход блока 5 дешифрации, а разрешающие (стробирующие) входы объединены и образуют вход блока 5, и блок 16 инверторов с открытым коллектором. Входы инверторов порознь соединены с выходами второго дешифратора 15. Выходы первого дешифратора 14 (соответствуют номерам строк блока 6 индикации) и выходы блока 16 инверторов (соответствуют номерам столбцов блока 6 индикации) образуют групповой выход блока 5 дешифрации .

Блок 6 индикации (фиг. 5) представляет собой матрицу 17 светодио- дов, каждый из которых выводами порознь подключен к соответствующим

f

шине строки и шине столбца. Набор концов этих шин образует групповой вход блока 6 индикации. Противочае групповой вход шифратора 3 содер жит три проводника (по числу ячеек блока 2 сравнения), а групповой выход - два проводника для цифрового управления дополнительным коммутатором 4. Шифратор 3 содержит первый 19 и второй 20 элементы И-НЕ, порознь подключенные выходами к первым входам соответственно первого 21 и второго 22 элементов И, выходы которых образуют групповой выход шифратора 3 при этом первый вход первого элемента И-НЕ 19 объединен:; с вторым вхо- 15 дом второго элемента К 22 и подключе к первому входному проводнику шифратора 3, первый вход второго элемента И-НЕ 20 объединен с вторым входом пе вого элемента И 21 и соединен с вто10

положные концы шин столбцов через со- 20 Рым входным проводником шифратора 3,

а вторые входы элементов И-НЕ 19 и 2 объединены и подключены к третьему входному проводнику шифратора 3. Формирователь 9 предназначен

ответствующие резисторы 18.1 соединены с одним из полюсов источника питания, другой полюс которого подключен к общей шине. В каждом из столбцов матрицы 17 аноды йсех светодиодов. подключены к шине этого столбца, а катоды - к соответствующим шинам строк. Функционирование матрицы 17 основано на использовании принципа динамической индикации, т.е. свето- диоды зажигаются поочередно при одновременном поступлении на их выводы соответствующих импульсов (положительных на аноды и отрицательных на катоды). При этом частота повторения импульсов выбирается достаточно высокой, чтобы глаз оператора не реагировал на мелькания светодиодов. Синхронизатор 8 осуществляет цифровое управление блоками устройства и содержит последовательно соединен ные генератор тактовых импульсов (ГТИ) и двоичный счетчик, выходы которого образуют групповой выход синхронизатора 8. Управляющие выходные сигналы синхронизатора 8 имеют форму меандра, а их частоты относятся к частоте сигналов ГТИ, как целые степени двух.

Шифратор 3, когда диапазоны допусков не перекрываются, выполнен в виде преобразователя позиционного кода в двоичный код. Если диапазоны допусков перекрываются, шифратор 3 делают более сложным. Например, на .фиг. 6 приведена схема шифратора для работы устройства в трех контрольных диапазонах, причем второй и третий диапазоны перекрываются. В этом случае групповой вход шифратора 3 содержит три проводника (по числу ячеек блока 2 сравнения), а групповой выход - два проводника для цифрового управления дополнительным коммутатором 4. Шифратор 3 содержит первый 19 и второй 20 элементы И-НЕ, порознь подключенные выходами к первым входам соответственно первого 21 и второго 22 элементов И, выходы которых образуют групповой выход шифратора 3, при этом первый вход первого элемента И-НЕ 19 объединен:; с вторым вхо- дом второго элемента К 22 и подключен к первому входному проводнику шифратора 3, первый вход второго элемента И-НЕ 20 объединен с вторым входом первого элемента И 21 и соединен с вто

Рым входным проводником шифратора 3,

а вторые входы элементов И-НЕ 19 и 20 объединены и подключены к третьему входному проводнику шифратора 3. Формирователь 9 предназначен

для задания режимов работы светодиодов блока 6 индикации. Для этого на проводниках группового выхода формирователя 9 формируются импульсные сигналы с требуемой частотой и скважностью. В общем случае формирователь 9 (фиг. 7) содержит счетчик 23 и блок 24 элементов И. Проводники группового выхода подключены в зависимости от требуемого сочетания режимов индикации к тем или иным выходам счетчика 23 и блока 24 элементов И, а также к |Нужным проводникам группового входа формирователя 9. При этом вход счетчика 23 соединен с одним проводником группового входа (с наименьшей частотой) , а входы блока 24 элементов И в соответствии с требуемой формой сигналов подключены к нужньы вых.одам счетчика 23 и проводникам группового

входа формирователя 9. Кроме того,

групповой выход формирователя 9 содержит еще два проводника, один из которых соединен, с общей шиной, а другой через резистор 25 - с положительным полюсом источника питания.

Указанная структура формирователя 9 позволяет синтезировать набор сигналов, задающих различные режимы раоты светодиодов: свечение с различной яркостью, мелькание с разным периодом. Кроме того, при помоищ сигалов, вырабатываемых формирователем , можно, разбив все контролируемые очки на группы, об еспечить разную

реакцию соответствующих светодиодов на одинаковые состояния этих контрольных точек. Например, если требу- ется проверять на соответствие j-му допуску только параметры с четными номерами (, где; ,2,3...) то сигнал, обеспечивающий нужньй режим индикации (свечение или мелькание), необходимо умножить (на элементе И) на один из управляющих сигналов, который соответствует младшему разряду группового входа формирователя 9 (с наибольшей частотой).

Устройство работает следующим образом (фиг. 8),

Для определенности в качестве контролируемого объекта принято оборудование электропитания крупного радиотехнического комплекса. Входящие в его состав блоки питания снабжены датчиками, измеряющими величины напряжений и токов. Сигнал в каждом датчике при помощи согласующего элемента преобразован в стандартную (нормализованную) форму, например в сигнал постоянного напряжения 1 В. Каждая контрольная точка (выход датчика) снабжена индивидуальным номером, показывающим место расположения соответствующего датчика и тип измеряемого параметра (напряжение, ток). Сигналы с контрольных точек подают на входы коммутатора 1 (фиг. 1), осуществляющего поочередный циклический (обегающий) опрос всех точек под действием цифровых управляющих сигналов, которые формируются в виде двоичного кода синхронизатором 8 из импульсной тактовой последовательности, вырабатываемой генератором тактовых импульсов (фиг. 8, диаграмма а:.) . На выходе коммутатора 1 образуется по- следовательность контрольных сигналов (фиг. 8, диаграмма 8i ).

Устройство может быть использовано для контроля параметров, преобразованных в электрические сигналы разного вида. В этом случае между выходом CQ коммутатора 1 и входом блока 2 сравне ния необходимо включить дополнитель- ньй преобразователь (не показан). Например, для контроля положительньк и отрицательных напряжений от разно- полярных источников питания дополнительный преобразователь выполняют в виде блока выделения абсолютной величины сигнала.

55

0

5

0

5

0

5

0

5

CQ

5

В блоке 2 сравнения контрольные сигналы сравниваются по уровняю с набором опорных (эталонных) сигналов

(,;) И (UQ; -Uni ) , Сформированных

в блоке 7 опорных сигналов (диаграмма Ь , пунктир) . Результаты сравнения в виде логических сигналов О и 1 (фиг. 8, диаграммы В, , ) поступают в шифратор 3, где из них формируются управляющие сигналы для переключения дополнительного коммутатора 4 (фиг.8, диаграммы е , тк ). В зависимости от сочетаний этих управляющих сигналов дополнительньй коммутатор 4 пропускает на блок 5 дешифрации тот или иной сигнал из набора сигналов, синтезированных формирователем 9 режима индикации.

Блок 5 дешифрации, управляемый цифровыми сигналами о т синхронизатора 8, осуществляет временную развертку импульсов для блока 6 индикации. При этом сигнал на входе блока 5 дешифрации разрешает или запрещает (в зависимости от логического уровня О или 1) включением дешифраторов 14 и 15 и, следовательно, включает или не включает соответствующий светодиод в блоке 6 индикации.

В результате циклического опроса всех контрольных точек исследуемого объекта в блоке 6 индикации отображаются исчерпывающие данные о его состоянии, представленные, например, в формЪ мнемосхемы (схемы расположения контролируемых блоков питания), на который одним цветом высвечивается информация о напряжениях, другим цветом - о токах. При этом разным диапазонам изменений контролируемых параметров соответствуют различные ре-жимы индикации светодиодов блока 6.

Формула изобретения

Устройство для контроля параметров сложных систем, содержащее коммутатор, блок опорных сигналов, блок сравнения, блок дешифрации, блок индикации, синхронизатор, входы коммутатора соединены с соответствующими входами устройства, выход коммутатора соединен с входом блока сравнения, опорные входы которого соединены с выходами блока опорных сигналов, вход блока индикации соединен с выходом блока дешифрации, групповой управляющий вход которого соединен. с групповым входом коммутатора и групповым выходом синхронизатора, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены шифратор, дополнительньй коммутатор и формирователь режима индикации, подклюдд

ченный управляющим, групповым входом к групповому выходу синхронизатора, а выходами - к информационным входам дополнительного коммутатора, выход которого соединен с входом блока дешифрации, выход блока сравнения через шифратор соединен с входом дополнительного комментатора.

S

Г

SM.2

2л ЬВчлл

Фи9.г

91

столбцы

Фиг.б

ijwxotf

Ь

I г

-21-гL

11

М

2/

-21-гL

-ЫФиг. 6

+f/

1:5

Вьаоб

24

r

.d

Ф«/г.7

пппппппппппппп

ц.

:fa

о

д

П

ж /

L

О

П

t

Ри.в

| Ильин В.А | |||

| Телеуправление и телеизмерение | |||

| - м.: Энергоиздат, 1982, с | |||

| Автоматический сцепной прибор | 1921 |

|

SU449A1 |

| Устройство для контроля параметров сложных систем | 1984 |

|

SU1205084A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-05-07—Публикация

1985-12-06—Подача