3.Устройство по П.1, отличающееся тем, что блок режима содержит первый элемент НЕ, соединен- лый входом с входом блока режима и с размыкающим контактом переключателя, переключающий контакт которого соединен с выходом блока режима, а замыкающий контакт - с.выходом первого элемента НЕ,

4.Устройство по п. 1, отличающееся тем, что блок опорных сигналов содержит первый и второй делители напряжения, соединенные первыми выводами с шиной питания устройства, вторыми выводами - с общей шиной устройства, третьими выводами - соответственно с первым

и вторым выходами блока опорных сигналов, соединенными соответственно через первый и второй вольтме ры с общей шиной устройства,

5.Устройство по п,1, отличающееся тем, что блок дешифрации содержит первый и второй дешифраторы, соединенные входами с информационными -входами блока дешифрации, стробирующими входами - со стробиру- ющим входом блока дешифрации, выходы первого дешифратора соединены с соот- ветствуюш;ими выходами блока дешифрации, выходы второго дешифратора соединены через вторые элементы НЕ с соответствующими выходами блока дешифрации.

Изобретение относится к контрольно-измерительной технике и может быть использовано для допус- кового контроля параметров объектов

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения допускового контроля нескольких параметров и контроля суммарного числа параметров, вышедших за пределы допуска при оперативно изменяемой величине области допустимых значений.

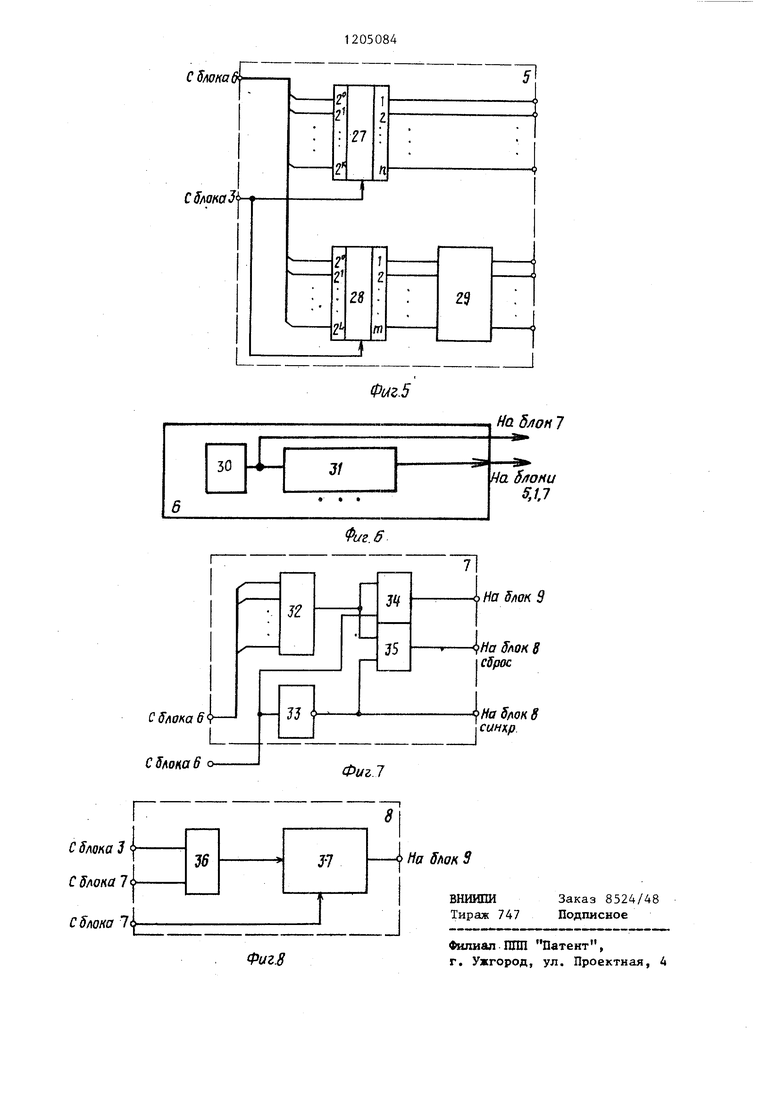

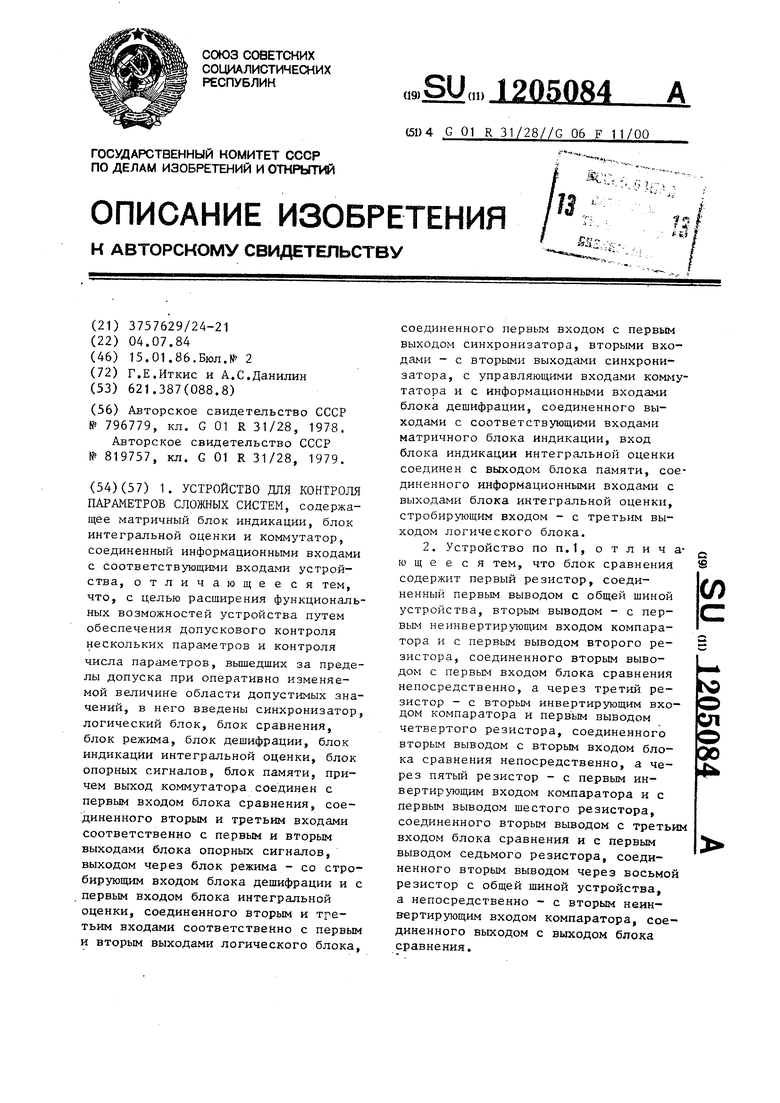

На фиг,1 приведена блок-схема предлагаемого устройства; на фиг,2 QxeMa блока сравнения.; на фиг,3 - схе05084

6.Устройство по п,1, отличающееся тем, что синхронизатор содержит генератор импульсов, соединенный выходом с первым выходом синхронизатора и со счетным входом nepBoi o счетчика, соединенного выходами с вторыми выходами син-- хронизатора.

7.Устройство по п,1, о т л и ч а- ю щ е е с я тем, что логический блок содержит первый элемент И, соединенный входами с вторьми входами логического блока, соединенного первым входом с первым входом второго элемента И непосредственно, а через третий элемент НЕ - с первьм выходом логического блока и с первым входом третьего элемента И, соединенного выходом с вторым выходом логического блока, вторым входом - с выходом первого элемента И и с вторым входом второго элемента И, соединенного выходом с третьим выходом логического блока,

8.Устройство по п,1, отличающее ся тем, что блок интегральной оценки содержит четвертый элемент И, соединенный первым и вторым входами с одноименными

I входами блока интегральной оценки, выходом - со счетным входом второго счетчика, соединенного выходами с выхода1 и блока интегральной оценки, установочным входом - с третьим входом блока интегральной оценки.

ма блока режима; на фиг,4 - схема блока опорных сигналов; на фиг,5 - схема блока дешифрации; на фиг,6 - схема синхронизатора; на фиг.7 - схема логического блока; на фиг,8 - схема блока интегральной оценки.

Устройство содержит коммутатор 1, блок 2 сравнения, блок 3 режима,

блок 4 опорных сигналов, блок 5 дешифрации, синхронизатор 6, логический блок 7, блок 8 интегральной оценки, блок 9 памяти, блок 10 индикации интегральной оценки и матричный блок 11 индикации.

Блок 2 сравнения содержит компаратор 12, первый 13, второй 14, шестой 15, пятый 16, седьмой 17, восьмой 18, третий 19 и четвертый 20 резисторы.

Блок 3 режима содержит первый элемент НЕ 21 и переключатель 22.

Блок 4 опорных сигналов содержит первый 23 и второй 24 делители напряжения и второй 25 и первый 26 вольтметры.

J Блок 5 дешифрации содержит первы 27 и второй 28 дешифраторы и вторые элементы НЕ 29.

Синхронизатор 6 содержит генератор 30 импульсов и первый счетчик 3

Логический блок 7 содержит первый элемент И 32, третий элемент НЕ 33, второй 34 и третий 35 элементы И.

Блок 8 интегральной оценки содержит четвертый 36 элемент И и второй счетчик 37,

Коммутатор 1 выполнен, например, на микросхемах К590КН1.

В блоке 2 сравнения компаратор 12 выполнен, например, на микросхеме 52fCA1.

Блок 9 памяти построен, например на регистре из D-триггеров, имеющих С и D входы.

Блок 10 индикации интегральной оценки выполнен, например, на цифровых индикаторах АЛС324Б, каждьй из которых снабжен дешифратором К314ИД2 на входе.

Коммутатор 1 соединен информационными входами с соответствующими входами устройства, а выходом - с первы входом блока 2 сравнения, соединенного вторым и третьим входами соответственно с первым и BTop bw выходами блока 4 опорных сигналов, выходом через блок 3 режима - со стробирую- щим входом блока 5 дешифрации и с первым, входом блока 8 1нтегральной , соединенного вторым и третьим входами соответственно с первым и вторым выходами логического блока 7 соединенного первым входом с первым выходом синхронизатора 6, вторыми входами - с вторыми выходами синхронизатора 6, с управляющими входами коммутатора 1 и с информационными входами блока 5 дешифрации, соединенного выходами с соответствующими входами матричного блока 11 индикации. Вход блока 10 индикации интегральной оценки соединен с выходом блока 9 памяти, соединенного информационными входами с выходами блока 8 интегральной оценки, стробирующим

входом - с третьим выходом логичес- кого блока 7.

В блоке 2 сравнения первый резистор 13 соединен первым выводом с общей шиной устройства, вторым выводом - с первым неинвертирующим входом компаратора и с первым выводом второго резистора 14, соединенного вторым выводом с первым входом блока 2 сравнения непосредственно, а через

третий резистор 19 - с вторым инвертирующим входом компаратора 12 и с первым выводом четвертого резистора 20, соединенного вторым выводом с вторым входом блока 2 сравнения не посредственно, а через пятый резистор 16 - с первым инвертирующим входом компаратора 12 и с первым выводом шестого резистора 15, соединенного вторым выводом с третьим входом

блока 2 сравнения и с первым выводом седьмого резистора 17, соединенного вторым выводом через восьмой резистор 18 с общей шиной устройства, а непосредственно - с вторым неин- вертирзлощим входом компаратора 12, соединенного выходом с выходом блока 2 сравнения.

в блоке 3 режима первый элемент НЕ 21 соединен входом с входом блока

3 режима и с размыкающим контактом переключателя 22, переключающий контакт которого соединен с выходом блока 3 режима, а замыкающий контакт - с выходом первого элемента

НЕ 21.

В блоке 4 опорных сигналов первый 23 и второй 24 делители напряжения соединены первыми выводами с- шиной питания устройства, вторыми

выводами - с общей шиной устройства, третьими выводами - соответственно с первым и вторьм выходами блока 4 опорных сигналов, соединенными соответственно через первый 26 и второй

25 вольтметры с общей шиной устройства.

В блоке 5 дешифрации первый 27 и второй 28 дешифраторы соединены входами с информационными входами

блока 5 дешифрации, стробирующими входами - со стробирующим входом блока 5 дешифрации, выходы первого дешифратора 27 соединены с соответстнующими выходами блока 5 дешифрации, а выходы второго дешифратора 28 через вторые элементы НЕ 29 - с соответствующими выходами блока 5 дешифрации.

В синхронизаторе 6 генератор 30 импульсов соединен выходом с первым выходом синхронизатора 6 и со счетным входом первого счетчика 31, соединенного выходами с вторыми выходами синхронизатора 6.

В логическом блоке 7 первый элемент И 32 соединен входами с вторыми входами логического блока 7, соединенного первым входом с первым входом второго элемента И 34 непосредственно, а через третий элемент НЕ 33 - с первым выходом логического блока 7 и с первым входом третьего элемента И 35, соединенно- то выходом с вторым выходом логического- блока 7, вторым входом - с выходом первого элемента И 32 и с вторым входом второго элемента И 34, соединенного выходом с третьим выходом логического блока 7.

В блоке 8 интегральной оценки четвертый элемент И 36 соединен первым и вторым входами с одноименными входами блока 8 интегральной оценки, выходом - со счетным входом второго счётчика 37, соединенного выходами с выходами блока 8 интегральной оценки, установочным входом с третьим входом блока В интегральной оценки.

Устройство работает следующим образом.

Контролю подлежат параметры например, (температура, влажность и т.д в распределенных в пространстве контролируемых точках. Требуется определить нахождение текущего значения V|j параметров в заданных пределах допуска Vg- V : YX VQ+ У„ , тде УО - среднее значение параметра Vf, - абсолютное допустимое значение отклонения параметра от среднего значения (фиг .2б). Каждая контролируемая точка характеризуется, например, пространственной координатой и значениями нескольких параметров. Значения параметров в каждой из конролируемых точек преобразуются в электрический сигнал,нормализуются и поступают с входов устройства на входы коммутатора 1.. Коммутатор 1 управляется с помощью генератора 30

импульсов и счетчика 31, входящих в состав синхронизатора 6 (фиг.6). Нарастающие во времени двоичные коды поступают с выходов синхронизатора 6 5 на входы коммутатора 1 и управляют последовательным во времени подключением сигналов с контролируемых точек через коммутатор 1 на вход блока 2 сравнения для проверки нахождения

0 параметра в допуске. Сигналы с выходов счетчика 31 в синхронизаторе 6 поступают также на информационные входы дешифраторов 27 и 28 блока 5 дешифрации (фиг.5) и обеспечивают

5 выбор индикатора в матричном блоке 11 индикации по двум координатам, первая из которых (например, номер контролируемой точки) определяется дешифратором 27, а вторая (например,

0 вид параметра) - дешифратором 28 и элементами НЕ 29.

При наличии уровня логической единицы на стробир тощих входах дешиф- 5 раторов 27 и 28, поступающего с выхода блока 3 режима, происходит включение выбранного с помощью дешифраторов 27 и 28 индиктора в матричном блоке 11 иЕЗдикации, а при наличии уровня логического нуля соответствующий индикатор не светится. Значение логического уровня на стробирующих входах дещифраторов 27 и 28 определяется положением переключателя 22 в блоке 3 режима и состоянием выхода блока 2 сравнения (фиг.З). При прямом соединении входа блока 3 с его выходом и наличии уровня логической единицы на выходе блока 2 сравнения соответствующий индикатор в матричном блоке 11 индикации светится, при наличии уровня логического нуля не светится.

Блок 2 сравнения (фиг.2) осуществляет двупороговый допусковый конт- роль нахождения значения параметра, поступающего на его первый вход с выхода коммутатора 1 в случае, если параметр находится в допуске, на выходе блока 2 сравнения формируется сигнал логического нуля, если нет - логической единицы. Значения величин V и V для задания их на блок 2 сравнения формируются в блоке 4 опорных сигналов (фиг.4). 5 Значения V задаются оператором с помощью делителя 24 напряжения по показаниям вольтметра 25 и поступают на точку соединения резисторов

0

5

0

5

0

7

15 и 17 в блоке 2, а значения Vp задаются оператором с помощью делителя 23 напряжения и вольтметра 26 и поступают на точку соединения резисторов 16 и 20 в блоке 2 сравнения.

В результате при показанном на фиг.З положении переключателя 22 на блоке 11 индикации включаются все индикаторы, соответствующие различным контролируемым точкам и их параметрам, вышедшим за пределы допуска. Поскольку опрос.контролируемых точек производится циклично, каждый из индикторов в блоке 11 мерцает, но выбрав частоту работы генератора 30 достаточно большой можно сделать это мерцание незаметным для ч ёловеческого глаза.

Изменяя значения величин V(j и V| с помощью делителей 23 и 24, т.е фактически меняя допуски на отклонение параметра от нормы, можно по показаниям блока 11 индикации оперативно определять параметры пространственно распределенных точек, которые находятся в заданном допуске и которые отсутствуют, т.е.оценивать состояние объекта в целом.

В случае переключения переключатля 22 в блоке 3 сигнал с входа блока 3 проходит на его выход через инвертор 21, что приводит к инвертированию индикации в блоке 11. При этом горят индикаторы блока 11, соответствующие контролируемым точкам, параметры которых находятся в допуске, а не горят индикаторы, соответствующие негодным по параметру контролируемым точкам.

Одновременно с индикацией номеров негодных контролируемых точек и параметров устройство подсчитывае количество контролируемых точек, в которых параметр вышел за пределы допуска. Для этого синхроимпульсы с генератора 30 в синхронизаторе 6 поступают на вход элемента НЕ 33 в блоке 7 и далее на один вход элемента И 36 в блоке 8 интегральной оценки (фиг.8). Через элемент И 36 синхроимпульсы проходят на вход счетчика 37 только при наличии вы- сокого уровня на другом входе элемента И 36, который формируется при нахождении параметра контролируемой точки вне допуска (в приведенном на фиг.З положении переключа050848

теля 22) или при нахождении параметра в допуске (при переключении переключателя 22 из исходного положения). В результате счетчик 37 подсчиты5 вает число контролируемых точек, параметры которых находятся в допуске (или вне допуска). В конце очередного цикла заполнения счетчика 31 в синхронизаторе 6, после опроса всех

10 видов устройства коммутатором 1, счетчик 31 формирует код конца цикла, который выделяется элементом И 32 в логическом блоке 7 (фиг.7), последний высоким уровнем со своего

15 выхода разрешает прохождение синхроимпульса с генератора 30 через элементы И 34 и 35. По переднему фронту синхроимпульса с выхода элемента И 34 выдается строб записи

20 на блок 9 памяти, а по его заднему фронту через элемент И 35 сбрасывается счетчик 37 в блоке

который

подготавливается к следующему циклу работы.

Содержимое блока 9 памяти индицируется блоком 10 индикации, по показаниям которого можно определить количество точек, параметры которых находятся вне допуска (или в допуске) . Изменяя значения V и V с помощью делителей 23 и 24 в блоке 4 можно оперативно отслеживать изменение числа контролируемых точек с параметрами в заданном допуске и оценивать таким образом состояние обт-екта контроля в целом.

Блок 2 сравнения (фиг.2с|) осуществляет двупороговый контроль входного сигнала, поступающего на точку резисторов 14 и 19. Резисторы 13 и 18 обеспечивают деление сигнала V, и величины V для задания их на входы двупорогового компаратора 12. С помощью резисто- ров 15 и 16 на первом инвертирующем входе компаратора 12 формируется сигнал, пропорциональный величине Vg -t- V , который сравнивается с сигналом, пропорциональным V,

поступающим с делителя на резисторах 14 и 13 на первый инвертирующий вход компаратора 12. Резисторы 19 и 20 обеспечивают формирование сигнала, пропорционального Vy- V на втором инвертирующем входе компаратора 12, который сравнивается с си1- налом, пропорциональным V, формируемым на втором неинвертирующем

входе компаратора 12 V, - V Vy- (Vo+ V,,).

В случае нахождения -параметра Чу в допуске компаратор 12 вырабатывает на выходе уровень логического нуля,

В результате циклического опро- са всех контрольных точек исследуемого объекта в матричном блоке 11 индикации,,; отображаются исчерпыващие данные о его состоянии, представленные, например, в форме многослойной мнемосхемы в виде схемы блоков объекта, на которой одним цветом высвечиваются данные о режимах блоков, другим цветом - о параметрах сигналов. Одновременно на блоке 10 индикации отображаются результаты в условных баллах, характеризующие контролируемый объек в целом.

В медицине устройство пригодно для комплексного исследования состояния человеческого организма по заданнь1м типам параметров. В этом случае на многослойной мнемосхеме изображения человека, в которой индикаторы расположены так же, как датчики на теле пациента, отображаются изокривые соответствующего параметра, характеризующие распределение этого параметра по телу пациента,

В агротехнике устройство может использоваться для контроля за сос- 5 тоянием воздуха и почвы (температура , влажность) в теплицах, интенсивности освещения в них.

В метеорологии устройство позволяет автоматически отобразить

0 изотермы, изобары и т.п. выбранного района, области, края.

Аналогичным образом устройство может быть использовано для контроля состояния машин, аппаратов,

5 плотин, мостов, химического оборудования и многих других объектов.

Таким образом, предлагаемое устройство обеспечивает проведение исследования и комплексного контроля

0 состояния технических и природных объектов, а именно определение адреса контрольных точек, обладающих заданными позитивными или негативными свойствами, оперативное из5 менение в широких пределах границы допусков и определение распределения значений параметров в контролируемом объекте, а также измерение количества контрольных точек, обладаюQ щих заданным свойством и характеризующих качество контролируемого объекта в целом, что расширяет его функциональные возможности.

Г

С1лока 6

±

CSMiKit

ЬгЕ

-{ZP

S

8ыа. Sfloxa 6

На ЯлвкЗ

fnlu.

Btif. бмяа /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров сложных систем | 1985 |

|

SU1394180A1 |

| Устройство для автоматизированного контроля радиоэлектронной аппаратуры | 1988 |

|

SU1589405A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Устройство для контроля импульсных трансформаторов в составе электронных блоков | 1987 |

|

SU1471158A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство индикации формирования печатных строк | 1985 |

|

SU1306732A1 |

| Устройство для функционально-параметрического контроля электронных блоков | 1982 |

|

SU1104520A1 |

Сдлона 2

21

На блок. 5

СН D

25

Р//о „ SACK 2

На блок. 2

Фиг.Ч

Фиг. б

с ffflOKa 6

L

С SKOKO 6

Фиг.7

.5

На SftOK 9

На 5лок В cSpoc

На 5flOK8 син)(р

С 5лока 3 С SAOM 7

7J

Фиг.8

На 5мк 8

ВНИЮШ Заказ 8524/48 Тираж 747 Подписное

Фшшал ШГО Патент,

г, Ужгород, ул. Проектная, 4

| Щелочный самогенерирующийМАгНиТОМЕТР | 1977 |

|

SU796779A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля техни-чЕСКиХ Об'ЕКТОВ | 1979 |

|

SU819757A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-01-15—Публикация

1984-07-04—Подача