САЭ СО 4 4 СП 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Частотный манипулятор | 1980 |

|

SU873450A1 |

| МНОГОЧАСТОТНЫЙ ПРИЕМНИК ДЕЛЬТА-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1993 |

|

RU2090981C1 |

| УСТРОЙСТВО ДЛЯ ФОРМОВАНИЯ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1992 |

|

RU2039414C1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| Формирователь сигналов с частотно-фазовой манипуляцией | 1981 |

|

SU1021013A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Приемник многочастотных сигналов | 1990 |

|

SU1838894A3 |

Изобретение относится к электросвязи и телемеханике и может найти применение при построении систем приема информации в частотном коде в автоматизированных системах сбора, обработки и передачи информации с повышенными требованиями к скорости передачи и обработки информации. Цель изобретения - увеличение скорости приема за счет сокращения времени обработки сигналов. Устр-во содержит избирательные у-ли 1, нуль-органы 2, г-р 3 тактовых импульсов, счетчики 4, 6 и 7, коммутатор 5. В устр-во введены триггер 9, постоянное запоминающее устр-во (ПЗУ) 10 и дополнительный элемент И 11. В данном устр-ве резко сокращается область поиска двоичного кода информации, а следовательно, и время отработки принимаемых сигналов, 2 ил., 1 табл. (Л

Фи.1

Изобретение относится к электросвязи и телемеханике.и может найти применение при построении систем приема информации в частотном коде в ав- томатизированных системах сбора, обработки и передачи информации с по- вьппенными требованиями к скорости передачи и обработки информации.

Цель изобретения - увеличение ско-JQ втором подцикле ведут поиск и иденрости приема за счет сокращения времени обработки сигналов.

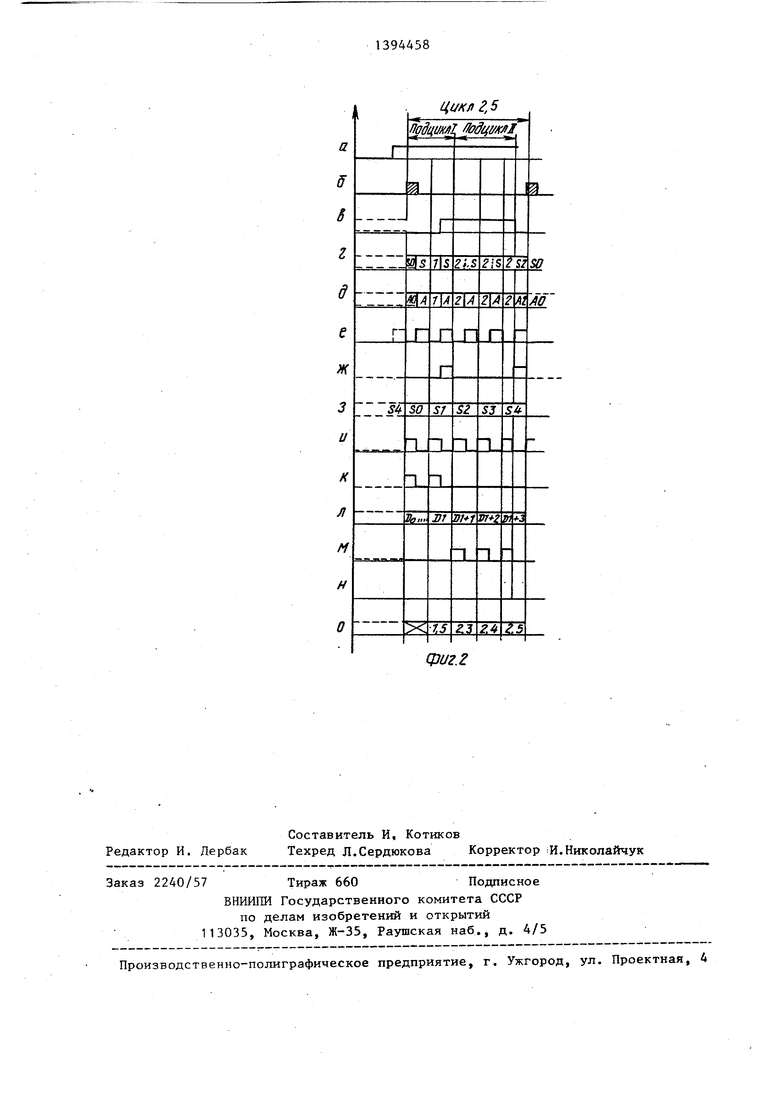

На фиг. I изображена структурная электрическая схема устройства для приема информации в частотном коде; на фиг. 2 - временные диаграммы работы устройства.

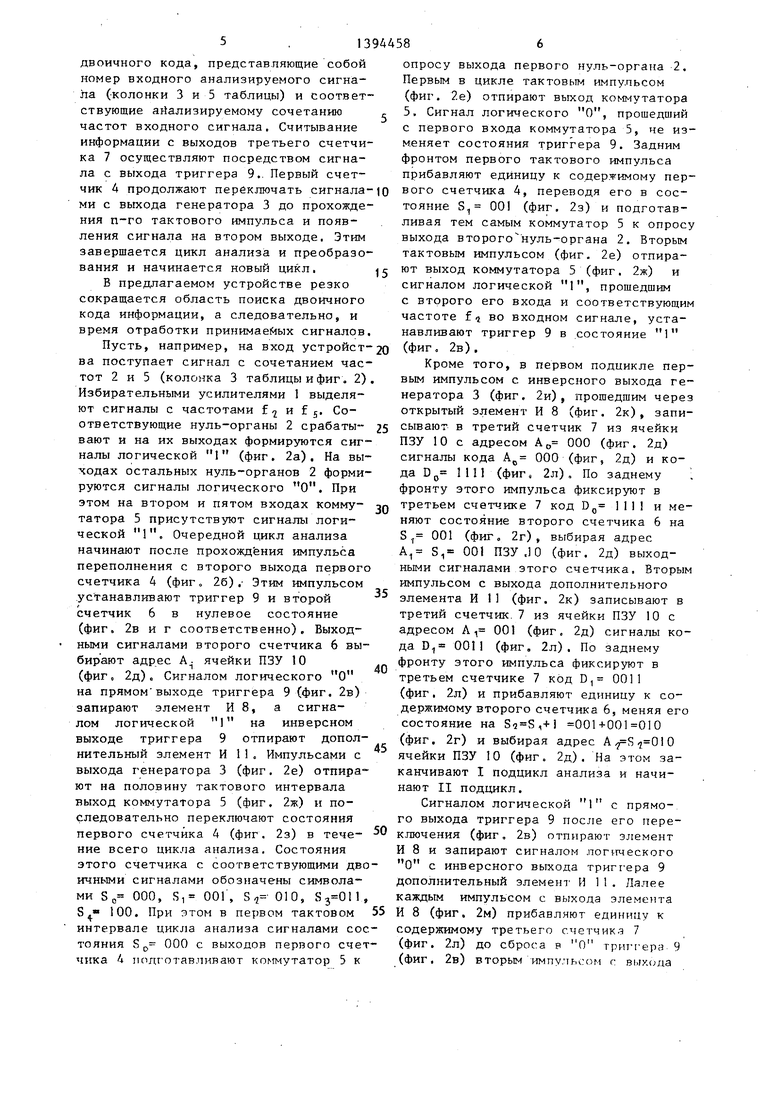

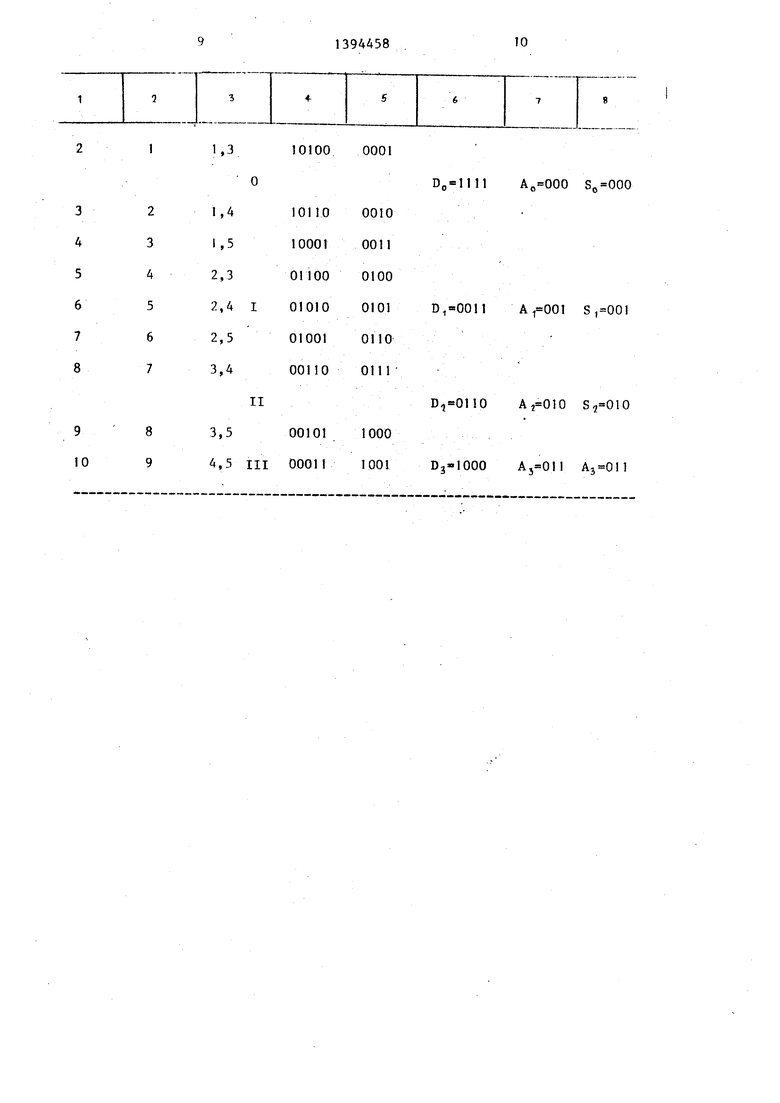

В таблице представлены соответствия входных сигналов состояниям устройства и его отдельных блоков.

Устройство для приема информации в частотном коде содержит избирательные усилители 1, нуль-органы 2, генератор 3 тактовых импульсов (ГТИ),

тификацию второй частоты внутри выбранной в первом подцикле подгруппы (колонки 3-5 таблицы). Во время обработки сигналов частотных комбиt5 наций устройство меняет свои состояния, возможное число которых равно числу разрешенных частотных комбинаций, но устройство необязательно принимает эти все состояния. После появ20 ления на выходе коммутатора 5 второго сигнала логической 1, соответствующего обнаружению второй частоты из комбинации частот входного сигнала, сигналы информации снимают с выходов

первый счетчик 4, коммутатор 5, вто- 25 третьего счетчика 7. Очередной сигнал рой 6 и третий 7 счетчики, элемент И 8, триггер 9, постоянное запоминающее устройство (ПЗУ) 10 и дополнительный элемент И 11.

переполнения первого счетчика 4 с второго выхода возвращает устройство в исходное состояние и подготавливает его к новому циклу работы.

Устройство для приема информации в частотном коде работает следующим образом.

В исходном состоянии счетчики 4 и 6 и триггер 9 находятся в состоянии О, а счетчик 7 - в произвольном состоянии. Состояние других элементо схемы определяется состояниями названных блоков. Это исходное состояние устройства отражено в специальной строке таблицы соответствия состояний, где для примера выбрано количество частот п, применяемых в тракте передачи, равное пяти. Количество раз- регаенных двухчастотных комбинаций кода L равно числу сочетаний по два из п.

Так, например, для п 5 L 10, что и определяет число возможных состоящий устройдтва, а также число строк в таблице соответствия (колонка 1). Анализ входного многочастотного сигнала и принятие решения о наличии той или иной комбинации частот в ней осуществляют избирательными усилителями 1. Дальнейшую обработку сигналов с выходов нуль-органов .2 проводят на высокой тактовой частоте источником которой служит ГТИ 3.

Работу устройства можно разбить на два подцикла, В первом подцикле работы при помощи коммутатора 5 и первого счетчика 4 ведут поиск первой частоты принятой комбинации частот с целью установления подгруппы, к которой относится данная комбинация частот (колонки 3 и 4 таблицы). Во

тификацию второй частоты внутри выбранной в первом подцикле подгруппы (колонки 3-5 таблицы). Во время обработки сигналов частотных комбинаций устройство меняет свои состояния, возможное число которых равно числу разрешенных частотных комбинаций, но устройство необязательно принимает эти все состояния. После появления на выходе коммутатора 5 второго сигнала логической 1, соответствующего обнаружению второй частоты из комбинации частот входного сигнала, сигналы информации снимают с выходов

третьего счетчика 7. Очередной сигнал

переполнения первого счетчика 4 с второго выхода возвращает устройство в исходное состояние и подготавливает его к новому циклу работы.

В колонке 3 таблицы перечислены сочетания частот входного сигнала с указанием на условно разбитые подгруппы частотных комбинаций. Каждое сочетание частот входного сигнала представляют в виде последовательности из п 5 двоичных сигналов на выходе коммутатора 5 за время прохождения п 5 тактовых интервалов ГТИЗ (колонка 4 таблицы).

В колонке 5 таблицы представлены двоичные номера входных сигналов, соответствующие порядковым номерам входных сигналов и возможньм состояниям устройства (колонка 2). В строках колонки 6 таблицы представлены коды, записанные в ячейках ПЗУ 10, где каждой подгруппе частотных комбинаций i (колонка 3) соответствует свой код Dj. Номера А- (адреса) ячеек ПЗУ 10, в которых записаны соответствующие коды D;, представлены в колонке 7. В строках колонки 8 представлены состояния Sj второго счетчика 6 и совпадающие с ним адреса А. в соответствии с порядковыми номерами подгрупп частотных комбинаций (колонка 3 таблицы). Входной сигнал с разрешенным сочетанием двух частот через избирательные усилители посту

пает на нуль-органы 2. При этом на выходах двух нуль-органов 2 появляются сигналы откликов на соответствующие частоты.

Сигналами генератора 3 переключают первый счетчик 4, изменяя значени сигналов на его выходах, и отпирают на часть каждого тактового периода выход коммутатора 5. Посредством этих сигналов выбирают текущий адрес входа Коммутатора 5. Сигнал с соответствующего входа коммутатора 5 поступает на его выход, если на стро

бирующем входе присутствует отпира- 15 состояния второго счетчика 6 (колонющий логический уровень. Цикл анализа входного сигнала в устройстве состоит из п тактов. По окончании каждого цикла на втором выходе пер- вого счетчика 4 получают импульс переполнения, которым устанавливают триггер 9 и второй счетчик 6 в исход- ные состояния. Таким образом к началу очередного цикла анализа первый 4 и второй 6 счетчики и триггер 9 находятся в состоянии логического О, При этом сигналом логического О на прямом выходе триггера 9 запирают элемент И 8.

Сигналом логической 1 с ного выхода триггера 9 отпирают дополнительный элемент И 11, при этом импульсы с выхода генератора-3 поступают на установочный вход третьего счетчика 7 и на счетный вход второго счетчика 6.

Сигналами с выходов второго счетчика 6 S. выбирают номер А ячейки ПЗУ 10, в которой хранится двоичный код D- , равный первому коду В - соответствующей подгруппы кодовых колебаний минус единица (колонки 5и 6 таблицы) . В рассматриваемом примере в ячейке ПЗУ 10 с нулевым адресом (А(| . 000, колонка 7) записан код Dg, равный 1-й кодовой комбинации (колонка 5) подгруппы О минус единица, а именно D 0000-0001 1111. В ячейке ПЗУ 10с 1-м адресом ()

ка 8) и смену выбираемых адресов ПЗУ (колонка 7). Первым сигналом логической 1, обнаруженным на текущем опрошенном входе коммутатора 5 и пе- 20 реданным на его выход, переключают триггер 9. Таким образом.происходит идентификация номера подгруппы, которой принадлежит сочетание частот входного сигнала (колонка 3 таблицы). 25 При этом сигналом логического О с инверсного выхода триггера 9 запрещают прохождение импульсов генерато- :ра 3 через дополнительный элемент И 11 и прекращают переключение-второ- инверс- 30 го счетчика б, а также фиксируют в

третьем счетчике 7 последнюю записан-, ную из ячеек ПЗУ 10-кодовую комбина- нацию DJ ,

Сигнал логической 1 с прямого выхода триггера 9 разрешает прохождение импульсов генератора 3 через элементы И 8 на счетный вход третьего счетчика 7. После переключения триггера 9 и окончания текущего тактового импульса на выходе генератора 3 сигналом с его инверсного выхода, .прошедшим через открытый элемент И 8, прибавляют единицу к содержимому третьего счетчика 7. Полученный в третьем счетчике.7 код представляет собой первую кодовую комбинацию в анализируемой подгруппе (таблица) и соответствует первому сочетанию частот входного сигнала в этой подгруппе.

35

40

45

записан код D. , равный 1-й кодовой . « Поступление импульсов генератора 3 комбинации подгруппы 1 минус единица, а именно D ,01005-0001 j:

0011, В 3.

В последней ячейке ПЗУ, которых всего п-1, записан код 1-й кодовой комбинации последней подгруппы минус единица. В рассматриваемом примере это будет код D, равный первой и единственной кодовой комбинации Вд

55

через открытый элемент И 8 на счетный вход третьего счетчика 7 продолжается до появления второй логической 1 на выходе коммутатора 5, соответству-.. ющей 2-й частоте из комбинации входного сигнала. Этим сигналом сбрасывают триггер 9 в состояние О. На выходе третьего счетчика 7 присутствуют искомые сигналы информации в виде

10012 подгруппы III минус единица, а именно 0 .

Если при пошаговом (потактовом) переключении коммутатора 5 на соответствующих его опрошенных входах обнаруживают сигналы логического О, то триггер 9 остается в исходном состоянии. При этом сигналами с выхода открытого дополнительного элемента И 11 осуществляют поочередную запись кодов DJ из ячеек ПЗУ 10, где ,.., ...,(п-2) (колонка 6 таблицы), в третий счетчик 7, а также переключение

Поступление импульсов генератора 3

через открытый элемент И 8 на счетный вход третьего счетчика 7 продолжается до появления второй логической 1 на выходе коммутатора 5, соответству-.. ющей 2-й частоте из комбинации входного сигнала. Этим сигналом сбрасывают триггер 9 в состояние О. На выходе третьего счетчика 7 присутствуют искомые сигналы информации в виде

двоичного кода, представляющие собой номер входного анализируемого сигна.- ла (колонки 3 и 5 таблицы) и соответствующие айализируемому сочетанию частот входного сигнала. Считывание информации с выходов третьего счетчика 7 осуществляют посредством сигнала с выхода триггера 9.. Первый счетчик А продолжают переключать сигналами с выхода генератора 3 до прохождения п-го тактового импульса и появления сигнала на втором выходе. Этим завершается цикл анализа и преобразования и начинается новый цикл,

В предлагаемом устройстве резко сокращается область поиска двоичного кода информации, а следовательно, и время отработки принимае 1х сигналов.

Пусть, например, на вход устройст-20 (Фиг, 2в),

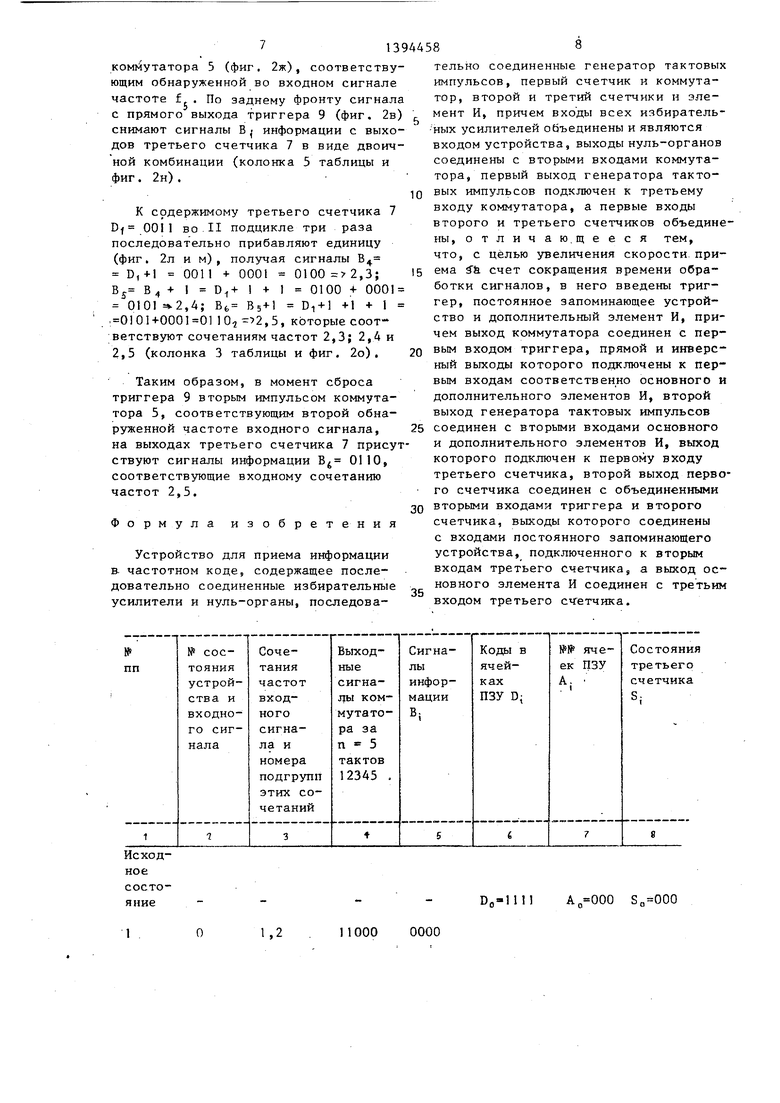

ва поступает сигнал с сочетанием час тот 2 и 5 (колонка 3 таблицы и фиг, 2) Избирательными усилителями 1 выделяют сигналы с частотами f и 5. Соответствующие нуль-органы 2 срабаты- вают и на их выходах формируются сигналы логической 1 (фиг, 2а), На выходах остальных нуль-органов 2 формируются сигналы логического О. При этом на втором и пятом входах коммутатора 5 присутствуют сигналы логической 1. Очередной цикл анализа начинают после прохождения импульса переполнения с второго выхода первого счетчика 4 (фиг. 26).- Этим импульсом устанавливают триггер 9 и второй счетчик 6 в нулевое состояние (фиг. 2в и г соответственно). Выходными сигналами второго счетчика 6 выбирают адрес А. ячейки ПЗУ 10 (фиг 2д)о Сигналом логического О на прямом выходе триггера 9 (фиг. 2в) запирают элемент И 8, а сигналом логической 1 на инверсном выходе триггера 9 отпирают дополнительный элемент И 1. Импульсами с выхода генератора 3 (фиг. 2е) отпирают на половину тактового интервала выход коммутатора 5 (фиг. 2ж) и последовательно переключают состояния первого счетчика 4 (фиг. 2з) в течение всего цикла анализа. Состояния этого счетчика с соответствующими двоичными сигналами обозначены символами So 000, Si 001, s-2- 010, ,

S « 100. При этом в первом тактовом интервале цикла анализа сигналами состояния S (j 000 с выходов первого счетчика 4 подготавливают коммутатор 5 к

5

опросу выхода первого нуль-органа 2. Первым в цикле тактовым импульсом (фиг. .е) отпирают выход коммутатора 5. Сигнал логического О, прошедший с первого входа коммутатора 5, не изменяет состояния триггера 9. Задним фронтом первого тактового импульса прибавляют единицу к содержимому первого счетчика 4, переводя его в состояние S 00 (фиг. 2з) и подготавливая тем самым коммутатор 5 к опросу выхода второго нуль-органа 2. Вторым тактовым импульсом (фиг. 2е) отпирают выход коммутатора 5 (фиг, 2ж) и сигналом логической I, прошедшим с второго его входа и соответствующим частоте f. ч во входном сигнале, устанавливают триггер 9 в состояние 1

0

5

5 50

5

0

Кроме того, в первом подцикле первым импульсом с инверсного выхода генератора 3 (фиг, 2и), прошедшим через открытый элемент И 8 (фиг. 2к), записывают в третий счетчик 7 из ячейки ПЗУ 10 с адресом АО 000 (фиг. 2д) сигналы кода A 000 (фиг, 2д) и кода Dp 1111 (фиг, 2л), По заднему . фронту этого импульса фиксируют в третьем счетчике 7 код 0 1I и меняют состояние второго счетчика 6 на S , 001 (фиг« 2г), выбирая адрес А, 8, 001 ПЗУ.10 (фиг. 2д) выходными сигналами этого счетчика. Вторым импульсом с выхода дополнительного элемента И П (фиг, 2к) записывают в третий счетчик. 7 из ячейки ПЗУ 10 с адресом А i 001 (фиг, 2д) сигналы кода D, ООП (фиг. 2л). По заднему фронту этого импульса фиксируют в третьем счетчике 7 код D, ООП (фиг, 2л) и прибавляют единицу к содержимому второго счетчика 6, меняя его состояние на ,+i 001+001 010 (фиг, 2г) и выбирая адрес ячейки ПЗУ 10 (фиг. 2д). На этом заканчивают I подцикл анализа и начинают II подцикл,

Сигналом логической 1 с прямого выхода триггера 9 после его переключения (фиг, 2в) отпирают элемент И 8 и запирают сигналом логического О с инверсного выхода тригг ера 9 дополнительный элемент И 11. Лалее каждым импульсом с выхода элемента И 8 (фиг, 2м) прибавляют единицу к содержимому третьего счетчика 7 (фиг, 2л) до сброса Р О трип-ера 9

(фиг, 2в) вторым импульсом г .(Л1а

ком 1утатора 5 (фиг, 2ж), соответствующим обнаруженной во входном сигнале частоте f . По заднему фронту сигнала с прямого выхода триггера 9 (фиг. 2в) снимают сигналы В , информации с выходов третьего счетчика 7 в виде двоичной комбинации (колонка 5 таблицы и фиг. 2н).

К содержимому третьего счетчика 7 Df 0011 во II подцикле три раза последовательно прибавляют единицу (фиг, 2л им), получая сигналы В D,-H ООП + 0001 0100: :72,3; Bj В + 1 + 1 0100 + 0001 0101.2,А; Bfc BS+I Di + l +1+1 ,0101+0001 01 10,-72,5, которые соответствуют сочетаниям частот 2,3; 2,4 и 2,5 (колонка 3 таблицы и фиг, 2о).

Таким образом, в момент сброса триггера 9 вторым импульсом коммутатора 5, соответствующим второй обнаруженной частоте входного сигнала, на выходах третьего счетчика 7 присутствуют сигналы информации В 0110, соответствующие входному сочетанию частот 2,5.

Формула изобретения

Устройство для приема информации в. частотном коде, содержащее последовательно соединенные избирательные усилители и нуль-органы, последова1,2

11000

тельно соединенные генератор тактовых импульсов, первый счетчик и коммутатор, второй и третий счетчики и элемент И, причем входы всех избиратель- ных усилителей объединены и являются входом устройства, выходы нуль-органов соединены с вторыми входами коммутатора, первый выход генератора тактоQ вых импульсов подключен к третьему входу коммутатора, а первые входы второго и третьего счетчиков объединены, отличаю.щееся тем, что, с целью увеличения скорости при5 ема S k счет сокращения времени обработки сигналов, в него введены триггер, постоянное запоминающее устройство и дополнительный элемент И, причем выход коммутатора соединен с перQ вым входом триггера, прямой и инверсный выходы которого подключены к первым входам соответственно основного и дополнительного элементов И, второй выход генератора тактовых импульсов

5 соединен с вторыми входами основного и дополнительного элементов И, выход которого подключен к первому входу третьего счетчика, второй выход первого счетчика соединен с объединенными

0 вторыми входами триггера и второго счетчика, выходы которого соединены с входами постоянного запоминающего устройства, подключенного к вторым входам третьего счетчика, а выход основного элемента И соединен с третьим

5

входом третьего счгетчика.

0000

фиг. г

| Устройство для приема информации в частотном коде | 1983 |

|

SU1185642A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-07—Публикация

1986-12-02—Подача