Изобретение относится к радиотехнике и может быть использовано в радиосвязи, радиолокации, радионавигации и радиоуправлении для получения сигналов с фазовой и частотной модуляцией.

Известен формирователь сигналов с частотно-фазовой манипуляцией, содер жащий последовательно соединенные певый коммутатор, первый и второй входы которого соединены с выходами соответственно первого и второго опорного генератора, и делитель частоты, а также фил.ьтр нижних частот, при этом управляющий вход первого коммутатора является первым входом инфо1эмационного сигнала формирователя сигналов с частотно-фазовой манипуляцией О ) .

Однако в в|ыходном сигнале известного формирователя сигналов с частотно-фазовой манипуляцией относительно высок уровень паразитных составляющих, для уменьшения которого требуется применение фильтра с высокой крутизной среза, так как паразитные спектральные составляющие находятся близко к полезным, при это в фильтре, в свою очередь, появляются динамические искажения.

Кроме того, в известном формирователе сигналов с частотно-фазовой манипуляцией нельзя получить сигнал с фазовой манипуляцией, отличной от 180.

Цель изобретения - уменьшение паразитных составляющих в спектре выходных сигналов при одновременном увеличении числа градаций скачка фазы.

Указанная цель достигается тем, что в формирователь сигналов с частотно-фазовой манипуляцией, содержащий последовательно соединенные первый коммутатор, первые и второй входы которого соединены с выходами соответственно первого и второго опорного генератора, и делитель частоты, а также фильтр нижних частот, при этом управляющий вход первого коммутатора является первым входом информационного сигнала формирователя сигналов с частотно-фазовой манипуляцией, между выходом первого коммутатора и входом фильтра нижних частот введены последовательно соединенные первый счетчик, второй коммутатор, второй сметчик, третий коммутатор, постоянное запоминающее устройство

и цифро-аналоговый преобразователь, между выходом делителя частоты и вторым входом второго коммутатора введен триггер, между выходом первого счетчика и вторым входом триггера введен блок сравнения кодов, между выходами второго счетчика и вторыми входами третьего коммутатора введен сумматор, вторые входы блока сравнения кодов и вторые входы двоичного сумматора соединены соответственно с выходами младших разрядов и выходами старших разрядов введенного датчика кодов, при этом установочный

5 вход делителя:-частоты соединен с выходом блока сравнения кодов, выход . второго коммутатора соединен с входом синхронизации цифро-аналогового преобразователя, а управляющие входы

0 второго и третьего коммутаторов соединены между собой, и точка их соединения является вторым входом информационного сигнала формирователя сигналов с частотно-фазовой манипуляцией.

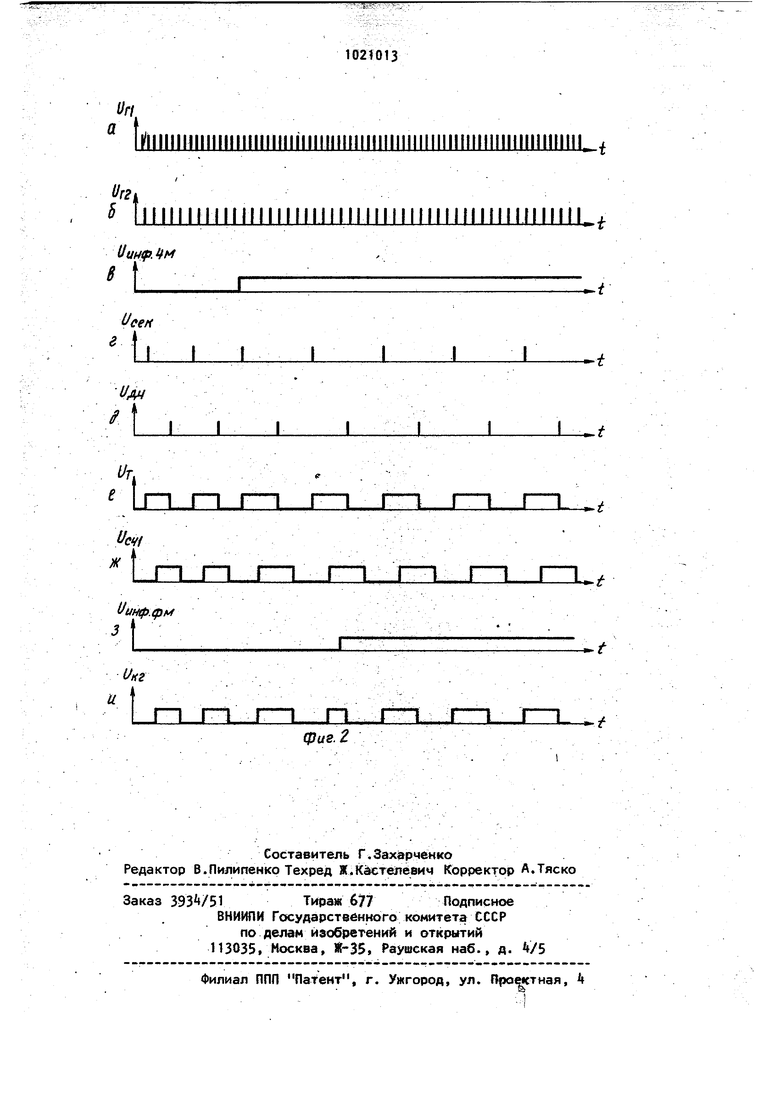

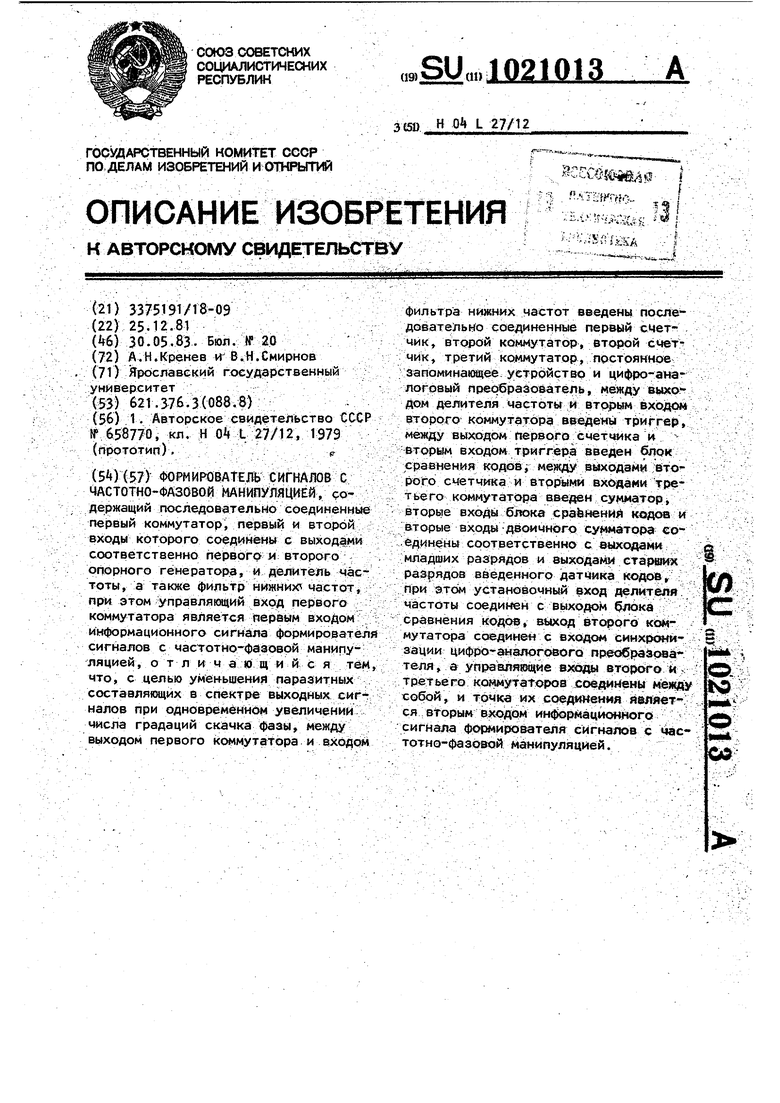

На фиг,1 представлена структурная электрическая схема предлагаемого формирователя сигналов с частотнофазовой манипуляцией; на фиг.2 - временные диаграммы его работы.

0

Формирователь содержит первый и второй опорные генераторы 1 и 2, первый коммутатор 3, делитель t частоты, первый счетчик 5, блок 6 сравнения кодов, триггер 7, второй коммутатор

5 8, второй счетчик 9, третий .коммутатор 10, постоянное запоминающее устройство (ПЗУ) 11, цифро-аналоговый преобразователь (ЦАП) 12, фильтр 13 нижних частот (ФНЧ) , двоичный

О сумматор Н, датчик 15 кодов.

Формирователь сигналов с частотног фазовой манипуляцией работает следующим образом.

Выходные сигналы опорных генера5торов 1 и 2, представляющие собой импульсные последовательности с частотой повторения импульсов f-.H f(соответственно фиг.2а и б), поступают на вход первого коммутатора 3,

который в зависимости от информационного сигнала частотной манипуляции на его управляющем входе пропускает либо последовательность импульсов с опорного генератора 1 - при информационном сигнале, равном логическому О (фиг,2в), либо с опорного генератора 2 - при логической 1. Выходное напряжение первого коммутатора 3 поступает на вход п-разрядног первого счетчика 5 и делителя k частоты на . Выходной сигнал первого счетчика 5, представляющий собой текущее значение двоичного кода, подается на первый вход блока 6 сравнения кодов, на другой вход которого подается код скачка с младших разрядов датчика 15 кодов. Последний может представлять собой, например, набор тумблеров, с помощью которых может быть выставлен напряжение логического нуля или единицы на соответствующих разрядах. Выходной сигнал блока 6 сравнения кодов (фиг.2г), являющийся последовательностью импульсов с частотой следования или f2/2 в зависимости от значения информационного .сигнала частотной манипуляции (ЧМ) и появляющийся при совпадений кодов на его входах, подается на второй вход триггер 7 и записывает (устанав ливает) в него единицу, а также устанавливает в исходное состояние делитель k частоты. Делитель k часто ты представляет собой устройство, которое пропускает импульс, поступающий на его вход. Выходной сигналделителя k частоты (фиг.2д) поступает на первый вход триггера 7 и записывает (устанавливает) в него нуль. Сигнал с выхода триггера 7 (фиг.2е), представляющий собой напряжение типа меандр подается на вход второго коммутатора 8, на другой вход которого поступает сигнал с выхода старшего разряда первого счетчика 5 (фиг,2ж), тоже представляющий собой напряжение типа меанд Частоты следования обоих сигналов на входах второго коммутатора 8 равны f2/2, но сдвинуты величину -ГГг А:т(2)/2, где Т(2) (2) -|2 а j- состояние младших радрядов датчика 15 кодов. Второй коммутатор 8 пропускает в зависимости от информационного си нала фазовой манипуляции (ФМ) (фиг.2 поданного на его управляющий вход, либо последовательное ;ь импульсов с выхода старшего разряда первого сче чика 5 - при информационном сигнале ФМ, равном логическому О, либо с выхода триггера 7 - при логической 1 (фиг.2и). Импульсная последовательность с выхода второго коммутатора 8 подается на вход к разрядиого второго счетчика 9, который срабатывает по перепаду напряжения из логического нуля в логическую единицу и преобразует поток импульсов в двоич ный код, период повторения которого равен , W ) где к - число старших разрядов датчика 15 кодов. Последовательность кодов с выхода второго счетчика 9 подается на вход третьего коммутатора 10, на другой вход которого поступает код с выхода двоичного сумматора k. Этот код равен сумме кодов с выхода второго счетчика 9 и старших разрядов датчика кодов 15, поданных на соответствующие входы двоичного сумматора Ik. Код с выхода третьего коммутатора 10, равный в зависимости от информационного сигнала ФМ, поданного ма управляющий вход третьего коммутатора 10, либо коду на выходе второго счетчика 9 (информационный сигнал ФН равен ло-ическому нулю) , либо на выходе двоичного сумматора (информационный сигнал ФМ равен логической единице) подается на адресный вход постойного запоминающего устройства 11, таблица истинности которого составлена таким образом, что последовательность кодовых комбинаций адреса выбирает выходную последовательность большей разрядности, значения которой пропорциональны мгновенным значениям амплитуды гармонического сигнала на его периоде. Кодовая комбинация с выхода ПЗУ 11 записывается и с помощью импульса синхронизации по переходу из логической единицы в логический нуль, подаваемому с выхода второго коммутатора 8 в ЦАП 12, где преобразуется в аналоговое напряжение, пропорциональное значению двоичного кода на.входе ЦАП 12. При работе второго счетчика 9 и ЦАП 12 по разным фронтам импульса исключаются сбои за счет задержек сигнала в втором счетчике9, третьем коммутаторе 10, ПЗУ 11, двоичном сумматоре 14 и переходных процессах в них. Выходной сигнал ЦАП 12 подается на вход ФНЧ 13, который отфильтровывает паразитные составляющие в спектре сигнала, лежащие в области частот )- Выходной сигнал ФНЧ 13 представляет собой колебание с частотнофазовой манипуляцией, частота которого равна .

-t(2/2 ..tc

число возможных скачков фазы 2 и дискрет установки скачка фазы . s

Предлагаемый формирователь сигналов с частотно-фазовой манипуляцией позволяет получить ЧМ-ФМ колебания с высокой чистотой спектра (так как паразитные составляющие лежат в 2 раз выше основной частоты и легко фильтруются) и большим числом градаций скачка фазы, что в свою оч редь, при использовании его, например, в системах передачи дисретной информации, приводит к повышению помехоустойчивости этих систем. miiininiiiiiiiiiiiiMiiiiiiiiiHiiiiiiiiiiiiiiiiiniiiiniiMiiniiiiiiL

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Фазовый модулятор | 1986 |

|

SU1388974A2 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТАКТОВОГО КОЛЕБАНИЯ | 1991 |

|

RU2007881C1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

ФОРМИРОВАТЕЛЬ СИГНАЛОВ С ЧАСТОТНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ, содержащий последовательно соединенные первый коммутатор, первый и второй входы которого соединены с выходами соответственно первого и второго опорного генератора, и делитель частоты, а также фильтр нижних частот, при этом управляющий вход первого коммутатора является первым входом информационного сигнала формирователи сигналов с частотно-фазовой манипуляцией, отличающийся тем, что, с целью уменьшения паразитных составляющих в спектре выходных сигналов при одновременном увеличении числа градаций скачка фазы, между выходом первого коммутатора и входом фильтра нижних частот введены последовательно соединенные первый счетчик, второй коммутатор, второй счетчик, третий коммутатор, постоянное запоминакмдее- устройство и цифро-а)налоговый преобразователь, между выходом делителя частоты и вторым входом второго коммутатора введены триггер, между выходом первого счетчика и вторым входом триггера введен блок сравнения кодов между выходами второго счетчика и вторыми входами третьего коммутатснза введен сумматор, вторые входы блока сраЬнений кодов и вторые входы двоичного сумматора соединены соответственно с выходами младших разрядов и выходами старших разрядов введенного датчика кодов, при этом установочный вход делителя частоты соединен с выходом блока сравнения кодов, выход второго коммутатора соединен с входом синхрс тзации цифро-аналогового пре : разова теля, а управлядащие axoyivii второго и третьего коммутаторов соейинены между собой, и точка их являет-. ся вторым входом информационного сигнала фсч мирователя сигна юв с частотно-фазовой манипуляцией. О

фие.2

- . . s

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой частотно-фазовый манипулятор | 1977 |

|

SU658770A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

Авторы

Даты

1983-05-30—Публикация

1981-12-25—Подача