оо

00

сз: о

00

к

Изобретение относится к радионзме- рениям и может быть использовано для спектрапьного анализа низкочастотных сигналов.

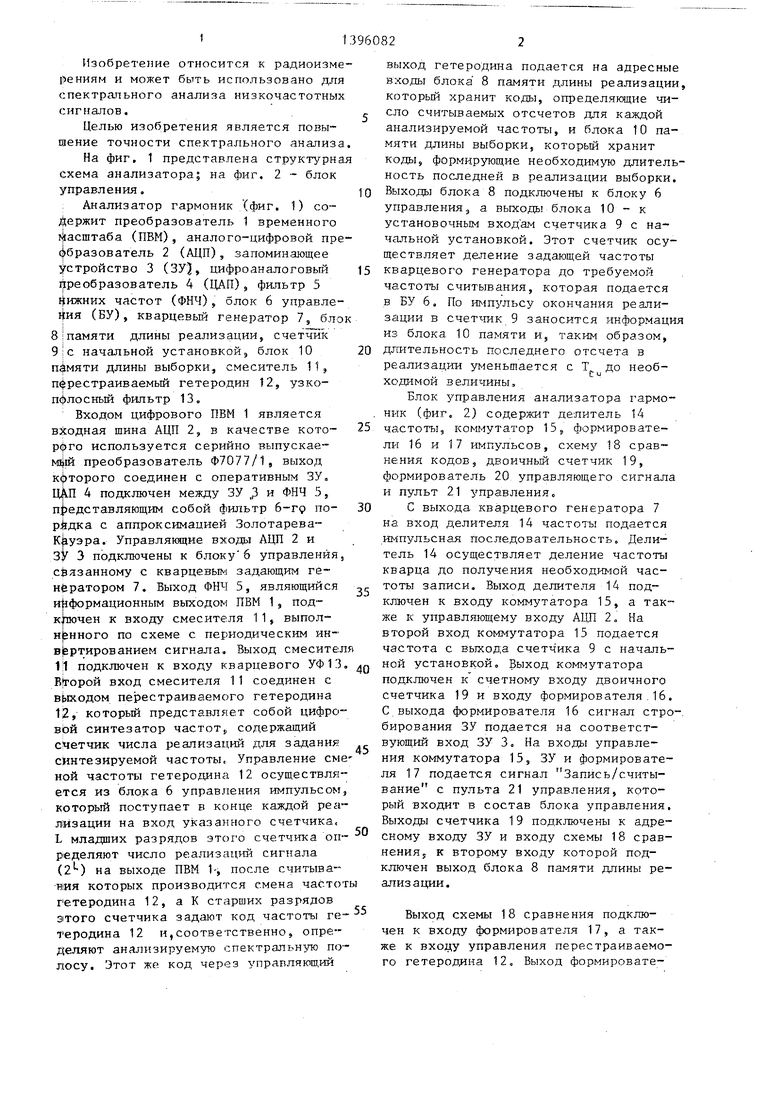

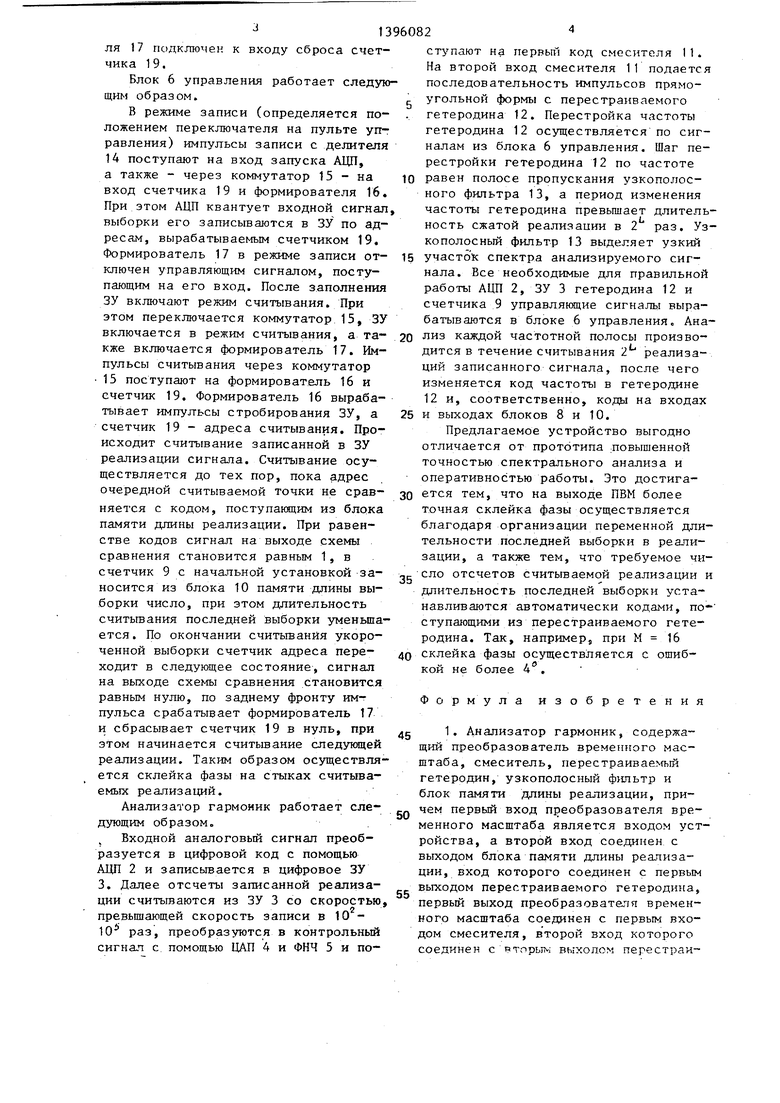

Целью изобретения является повышение точности спектрального анализа. На фиг. 1 представлена структурнал схема анализатора; на фиг. 2 - блок управления.

: Анализатор гармоник (фиг. 1) содержит преобразователь 1 временного |1асштаба (ПВМ), аналого-цифровой пре- фбразователь 2 (АЦП), запоминающее устройство 3 (ЗУ5, цифроаналоговый т реобразователь 4 (ЦАИ) , фильтр 5 |ижних частот (ФНЧ), блок 6 управле- 1|ия (БУ), кварцевый генератор У, блок :памяти длины реализации, счетчик |С начальной установкойj блок 10

пфмяти длины выборки, смеситель 11, перестраиваемый гетеродин 12, узко- пфлосный фильтр 13.

Входом цифрового ПВМ 1 является входная шина АЦП 2, в качестве кото- рфго используется серийно выпускав- MiJKi преобразователь Ф7077/1, выход которого соединен с оперативным ЗУ. 4 подключен между ЗУ „3 и ФНЧ 5, представляющим собой фильтр б-гд по- с аппроксимацией Золотарева- Кйуэра. Управляющие входы АЦП 2 и ЗУ 3 подключены к блоку 6 управления, связанному с кварцевым задающим генератором 7. Выход ФНЧ 5, являющийся и|1формационным выходом ПВМ 1 , под- кЬючен к входу смесителя 11, выпол- н нного по схеме с периодическим инвертированием сигнала. Выход смесител 11 подключен к входу кварцевого УФ 13, Второй вход смесителя 11 соединен с вЬкодом пе естраиваемого гетеродина 1(2,- который представляет собой цифровой синтезатор частот,, содержащий сйетчик числа реализаций для задания синтезируемой частоты. Управление сме ной частоты гетеродина 12 осуществляется из блока 6 управления импульсом,, который поступает в конце каждой реализации на вход указанного счетчика L младших разрядов этого счетчика оц р вделяют число реализаций сигнала () на выходе ПВМ 1-, после счнтыва- которых производится с.мена час-тот гетеродина 12, а К старших разрядов этого счетчика задают код частоты ге теродина 12 и,соответственно, определяют анатшзируемую спектральную полосу. Этот же код через управляющий

т..

15

20

25

30

35

Q

0

5

выход гетеродина подается на адресные входы блока 8 памяти длины реализации, который хранит коды, определяющие число считываемых отсчетов для каждой анализируемой частоты, и блока 10 памяти длины выборки, который хранит коды, формирующие необходимую длительность последней в реализации выборки. Выходы блока 8 подключены к блоку 6 управления 3 а выходы блока 10 - к установочным вход ам счетчика 9 с начальной установкой. Этот счетчик осуществляет деление задающей частоты кварцевого генератора до требуемой частоты считывания, которая подается в БУ 6. По импульсу окончания реализации в счетчик 9 заносится информация из блока 10 памяти и, таким образом, длительность последнего отсчета в реализации уменьшается с Т до необходимой величины.

Блок управления анализатора гармоник (фиг, 2} содержит делитель 14 частоты, коммутатор 15,, формирователи 16 и 17 импульсов, схему 18 сравнения кодов, двоичньй счетчик 19, формирователь 20 управляющего сигнала и пульт 21 з правления.

С выхода кварцевого генератора 7 на вход делителя 14 частоты подается импульсная последовательность. Делитель 14 осуществляет деление частоты кварца до получения необходимой частоты записи. Выход делителя 14 подключен к входу коммутатора 15, а также к управляющему входу АЦП 2„ На второй вход коммутатора 15 подается частота с выхода счетчика 9 с начальной установкой. Выход коммутатора подключен к счетному входу двоичного счетчика 19 и входу формирователя.16. С выхода формирователя 16 сигнал стро-, бирования ЗУ подается на соответствующий вход ЗУ 3, На входы управления коммутатора 15, ЗУ и формирователя 1 7 подается сигнал Запись/считывание с пульта 21 управления, который входит в состав блока управления. Выходы счетчика 19 подключены к адресному входу ЗУ и входу схемы 18 сравнения j к второму входу которой подключен выход блока 8 памяти длины ре- ализ ации.

Выход схемы 18 сравнения подключен к входу формирователя 17, а также к входу управления перестраиваемого гетеродина 12, Выход формирователя 17 подключен к входу сброса счетчика 19.

Блок 6 управления работает следующим образом.

В режиме записи (определяется положением переключателя на пульте управления) импульсы записи с делителя 14 поступают на вход запуска АЦП, а также - через коммутатор 15 - на вход счетчика 19 и формирователя 16. При этом АЦП квантует входной сигнал выборки его записываются в ЗУ по адресам, вырабатываемым счетчиком 19. Формирователь 17 в режиме записи отключен управляющим сигналом, поступающим на его вход. После заполнения ЗУ включают режим считывания. При этом переключается коммутатор 15, ЗУ включается в режим считывания, а также включается формирователь 17. Импульсы считывания через коммутатор 15 поступают на формирователь 16 и счетчик 19. Формирователь 16 вырабатывает импул-ьсы стробирования ЗУ, а счетчик 19 - адреса считывания. Происходит считывание записанной в ЗУ реализации сигнала. Считывание осуществляется до тех пор, пока адрес очередной считываемой точки не сравняется с кодом, поступаняцим из блока памяти длины реализации. При равенстве кодов сигнал на выходе схемы сравнения становится равным 1, в счетчик 9 с начальной установкой заносится из блока 10 памяти длины выборки число, при этом длительность считьшания последней выборки уменьшается. По окончании считьтанйя укороченной выборки счетчик адреса переходит в следующее состояние, сигнал на выходе схемы сравнения становится равным нулю, по заднему фронту импульса срабатывает формирователь 17 и сбрасывает счетчик 19 в нуль, при этом начинается считьшание следующей реализации. Таким образом осуществляется склейка фазы на стыках считываемых реализаций.

Анализатор гармоник работает сле- дзтощин образом.

Входной аналоговый сигнал преобразуется в цифровой код с помощью АЦП 2 и записывается в цифровое ЗУ 3. Далее отсчеты записанной реализации считьгааются из ЗУ 3 со скоростью превышающей скорость записи в 10 - 10 раз, преобразуются в контрольный сигнал с помощью ЦАП 4 и ФНЧ 5 и поступают на первьш код смесителя I1. На второй вход смесителя 11 подается последовательность импульсов прямо- g угольной формы с перестраиваемого гетеродина 12. Перестройка частоты гетеродина 12 осуществляется по сигналам из блока 6 управления. Шаг перестройки гетеродина 12 по частоте

0 равен полосе пропускания узкополосного фильтра 13, а период изменения частоты гетеродина превьпиает длительность сжатой реализации в 2 раз. Узкополосный фильтр 13 выделяет узкий

5 участо к спектра анализируемого сигнала. Все необходимые для правильной работы АЦП 2, ЗУ 3 гетеродина 12 и счетчика 9 управляющие сигналы вырабатываются в блоке 6 управления. Ана0 ЛИЗ каждой частотной полосы производится в течение считывания 2 реализаций записанного сигнала, после чего изменяется код частоты в гетеродине 12 и, соответственно, коды на входах

5 и выходах блоков 8 и 10.

Предлагаемое устройство выгодно отличается от прототипа повышенной точностью спектрального анализа и оперативностью работы. Это достига0 ется тем, что на выходе ПВМ более точная склейка фазы осуществляется благодаря организации переменной длительности последней выборки в реализации, а также тем, что требуемое число отсчетов считываемой реализации и длительность последней выборки устанавливаются автоматически кодами, по- ступающими из перестраиваемого гетеродина. Так, например, при М 16

0 склейка фазы осуществляется с ошибкой не более 4,

Формула изобретения

5 1. Анализатор гармоник, содержащий преобразователь временного масштаба, смеситель, перестраивае {ый гетеродин, узкополосный фильтр и блок памяти длины реализации, причем первый вход преобразователя временного масщтаба является входом устройства, а второй вход соединен с выходом блока памяти длины реализации, вход которого соединен с первым выходом перестраиваемого гетероди1са, первый выход преобразователя временного масштаба соединен с первым входом смесителя, второй вход которого соединен с вторыт ; выходом перестраи5

0

5

15

20

лаемого гетеродина, вход которого соединен с вторым выходом преобразователя временного масштаба, выход смесителя соединен с входом уэкопо- лосного фильтра, выход которого является выходом устройства,, отличающийся тем, что, с целью увеличения точности янализа9 в него введены последовательно соединенные ю блок памяти длины выборки и счетчик ;С начальной установкой, выход кото- :рого подключен к третьему входу пре- Ьбразователя временного масштаба, тре- ;тий выход которого соединен с вторым входом счетчика с начальной установ- |кой, третий вход которого соединен |С четвертым выходом преобразователя :временного масштаба, вход блока памяти длины выборки соединен с первьлм |выходом перестраиваемого гетеродина.

2, Анализатор по п. 1, о т л и - чающийс я тем,,, что преобразователь временного масштаба содержит последовательно соед сненные аналого- 25 ;цифровой преобразователь (АЦП), за- |поминакидее устройство, цифроаналого- йый преобразователь, фильтр нижних частот, а также блок управления и кварцевый генератор, причем вход AIUI является первым входом преобразователя временного масштаба, первый и второй выходы блока управления соединены соответственно с управляющим входом аналого-цифрового преобразователя и управляющим входом запоминая - (цего устройства, третий выход блока1 управления является вторым и третям выходами преобразователя временного Масштаба, выход кварцевого генератора является четвертым выходом преоб13960826

разователя временного масштаба и соединен с первым входом блока управле30

35

40

ния, второй и третий входы которого являются соответственно вторым и третьим входами преобразователя временного масштаба.

3. Анализатор по п. 2, отличающийся тем, что блок управления содержит формирователь управляющего сигнала, первый и второй формирователи импульсов, делитель частоты, коммутатор, -пульт управления, двоичный счетчик, схему сравнения кодов, причем выход пульта управления соединен с первыми входами коммутатора, формирователя управляющего сигнала и первого формирователя импульсов, второй вход которого соединен с выходом схемы сравнения кодов, который является третьим выходом блока управления, первый вход схемы сравнения кодов является вторым входом блока управления, второй вход которой объединен с вторым входом формирователя управляющего сигнала и .,соединен с выходом двоичного счетчика, первый вход которого соединен с выходом первого формирователя импульсов, а второй вход объединен с выходом коммутатора через второй формирователь импульсов и соединен с третьим входом формирователя управляющего сигнала, выход которого является вторым выходом блока управления, второй вход коммутатора является третьим входом блока управления, а третий вход соединен с выходом делителя частоты, который является первым выходом блока управления, вход делителя частоты является первым входом блока управления

5

0

5

0

5

0

ния, второй и третий входы которого являются соответственно вторым и третьим входами преобразователя временного масштаба.

3. Анализатор по п. 2, отличающийся тем, что блок управления содержит формирователь управляющего сигнала, первый и второй формирователи импульсов, делитель частоты, коммутатор, -пульт управления, двоичный счетчик, схему сравнения кодов, причем выход пульта управления соединен с первыми входами коммутатора, формирователя управляющего сигнала и первого формирователя импульсов, второй вход которого соединен с выходом схемы сравнения кодов, который является третьим выходом блока управления, первый вход схемы сравнения кодов является вторым входом блока управления, второй вход которой объединен с вторым входом формирователя управляющего сигнала и .,соединен с выходом двоичного счетчика, первый вход которого соединен с выходом первого формирователя импульсов, а второй вход объединен с выходом коммутатора через второй формирователь импульсов и соединен с третьим входом формирователя управляющего сигнала, выход которого является вторым выходом блока управления, второй вход коммутатора является третьим входом блока управления, а третий вход соединен с выходом делителя частоты, который является первым выходом блока управления, вход делителя частоты является первым входом блока управления

КАЦП(2)

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометр | 1985 |

|

SU1298685A1 |

| ДОПЛЕРОВСКИЙ ИЗМЕРИТЕЛЬ СОСТАВЛЯЮЩИХ ВЕКТОРА СКОРОСТИ, ВЫСОТЫ И МЕСТНОЙ ВЕРТИКАЛИ ДЛЯ ВЕРТОЛЕТОВ И КОСМИЧЕСКИХ АППАРАТОВ ВЕРТИКАЛЬНОЙ ПОСАДКИ | 1995 |

|

RU2083998C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2027315C1 |

| Цветная телевизионная камера | 1984 |

|

SU1233301A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ СБОРОЧНЫМ УСТРОЙСТВОМ | 1991 |

|

RU2029335C1 |

Изобретение может быть использовано для спектрального анализа низкочастотных сильфонов, Цель изобретения - повьшение точности спектрального анализа. Устройство содержит преобразователь 1 временного масштаба, включакяций аналого-цифровой преобразователь 2,запоминающее устройство 3, цифроаналоговый преобразователь 4, фильтр 5 нижних частот, блок 6 управления и кварцевый генератор 7. Кроме того, анализатор гармоник содержит блок 8 памяти длины реализации, смеситель 11, перестраиваемый гетеродин 12 и узкополосный фильтр 13. Введение блока 10 памяти длины выборки, счетчика 9 с начальной установкой и образование новых функциональных связей позволяет получить на выходе преобразователя 1 временного масштаба бол ее точную склейку фазы. Это осуществляется благодаря организации переменной длительности последней выборки вреализации. При этом требуемое число отсчетов считываемой реализации и длительность последней выборки устанавливаются автоматически кодами, поступающими из перестраиваемого гетеродина блока 6 управления. В описании предложен пример реализации блока 6 управления. 2 з.п. ф-лы, 2 ил. Ф (Л

от КГ(7}

Фиг.

От5ПДР(8)

| Анализатор спектра | 1974 |

|

SU513324A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Анализатор гармоник с транспониро-ВАНиЕМ | 1979 |

|

SU836602A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-05-15—Публикация

1986-03-25—Подача