/J

00

со

О5

к

оо

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для расширения системы оснований модулярного кода | 1985 |

|

SU1282134A1 |

| Система надежного облачного хранения с регулируемой избыточностью данных | 2021 |

|

RU2782681C1 |

| Система распределенного хранения данных | 2021 |

|

RU2780148C1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ НА ОСНОВЕ ИНТЕРВАЛЬНО-ПОЗИЦИОННЫХ ХАРАКТЕРИСТИК | 2014 |

|

RU2557444C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| Устройство коррекции ошибок в модулярном коде на основе расширения системы оснований | 2017 |

|

RU2652446C1 |

| Устройство для сравнения чисел в системе остаточных классов | 2018 |

|

RU2698413C1 |

| Устройство для декодирования модулярного кода | 1987 |

|

SU1411980A1 |

| Устройство для обнаружения ошибок в модулярном коде | 1985 |

|

SU1295528A1 |

| Устройство для вычисления позиционной характеристики непозиционного кода | 1986 |

|

SU1324116A1 |

Изобретение относится к области вычислительной техники и может быть использовано для контроля в вычислительных устройствах, функционирую ----. пшх в системе остаточных классовj а также для обнаружения ошибок в системах передачи информации, представленной модулярными кодами. Целью изобретения является уменьшение аппаратурных затрат. Поставленная цель достигается тем, что устройство для обнаружения ошибок в двухступенчатом модулярном коде, содержащее блок 4 памяти, блок 5 вьшисления позиционной характеристики, две схемы 8,9 сравнения с константой и элемент ИЛИ 10, содержит демультиплексор 3, . блок 6 вычисления квазиранга числа и схему 7 сравнения с соответствующими связями. 2 з.п. ф-лы, 3 ил.

fpuz-l

Изобретение относится к вьмисли- тельной технике и может быть использовано для контроля в вычислительных устройствах,функционирующих в системе остаточных классов, а также в сие темах передачи информации, представленной модулярными кодами.

Целью изобретения является уменьшение аппаратурных затрат.

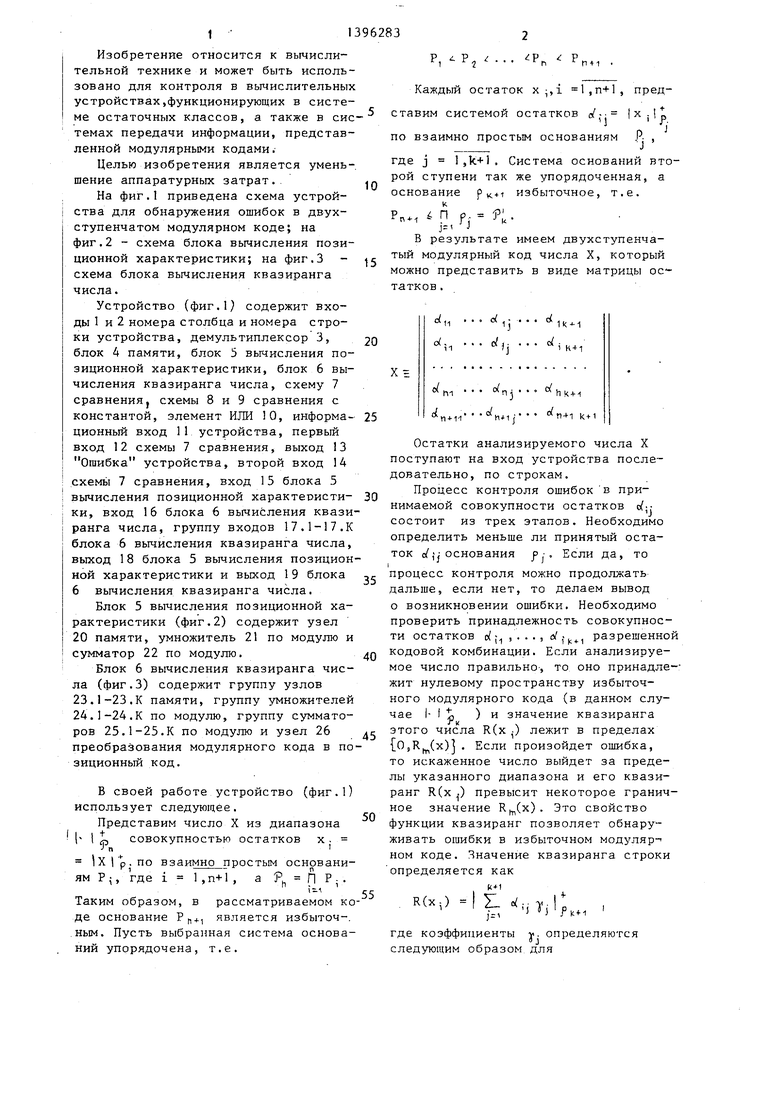

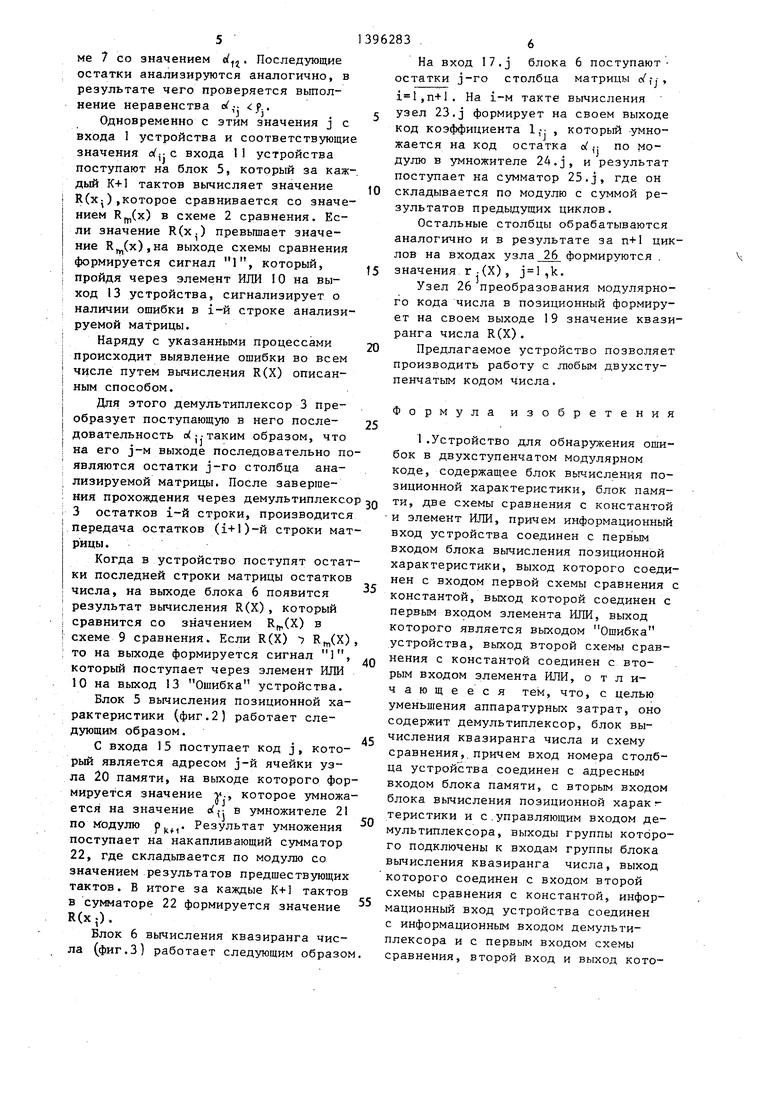

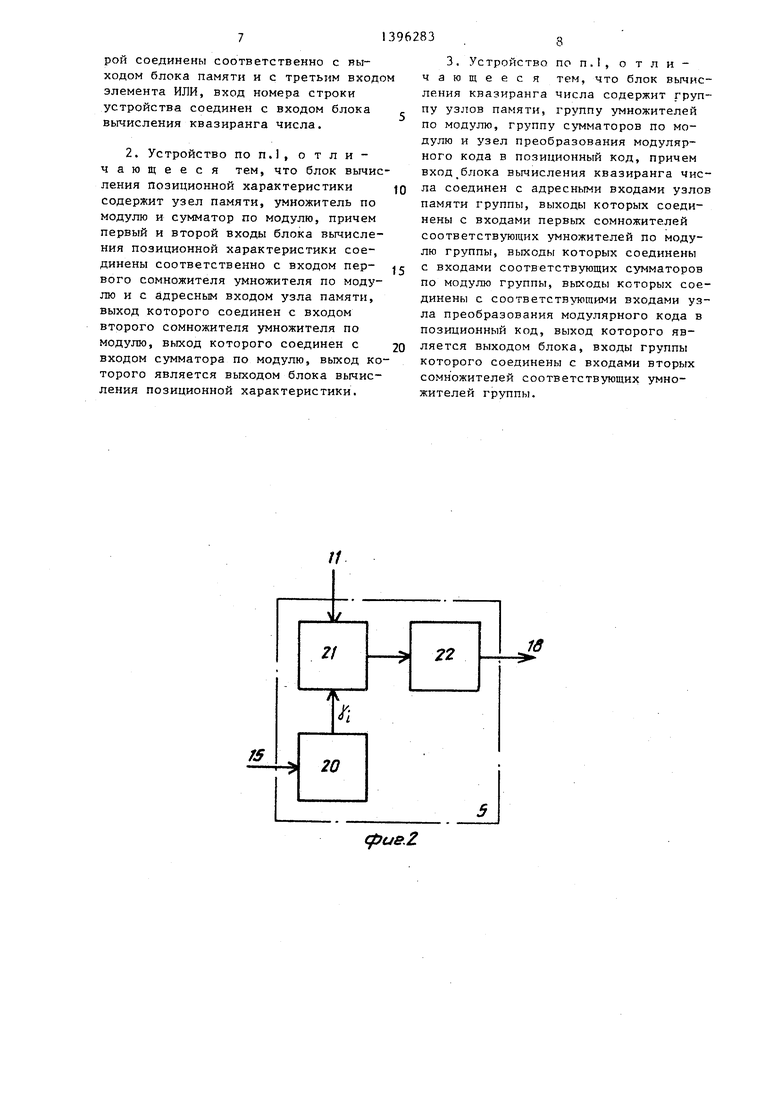

На фиг.1 приведена схема устройства для обнаружения ошибок в двухступенчатом модулярном коде; на фиг.2 - схема блока вычисления позиционной характеристики; на фиг.З схема блока вычисления квазиранга числа.

Устройство (фиг.1} содержит входы 1 и 2 номера столбца и номера строки устройства, демультиплексор 3, блок 4 памяти, блок 5 вычисления позиционной характеристики, блок 6 вычисления квазиранга числа, схему 7 сравненияJ схемы 8 и 9 сравнения с константой, элемент ИЛИ 0, информа- ционный вход 11 устройства, первый вход 12 схемы 7 сравнения, выход 13 Ошибка устройства, второй вход 14 схемь 7 сравнения, вход 15 блока 5 вычисления позиционной характеристи- ки, вход 16 блока 6 вычисления квазиранга числа, группу входов 17.1-17.К блока 6 вычисления квазиранга числа, выход 18 блока 5 вычисления позиционной характеристики и выход 19 блока 6 вычисления квазиранга числа.

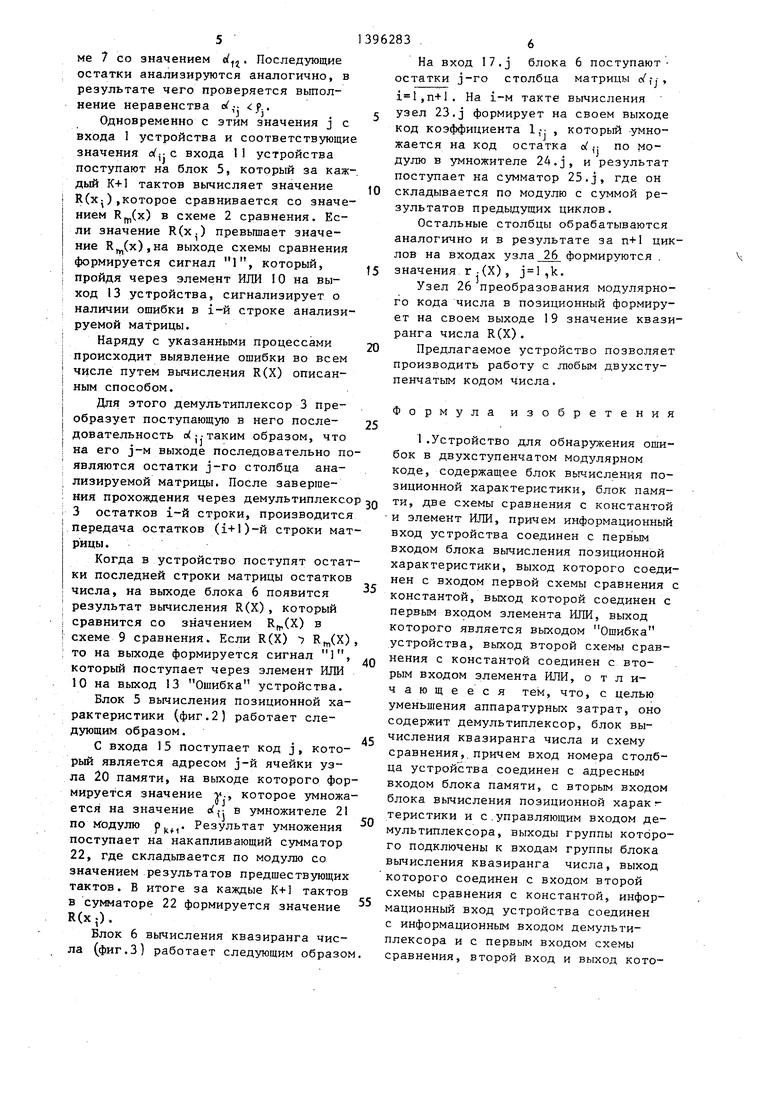

Блок 5 вычисления позиционной характеристики (фиг.2) содержит узел 20 памяти, умножитель 21 по модулю и сумматор 22 по модулю.

Блок 6 вычисления квазиранга числа (фиг.З) содержит группу узлов 23.1-23.К памяти, группу умножителей 24.1-24.К по модулю, группу сумматоров 25.1-25.К по модулю и узел 26 преобразования модулярного кода в позиционный код.

В своей работе устройство (фиг.1) использует следующее.

Представим число X из диапазона - t, совокупностью остатков х..

П 1X1 ям Р

I р. по взаимно простым основани- (, где i 1 , n-t-1 , а Р П Р - .

Таким образом, в рассматриваемом коде основание Р,+, является избыточ-. ,ным. Пусть выбранная система оснований упорядочена, т.е.

Р, , .

, Р

П + 1

Каждый остаток X;,i 1,п+1, пред5 ставим системой остатков с/-- |х

1 по взаимно простым основаниям

j

где j l,. Система оснований второй ступени так же упорядоченная, а основание р K. + I избыточное, т.е.

РПМ П f

J

В результате имеем двухступенчатый модулярный код числа X, который можно представить в виде матрицы остатков ,

-р к

X г

Остатки анализируемого числа X поступают на вход устройства последовательно, по строкам.

Процесс контроля ошибок в принимаемой совокупности остатков с(;- состоит из трех этапов. Необходимо определить меньше ли принятый остаток /;j основания fj. Если да, то

процесс контроля можно продолжать дальше, если нет, то делаем вывод о возникновении ошибки. Необходимо проверить принадлежность совокупнос0

0

5

ти остатков

с1

UM

разрешенной

кодовой комбинации. Если анализируемое число правильно-, то оно принадлежит нулевому пространству избыточного модулярного кода (в данном случае I- I ) и значение квазиранга

УК , , с этого числа К(х () лежит в пределах

{05R(x). Если произойдет ошибка, то искаженное число выйдет за пределы указанного диапазона и его квазиранг R(x р превысит некоторое граничное значение R|(x). Это свойство функции квазиранг позволяет обнаруживать ошибки в избыточном модуляр- ном коде. Значение квазиранга строки определяется как

« 7,|;„,,

где коэффициенты у. определяются следующим образом для

К + 1

Граничное значение

к„(х) .t -

1

Необходимо, располагая совокупностью остатков х

1

l,n-fl,

рить принадлежность числа X к диапазону j- 1 , и только в этом случае его можно считать правильным.

В общем случае контроль указанной совокупности остатков X ; не отличается от описанного процесса контроля совокупности остатков о(;, , . , ,, о( f | + , . Для упрощения технической реализации квазиранг определяется по формуле

RV

г,.(Х)В,

r.(X)Bj

Rm(x)

h-n

M,(,-) P:

де

r j(x)

15 ,-i jip,

k

П Pj ;

базисные числа системы оснований p. , второй сту

первой

ступени;

Mi.

Р .

1

П+1

Процент обнаруживаемых ошибок определяется по формуле

H (1-R,(X):(P,,, -1) первой ступени;

1,00%. для

396283л

l (l-Rjx):() -100% второй ступени.

для

1

10

куп15

роведиаслучае

занной личантро,, ской тся

20

25

30

35

а сисй p. , ой сту40

45

вой

50

+1

ок оп55

для

Систему оснований необходимо подбирать таким образом, чтобы гранич - ное значение квазиранга было как можно меньше избыточного основания.

Демультиплексор 3 распределяет остатки о(;: входа 1 1 на К своих выходов в зависимости от значения j на входе 1 .

Все блоки памяти, используемые в устройстве, представляют собой постоянные запоминающие устройства, в ячейки которых записаны нужные коэффициенты, и адресом к ним является состояние соответствующего входа 1 и 2 устройства.

Схема 7 сравнения формирует сигнал 1 на своем выходе, когда код на вьгходе блока 4 ббльте, чем на входе 1 1 ..

Схемы 8 и 9 сравнения выдают сигнал, если их входной код превысит

т().

и

R. (X) соответстзначениявенно.

В блоке 5 вычисления позиционной характеристики з множитель 21 и накапливающий сумматор 22 выполнены по модулю у,,.

В блоке 6 вьмисления квазиранга числа умножители 24.j и накапливающие сумматоры 25.j выполнены по модулю PJ .

Устройство (фиг.1) работает следующим образом.

В исходном состоянии все сумматоры обнулены, узел 26 преобразования модулярного кода в позиционный готов к преобразованию, на входах 1 и 2 устройства - 1.

Работа устройства начинается в момент появления на входе I1 кода первого остатка с/,,, величина которого сравнивается схемой 7 со значением кода основания р, , установленного

на выходе блока 4 памяти, и, если первое значение превьпиает второе, на выходе схемы 7 формируется сигнал 1, который проходит через элемент ИЛИ 10 на выход 13 устройства, что означает наличие ошибки в анали- зируемом остатке. Далее на вход II подается код следующего остатка ci,, сопровождаемый значением два на входе 1 устройства, что вызывает формирование на выходе блока 4 значе ния р, которое сравнивается в схе

ме 7 со значением d. Последующие остатки анализируются аналогично, в результате чего проверяется выполнение неравенства о,- :р..

Одновременно с этим значения j с входа 1 устройства и соответствующие значения о(- с входа 1 устройства поступают на блок 5, который за каждый К+1 тактов вьгчисляет значение R(x-),которое сравнивается со значением R(x) в схеме 2 сравнения. Если значение R(x.) превышает значение К(х),на выходе схемы сравнения формируется сигнал 1, который, пройдя через элемент ИЛИ IО на выход 13 устройства, сигнализирует о наличии ошибки в i-й строке анализируемой матрицы.

Наряду с указанными процессами происходит выявление ошибки во всем числе путем вычисления R(X) описанным способом.

Для этого демультиплексор 3 преобразует поступающую в него последовательность о --таким образом, что на его J-M выходе последовательно появляются остатки j-ro столбца анализируемой матрицы. После завершения прохождения через демультиплексо 3 остатков i-и строки, производится передача остатков (1+1)-й строки матрицы.

Когда в устройство поступят остатки последней строки матрицы остатков числа, на выходе блока 6 появится результат вычисления R(X), который сравнится со значением ) в схеме 9 сравнения. Если R(X) -7 ) то на выходе формируется сигнал 1, который поступает через элемент ИЛИ 10 на выход 13 Ошибка устройства.

Блок 5 вычисления позиционной характеристики (фиг.2) работает следующим образом.

С входа 15 поступает код j, который является адресом j-й ячейки узла 20 памяти, на выходе которого формируется значение v., которое умножа

ется на значение о(,-- в умножителе 21 по Модулю р|4, Результат умножения поступает на накапливающий сумматор 22, где складывается по модулю со значением результатов предшествующих тактов. В итоге за каждые К+1 тактов в сумматоре 22 формируется значение R(x,).

Блок 6 вычисления квазиранга числа (фиг.З) работает следующим образо

10

20

96283 ,6

На вход 17.J блока 6 поступают- остатки j-ro столбца матрицы (/fj , ,n+l. На i-M такте вычисления с узел 23.j формирует на своем выходе код коэффициента 1,-: , который умноМ

жается на код остатка о ,: по модулю в умножителе 24.j, и результат поступает на сумматор 25,j, где он складывается по модулю с суммой результатов предьщущих циклов.

Остальные столбцы обрабатываются аналогично и в результате за п+1 циклов на входах узла 26 формируются . 15 значения г .(X), j l,k.

Узел 26 преобразования модулярного кода числа в позиционный формирует на своем выходе 19 значение квазиранга числа R(X).

Предлагаемое устройство позволяет производить работу с любым двухступенчатым кодом числа.

Формула изобретения

(pus.Z

фиг.З

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1979 |

|

SU862143A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-05-15—Публикация

1986-11-21—Подача