112

Изобретение относится к вычислительной технике и может быть испрль зовано в системах обработки и передачи информации, использующих модулярные коды, для введения избыточности.

Целью изобретения является расширение функциональных возможностей за счет вычисления, ядра числа.

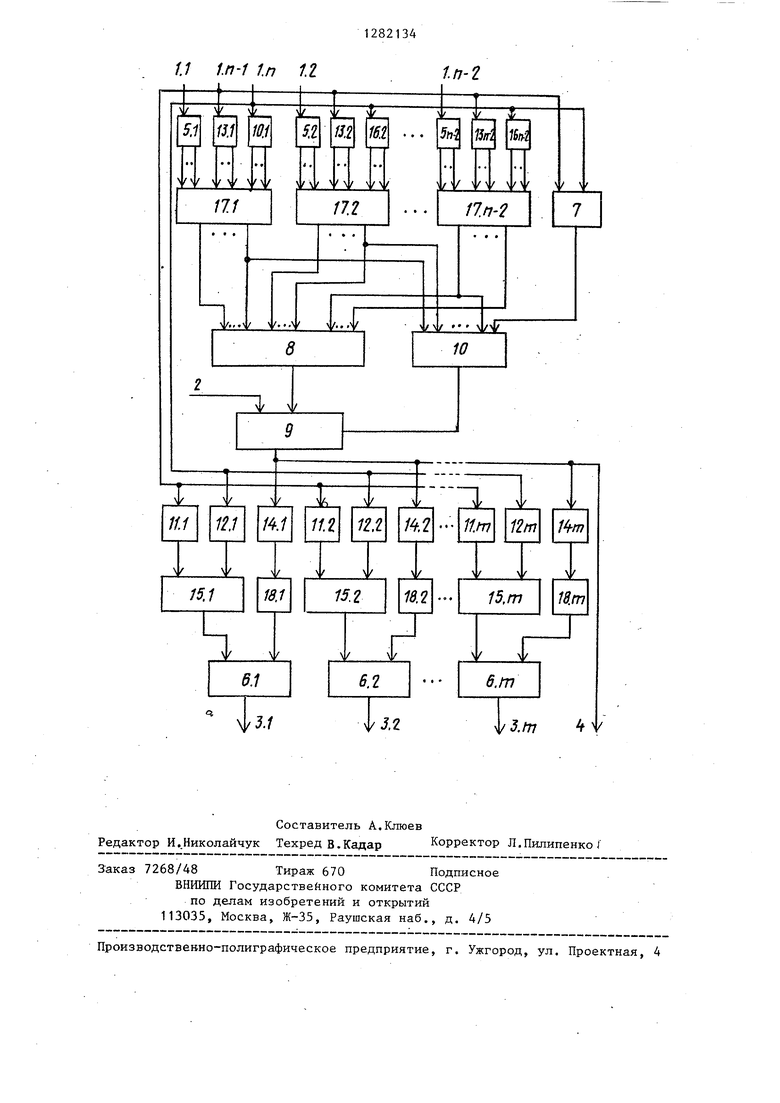

Па чертеже представлена схема предлагаемого устройства.

Устройство для расширения системы оснований модулярного кода содержит группу информационных входов 1.1- 1.п устройства, вход 2 константы устройства, группу информационных выходов 3.1-З.т устройства, выход 4 ядра числа устройства, группу умножителей 5.1-5.П-2 на константу по модулю, группу сумматоров 6.1-6.т по модулю схему 7 сравнения, преобразователь 8 модулярного кода в позиционный код, коммутатор 9, зламент И 10, группы умножителей .11.1-11.т, 12.1-12.т и 13.1-13.n-2 на константу по модулю, группу преобразователей 14.1-14.т позиционного кода в модулярный код, группу сумматоров 15.1-15.т по модулю, группу умножителей 16.1-16.n-2 на константу по модулю, группуосум- маторов 17.1-17.n-2 по модулю и группу умножителей 18.1-18.m на константу по модулю (где пит соответственно количество рабочих и избыточных оснований модулярного кода).

Число X представляется совокупностью остатков ot , oiJ. ,.,., oL по взаимопростым рабочим основаниям /, ,

,., 1).

Остатки числа X по избыточным основаниям А, Р определяются следуhi-r-n

ющим образом:

ЛЛЦПГ

.j-ii.

Р - диапазон представления чиселj t - целые числа, независящие от X (7 . ...5 0,V,-Ut -1), 11 Год .pi - ядро числа X; R Яг-Pi ° диапазона.

R представляется совокупностью остатков по основаниям Pj , причем

и Р,

Ji

fO

5

0

5

0

5

сравнения

m Р Р-:

1

где m - решение « Cmod /).

Если получается значение ядра, равное нулю, то в противном случае R R

в случае а (.,R,0,

П 1 г) X

Сумматоры 6J и 15j работают по модулям , сумматоры 171 - по модулям р. .

Умножители 51, 131, 161 выполняют соответственно операции R.. ;.

-. iy 9«° h,//i УМНОЖИТ И

и V2J - соответственно операции

l6,,-,- n-i-lpn+j « M«IP«4J . умножители 18J - операции 101 R I .

,, „ РН+ J I Pf,

Устройство для расширения системы оснований модулярного кода работает следующим образом.

Коды остатков исходного представления числа X (cJ, d,j,. . .,о() , по входам 1.1-1.П поступают на входы умножителей 5.1-5.П-2, 13.1-13.n-2, 16.1-l6.n-2 и на входы умножителей 11.1-11.га, 12.1-12.т. На выходе умножителей 5.1, 13.1, 16.1 по окончании переходных процессов появ ляют- ся коды величин

0

IR

Я,

iRn

в

П

в одноПозиционном виде, которые поступают на входы соответствующего сумматора 17.1, в результате чего

5 на выходах сумматоров 17.1-17.n-2 появляются коды непозиционного представления ядра числа R .

В преобразователе 8 происходит преобразование непозиционного кода

0 ядра в позиционный код. Если хотя бы один из кодов остатка R не равен нулю или .,, то на выходе схемы 7 сравнения присутствует код нулевого потенциала, следовательно,

5 нулевой потенциал на выходе элемента И 10 разрешает прохождение через коммутатор 9 кода ядра числа. В противном случае на выходе элемента И 10 появляется потенциал логической

единицы, который запрещает прохождение кода R О через коммутатор 9 и вызывает появление на его выходе кода ядра числа, равного R , с входа 2 устройства. Код ядра числа посту- пает на входы преобразователей 14.1- 14.т, на выходах которых через время, равное длительности переходных процессов, появляются коды величин . . Эти величины преобразуют- ся в умножителях 18.1-18.т по модулям в значения

leiR

. pn.J

которые поступают на входы суммато ров 6.1-6.т по модулям, на других входах которых присутствуют коды величин

Pn4j

.

ll6,-/c

..Л...

полученные за счет прохождения кодов остатков .,, и ci г через умножи т елц- по модулям 11.J и 12.J и суммирова- ния полученных кодов в сумматорах 15.1-15.т. В результате на выходах сумматоров 6.1-6.т получаются коды остатков расширения d,.,,,,ai соответственно, которые поступают на выходы 3.1-3.т устройства. Значение ядра числа с выхода коммутатора 9. поступает на выход 4 устройства.

Ф. ормула изобретения

Устройство для расширения системы оснований модулярного кода, содержа- щее три группы умножителей на константу по модулю и две группы сумматоров по модулю, причем информационные ВХО.ЦЫ, кроме двух старших, группы устройства соединены соответственно с входами умножителей и на константу по модулю первой группы,

два старших информационных входа группы устройства соединены соответственно с входами умножителей на константу по модулю второй и третьей групп выходы сумматоров по модулю первой г р уппы являются группой инфор мационных выходов устройства, выходы

.блоков умножения на константу по модулю второй и третьей групп соединены соответственно с входами первого

5 t3

20

25 у,

35

40

-

45

и второго слагаемых сумматоров по модулю второй группы, выходы которых соединены с входами первых слагаемых соответствующих сумматоров по модулю первой группы, отличающее- е я тем, что, с целью расширения функциональных возможностей за счет вычисления ядра числа, оно содержит третью группу сумматоров по модулю, схему сравнения, преобразователь модулярного кода в позиционный код, i коммутатор, элемент И, группу преобразователей позиционного кода в модулярный код, четвертую, пятую и шес- тую группы умножителей на константу по модулю, причем два старших информационных входа группы устройства соединены соответственно с входами умножителей на константу по модулю четвертой и пятой групп, выходы умножителей на константу по модулю первой, четвертой.и пятой групп соединены соответственно с входами первого, второго и третьего слагаемых соответствующих сумматоров по модулю третьей группы, выходы унитарного кода суммы которых соединены соответственно с входами преобразователя модулярного кода в позиционный код, выход которого соединен с первым ин- фбрмационным входом коммутатора, выход которого соединен с входами преобразователей позиционного кода в модулярный код группы, выходы которых соединены с входами соответствующих умножителей на константу по модулю шестой группы, выходы которых соединены с входами вторых слагаемых соответствующих сумматоров по модулю первой группы, вход константы устройства и выход ядра числа устройства соединены соответственно с вторым информационным входом и выходом коммутатора, управляющий вход которого соединен с выходом элемента И, входы которого соединены соответственно с нулевыми выходами унитарного кода суммы сумматоров по модулю третьей группы и выходом схемы сравнения, первый и второй входы которой соединены соответственно с двумя старшими информационными входами группы устройства.

/./ l.n-1 l.n 1.1

1.П-2

Ju X-, il tl

13.1

10.1

5.1

т

f

Ш

/j/

/

Пп-2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для обнаружения ошибок в двухступенчатом модулярном коде | 1986 |

|

SU1396283A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1986 |

|

SU1388996A1 |

| Устройство для вычисления позиционных характеристик модулярного кода | 1989 |

|

SU1608660A1 |

| Устройство для вычисления остатка по модулю 2 @ +1 | 1990 |

|

SU1734212A1 |

| Преобразователь чисел из модулярного кода в позиционный код | 1987 |

|

SU1481898A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах обработКйт и передачи информации, использу- ющих модулярные коды, для введения . избыточности. Целью изобретения является расширение функциональных воз- йожностей за счет ядра числа. Поставленная цель достигается тем, что устройство, содержащее три группы умножителей на константу по модулю и две группы сумматоров по модулю, содержит дополнительно группу преобразователей позиционного кода в модулярный, код, схему сравнения, элемент И, преобразователь модулярного кода в позиционный, третью группу сумматоров по модулю, четвертую, пятую и шестую группы умножителей на константу по модулю и коммутатор. Техническое преимущество заключается в обеспечении определения ядра числа, позволяющего упростить ряд немодульных операций, в том числе расширение системы оснований. 1 ил. о «9 (Л го 00 N9 00 ф

r,,, / л Л f., Л f i /V

S/

Составитель А.Клюев Редактор И..Николайчук Техред В.Кадар Корректор Л,Пилипенко I

Заказ 7268/48 Тираж 670 Подписное ВНИИПИ Государствейного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производствевно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| УСТРОЙСТВО ДЛЯ ВВЕДЕНИЯ ИЗБЫТОЧНОСТИ : | 0 |

|

SU350000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения ошибок в слабоарифметическом коде системы остаточных классов | 1984 |

|

SU1166116A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1985-07-11—Подача