00

со CD

Слд

1

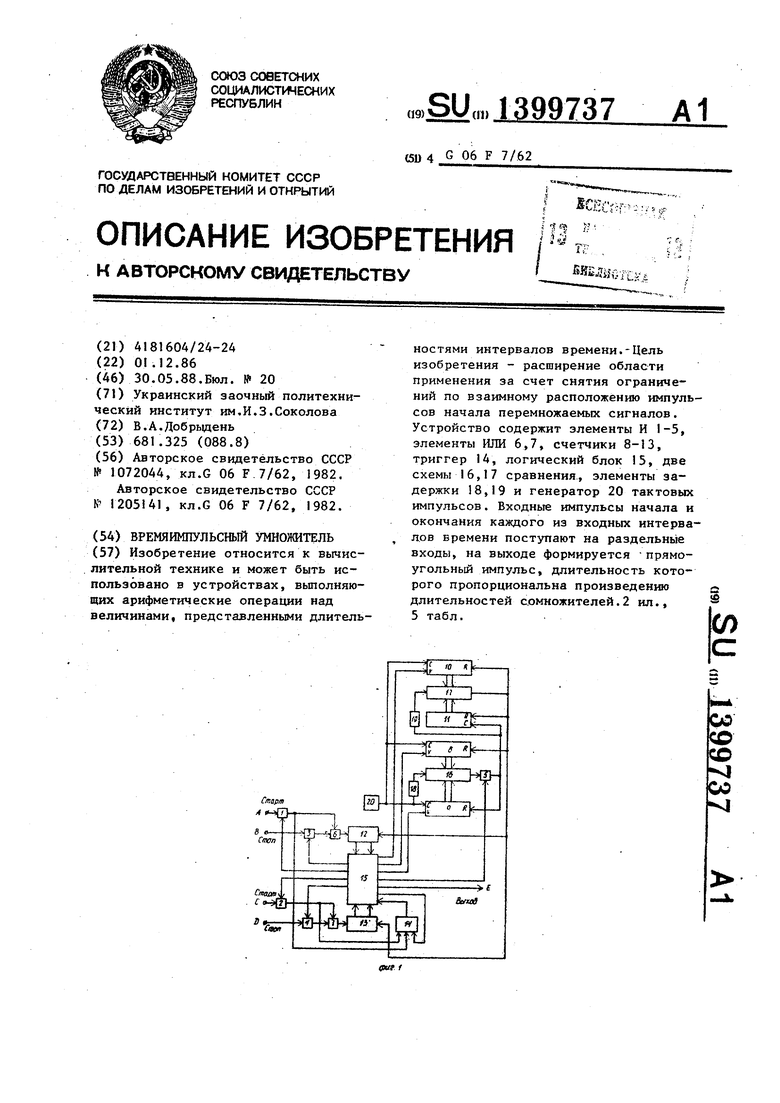

Изобретение относится к вычислительной технике и может быть использовано в устройствах, выполняющих арифметические операции над величи- Йами представленными длительностями интервалов времени.

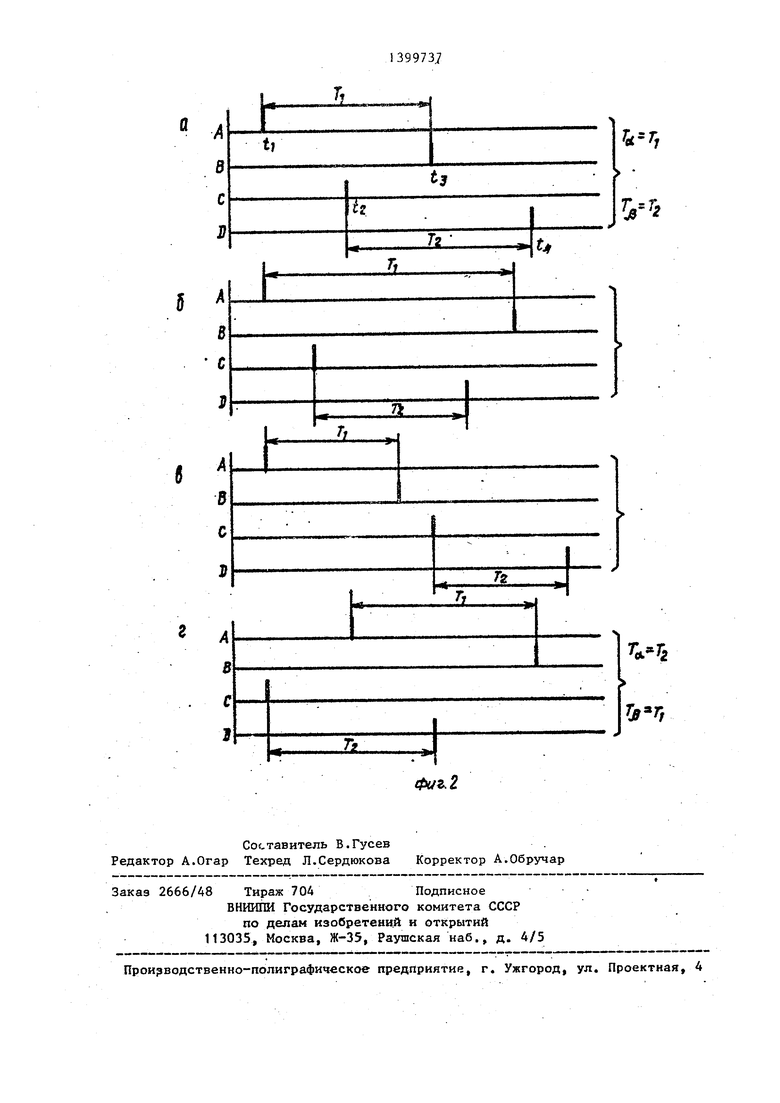

Цель изобретения - расширение области применения умножителя за счет снятия ограничений по взаимному рас- Ьоложению импульсов начала перемножа емых сигналов. ; На фиг.1 представлена функциональ- |ная схема времяимпульсного умножите- я; на фиг.2 - варианты взаимного расположения входных сигналов, I Времяимпульсный умножитель содер- |жит с первого по пятый элементы И |1-5, первый 6 и второй 7 элементы ИЛИ, с первого по шестой счетчики , триггер 14, логический блок 15, |вьшолненный в виде программируемой

13997372

. логической матрицы, первую 16 и вторую 17 схемы сравнения, первый 18 и второй 19 элементы задержки и гене- ратор.20 тактовых импульсов. Первый 8 и третий 10 счетчики предназначены для формирования, и фиксации цифровых значений тип длительностей вход- ных интервалов времени, причем т-го fO из них (Tjj) ,стартовый импульс которого появился раньше (на фиг. 2а-в Т Т, ; на фиг.2г Т,, Tj), чем стартовый импульс другого (Тд). Второй 9 и четвертый 11 счетчики участвуют

15 в формировании выходного интервала времени Т, Т, Т. Пятый 12 и шестой 13 счетчики формируют адресные сигналы логического блока 15. Триггер I 14 формирует управляющий сигнал для

20 логического блока 15.

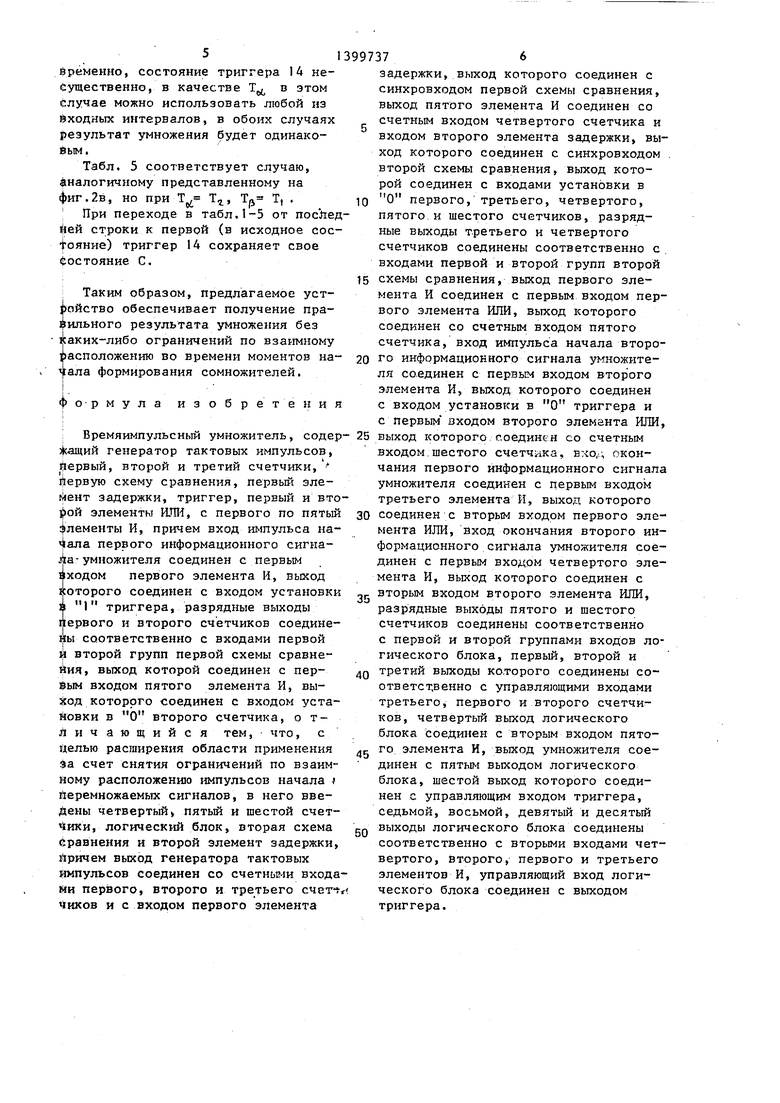

Логический блок 15 реализует следующие логические функции;

товый импульс другого (Тд). Второй 9 и четвертый 11 счетчики участвуют

в формировании выходного интервала времени Т, Т, Т. Пятый 12 и шестой 13 счетчики формируют адресные сигналы логического блока 15. Триггер I 14 формирует управляющий сигнал для

логического блока 15.

Логический блок 15 реализует следующие логические функции;

| название | год | авторы | номер документа |

|---|---|---|---|

| Времяимпульсный умножитель | 1982 |

|

SU1205141A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Времяимпульсный сумматор | 1982 |

|

SU1188733A1 |

| Вычислительное устройство | 1982 |

|

SU1072044A1 |

| Устройство для умножения полиномов многих переменных | 1980 |

|

SU922732A1 |

| Вычислительное устройство | 1983 |

|

SU1120324A1 |

| Программируемое устройство управления | 1986 |

|

SU1448393A1 |

| Число-импульсное множительное устройство | 1986 |

|

SU1424014A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах, выполняющих арифметические операции над величинами, представленными длительностями интервалов времени. Цель изобретения - расширение области применения за счет снятия ограничений по взаимному расположению импульсов начала перемножаемых сигналов. Устройство содержит элементы И 1-5, элементы ИЛИ 6,7, счетчики 8-13, триггер 14, логический блок 15, две схемы 16,17 сравнения, элементы задержки 18,19 и генератор 20 тактовых импульсов. Входные импульсы начала и окончания каждого из входных интервалов времени поступают на раздельные входы, на выходе формируется -прямоугольный импульс, длительность которого пропорциональна произведению длительностей сомножителей.2 ил., 5 табл. § О)

П.

Л

Л,

л,

л.

А,А

А, AJ В.Вг

в,в,

А,,В.г A,S,jC + В,В.С

(ожидание начала счета Т); (ожидание конца счета Т,); (ожидание начала, счета Т.);

(ожидание конца счета Т);

(единичный сигнал с момента окончания Тд до момента окончания Т,); (счет Т„ в счетчике 8);

(A,Aj,+ А,Аг)С+(В,В2+ В, В2)С (счет в счетчике 9 с момента начала

Тп до окончания Т); А, + (счет Т в счетчике 10);

S,AjB,B:i (А,+ А.г)(В,+ В)

(ожидание момента начала Т);

(с момента начала Тя и Т, до окончания выходного интервала Т),

Р,-РЗ

де Л,- Л5 - сигналы на выходах логического блока 15, соединенных соответственно с входами элементов И JQ 1-5,

сигналы на выходах логического блока 15, соединенных соответственно с управляющими входами 55 первого, второго и третьего счетчиков 8-1Oi сигналы на выходе логического блока 15, соедиР. ненном с управляющим входом триггера 14;

А, ,А2,В, , состояния первого (младшего) и второго разрядов счетчиков 12 и 13 соответственно; С - состояние выхода триггера 1 4 .

Времяимпульсный умножитель работает следующим образом.

Моментгы начала и окончания входного интервала Т времени (первого со-- .ьшожителя) задаются короткими импульсами,поступающими соответственно на входы А и В устройства (фиг.2). Аналогично короткими импульсами на входах С и D задаются моменты начала и окончания второго сомножителя Tj.

В исходном состоянии все счетчики устройства установлены в нуль (А,

А

В, В 0), при этом блок

15 поддерживает единичный сигнал на вторых входах элементов И 1 и 2 и -на разрешающем входе триггера 1А, на остальных его выходах поддерживается нулевой сигнал, т.е. счетчики 8-11 бездействуют.

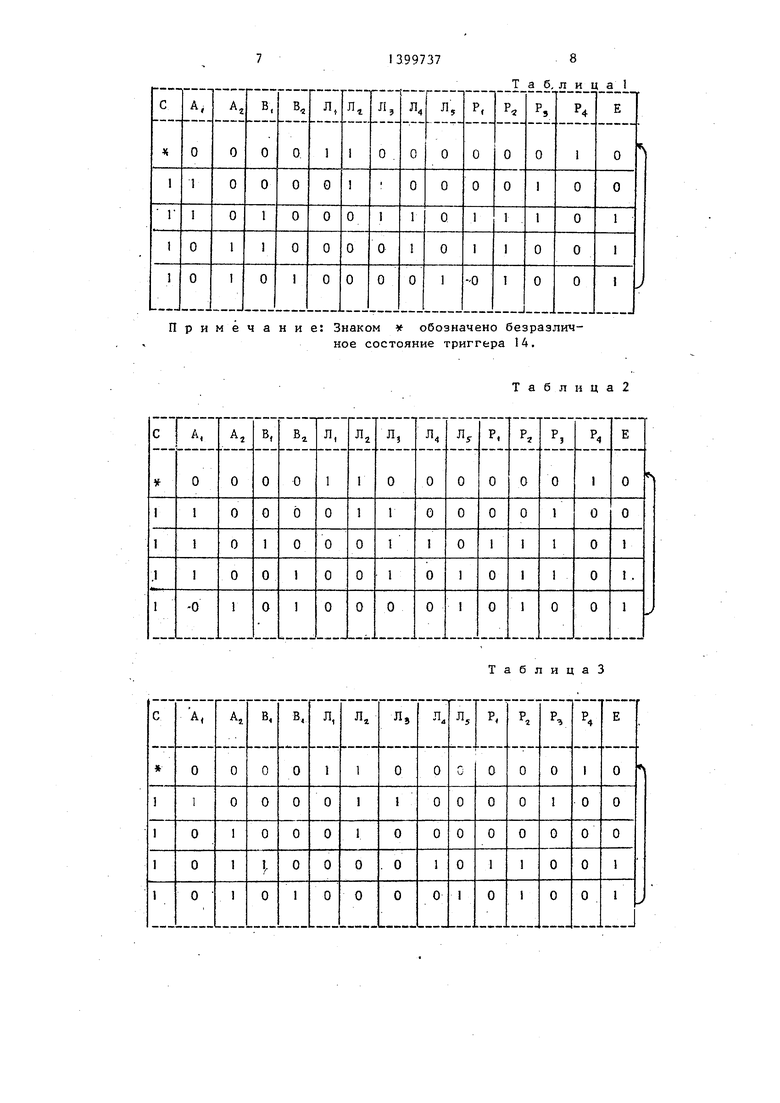

Рассмотрим случай, когда первым на входы устройства поступает интервал Т, (т.е. Тд Т|, фиг.2а-в). В момент t, импульс начала Т, поступает на вход А устройства на импульсы, поступающие на вход B,D, устройство при этом не реагирует}. Пройдя через элемент И 1 и элемент ИЛИ 6 на тактовый вход счетчика 12, этот импульс устанавливает А, 1, кроме того, он устанавливает . С этого момента единичный сигнал снимается с второго входа элемента И 1 и -- разрещающего входа триггера 14, устанавливается на разрешающем входе счетчика 10, который начинает считать тактовые импульсы с выхода генератора 20. Изменение состояний счечиков- 12 и 13 и триггера 14 в рассматриваемом случае, а также соот- ветствующие выходные сигналы блока 15 показаны в табл.1.

t на вход С устройства

В момент

поступает импульс Старт второго сомножителя Т. Пройдя через элемент И2 и элемент ИЛИ 7 на тактовый вход счетчика 13, этот импульс устанавливает В, 1. В результате эле- .мент И 2 закрывается по второму входу, элемент И 4 открывается, а счетчики 8 и 9 начинают с этого момента счет тактовьк импульсов. С этого же момента появляется единичный сигнал на выходе Е устройства.

Далее в момент t,, на вход В поступает импульс окончания интервала Т, , проходящий через элемент И 3 и элемент ИЛИ 6 на тактовый вход счетчика 12 и устанавливающий А, О, . Благодаря этому счетчик -10 прекращает счет. Элемент И 3 закрьгеается, . продолжают счет счетчики 8 и 9. На конец э момент t поступает импульс

на вход D - импульс окончания второго сомножителя. Этот импульс проходит через элементы И 4 и элемент И 7 на тактовый вход счетчика 13, устанав0

5

0 5 0 в

0

ливая В, О,

В2 1

Вследствие этого

счетчик 8 прекращает счет.

Элемент И 5 открьшается, так что последний тактовый импульс, поступивший в счетчик 8, проходит через эле-, мент 18, схему 16 и элемент И 5, возвращая в нуль счетчик 9 и добавляя единицу в счетчик 11. В счетчик 9 продолжают поступать тактовые им- пульс ы, и каждый раз, когда его содержимое достигает значения п, тактовый импульс, проходя через элемент 18 задержки, схему 16 сравнения и элемент И 5, повторяет описанные действия. Так продолжается до тех пор, пока содержимое счетчика 1 1 не соав- няется с содержимым m счетчика 10, т.е. пока не будут m раз отсчитаны п тактовых импульсов с момента начала интервала T/j. Входной импульс счетчика 11, обеспечивающий указанное равенство, проходит через элемент 19 и схему 17 и возвращает устройство в исходное состояние, уста- - навливая в нуль счетчики 8 и 10-12 счетчик 9 устанавливается в нуль импульсом с выхода элемента И З). В этот момент снимается единичный сигнал с выхода Е устройства, присутствующий на нем с момента поступления импульса начала сомножителя То до момента, когда в га-й раз счетчик 9 заполнится тактовыми импульсами до значения п. Поскольку m FT,

FT р (в рассматриваемом случае , Тп -г), длительность Т выходного прямоугольного импульса на выходе Е устройства определяется формулой Tj FT,T2;.

В случаях, показанных на фиг.26, в, устройство работает аналогично (см.табл.2 и 3). Если входной интервал Т, начинает формироваться

0 а п TCI

5

г

чём Т.

т.е.

т А1

| V i 2

как, например, на фиг.2г, где

раньше,

Т

в остальном ситуация аналогична ситуации на фиг.2а|, устройство работает

так же, только триггер 14, фиксирующий информацию о том, какой из вход- tg ньгх интервалов начал формироваться первым (, если Т Т,, С О, Тд Тэ), находится в нулевом состоянии (см.табл.4). Если интервалы Т, и Tg

если

начинаются практически одновременно, состояние триггера 14 не- (ущественно, в качестве Т в этом (Случае можно использовать любой нз йходных интервалов, в обоих случаях результат умножения будет одинаковым .

Табл. 5 соответствует случаю, Аналогичному представленному на фиг.2в, но при Т, Тр Т, . При переходе в табл.1-5 от посЛед liieft строки к первой (в исходное сос- fonHHe) триггер 14 сохраняет свое Достояние С.

Таким образом, предлагаемое уст- ойство обеспечивает получение пра- иильного результата умножения без каких-либо ограничений по взаимному 1 асположеник) во времени моментов на- гала формирования сомножителей.

фо-рмула изобретения

. Времяимпульсный умножитель, содер з|сащий генератор тактовых импульсов, Йервый, второй и третий счетчики, 1| ервую схему сравнения, первый эле- задержки, триггер, первый и второй элементы ИЛИ, с первого по пятьш Элементы И, причем вход импульса на- |ала первого информационного сигна- jjia-умножителя соединен с первым входом первого элемента И, выход |:оторого соединен с входом установки

1 триггера, разрядные выходы jiepBoro и второго счетчиков соедине- ы соответственно с входами первой Ц второй групп первой схемы сравне- йич, выход которой соединен с первым входом пятого элемента И, вы- Ход которого соединен с входом установки в О второго счетчика, отличающийся тем, что, с Целью расширения области применения За счет снятия ограничений по взаимному расположению импульсов начала перемножаемых сигналов, в него введены четвертый, пятый и шестой счет- 1ики, логический блок, вторая схема (|:раБнения и второй элемент задержки, йричем выход генератора тактовых Импульсов соединен со счетньй-ш входа Ми первого, второго и третьего счет Чихов и с входом первого элемента

5

0

5

0

5

0

5

0

задержки, выход которого соединен с синхровходом первой схемы сравнения, выход пятого элемента И соединен со счетным входом четвертого счетчика и входом второго элемента задержки, выход которого Соединен с синхровходом . второй схемы сравнения, выход которой соединен с входами установки в О первого, третьего, четвертого, пятого и шестого счетчиков, разрядные выходы третьего и четвертого счетчиков соединены соответственно с входами первой и второй групп второй схемы сравнения, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом пятого счетчика, вход импульса начала второго информационного сигнала умножителя соединен с первым входом второго элемента И, выход которого соединен с входом установки в О триггера и с первым входом второго элемента ИЛИ, выход которого соединен со счетным входом, шестого счетчика, вхо,ч окончания первого информационного сигнала умножителя соединен с первым входом третьего элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, вход окончания второго информационного сигнала умножителя соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, разрядные выходы пятого и шестого счетчиков соединены соответственно с первой и второй группами входов логического блока, первьй, второй и третий выходы которого соединены соответственно с управляющими входами третьего, первого н второго счетчиков, четвертый выход логического блока соединен с вторым входом пятого элемента И, выход умножителя соединен с пятым выходом логического блока, шестой выход которого соединен с управляющим входом триггера, седьмой, восьмой, девятый и десятый выходы логического блока соединены соответственно с вторыми входами четвертого, второго, первого и третьего элементов И, управляющий вход логического блока соединен с выходом триггера.

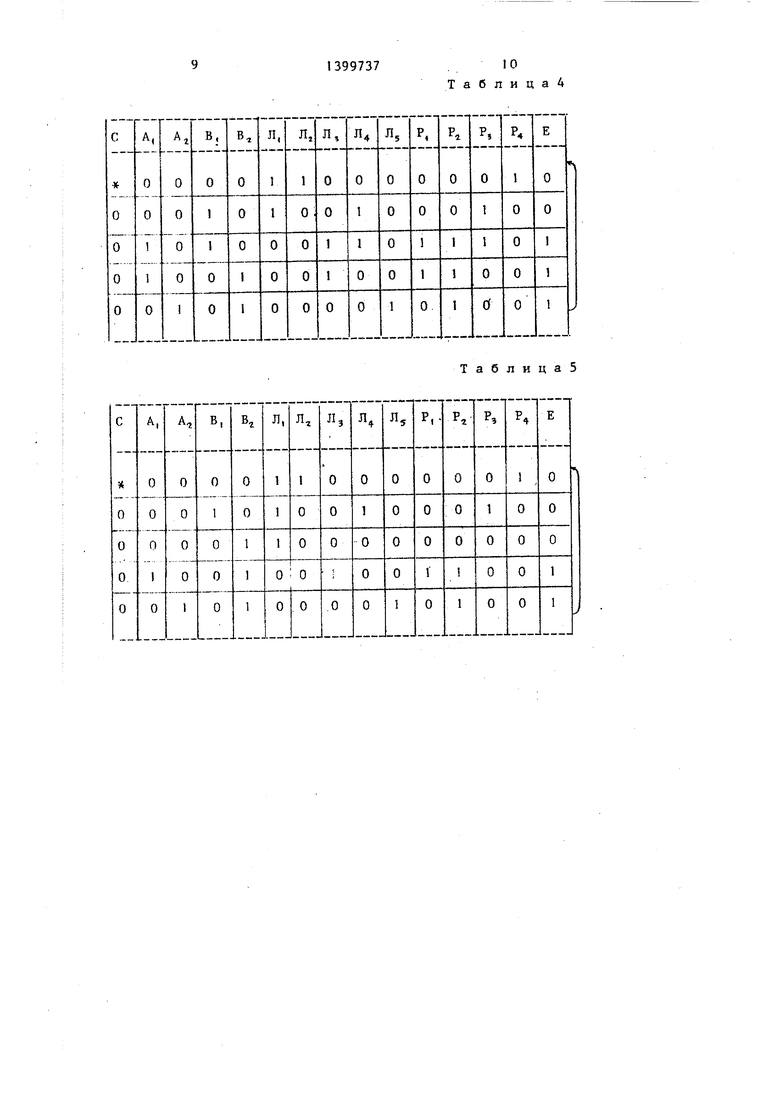

Примечание: Знаком обозначено безразличное состояние триггера 14.

Т а б л и ц а 2

ТаблицаЗ

ТаблицаЗ

| Вычислительное устройство | 1982 |

|

SU1072044A1 |

| Времяимпульсный умножитель | 1982 |

|

SU1205141A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-01—Подача