СЛ

со со со

О5 4

достигается благодаря тому, что в устройство введены информационные входы I и 2, первая матрица 3 с вычислительными модулями 4 и выходом 5, дополнительные матрицы 6 с вычислительными модулями 7 и входами 8 и 9, блок 10 конвейерных регистров, содержащий каналы 11 и выход 12, информа- ционньй выход 13 устройства, вход 14 синхронизации. 4 ип.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ С КОРРЕКЦИЕЙ ОШИБКИ | 1992 |

|

RU2018950C1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1987 |

|

SU1418745A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Систолический процессор для вычисления полиномиальных функций | 1988 |

|

SU1608689A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1737462A1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1387173A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Систолический процессор дискретного преобразования Фурье | 1986 |

|

SU1363243A1 |

| Систолический процессор для двумерного дискретного преобразования Фурье | 1988 |

|

SU1608688A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов- и изображений высокой производительности. Цель изобретения - расширение функциональных возможностей за счет обработки в различных ортогональных базисах и выполнения многомерного дискретного преобразования Фурье. Поставленная цель

1

Изобретение относится к вычисли- тельной технике и может быть исполь- зовано в специализированных системах обработки сигналов и изображений вы- сокой производительности,с

Цель изобретения - расширение функциональных возможностей за счет обработки в различных ортогональных базисах и выполнения многомерного дискретного преобразования Фурье. Ю

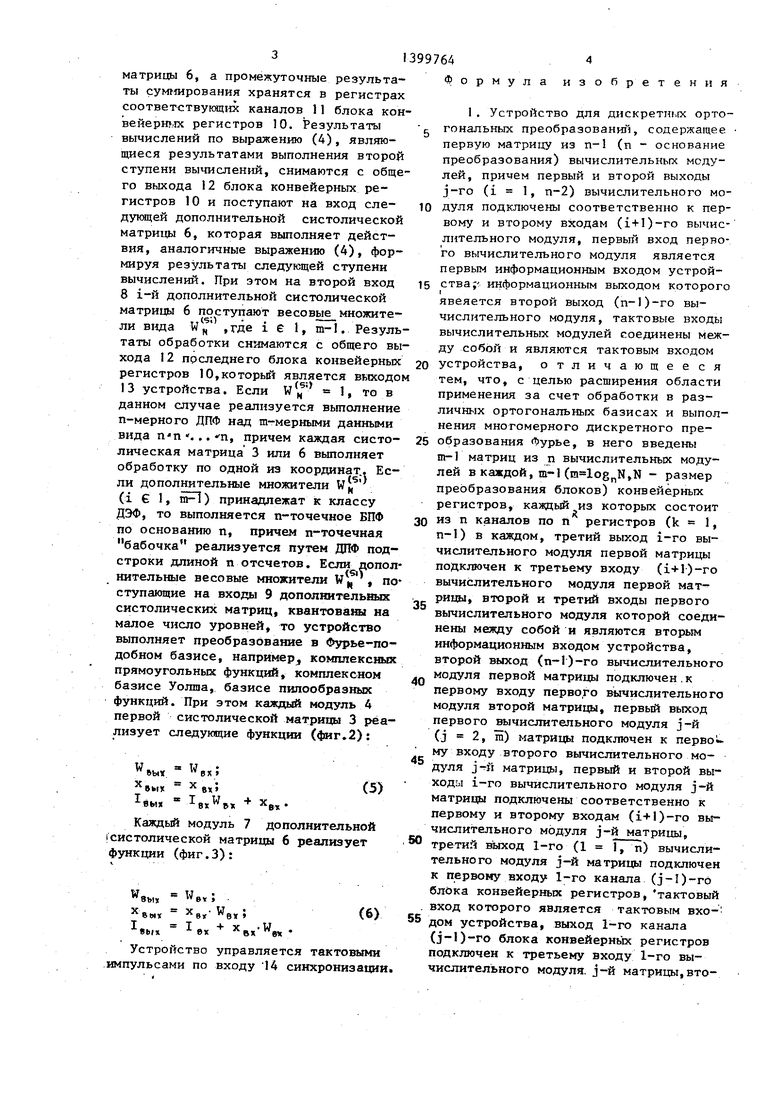

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема вычислительного модуля первой (систолической) матрицы; на фиг.З - функ- 15 ционапьная схема вычислительного модуля второй систолической матрицы; на фиг.4 - функциональная схема канала блока конвейерных регистров.

Устройство (фиг.1) содержит инфор-20 мационные входы 1 и 2, первую систолическую матрицу 3 с вычислительными модулями 4 и выходом 5, т-1 дополнительных систолических матриц 6 с вычислительными модулями 7 и вторым 8 25 и третьим 9 входами, блок 10 из т-Т конвейерных регистров, содержащий каналы 11 и выход 12,информационный выход 13 устройства и вход 14 синхронизации.30

Вычислительный модуль 4 (фиг.2) содержит входы 15-17, регистры 18 и 19, умножитель 20, сумматор 21 и выходы 22-24.

Вычислительный модуль 7 (фиг.З) « содержит входы 25-27, регистр 28, умножитель 29, сумматор 30 и выходы 31-33.

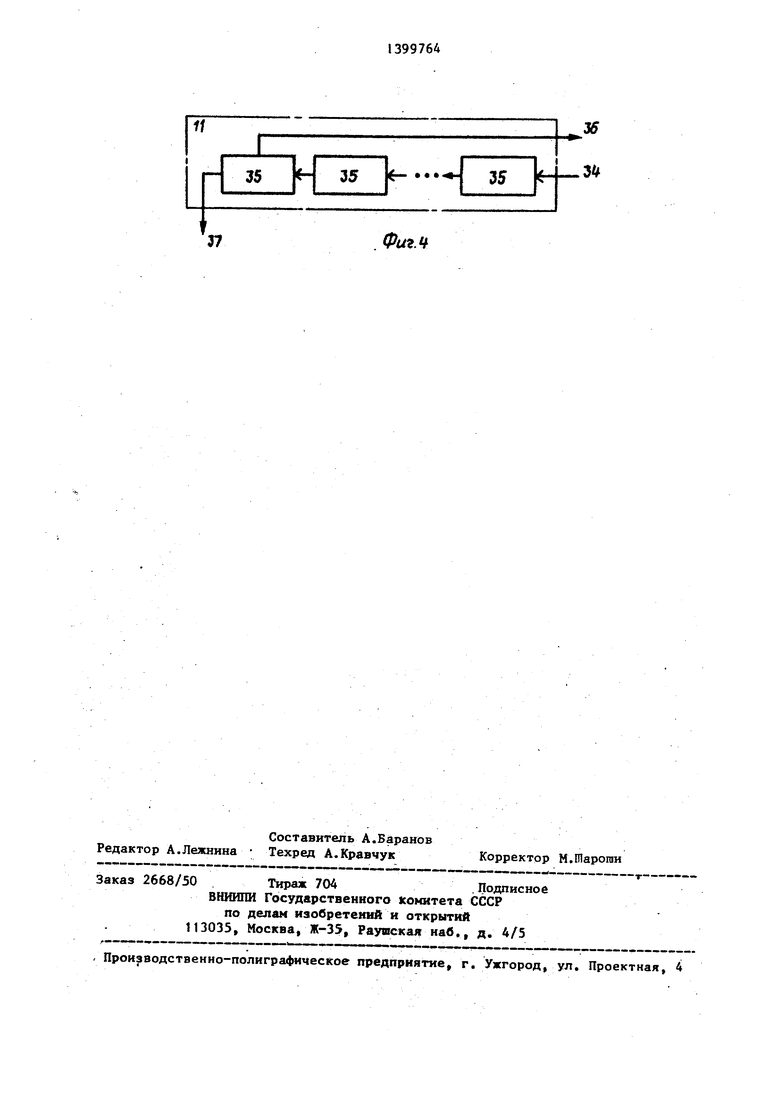

Канал 11 (фиг.4) содержит вход 34, регистры 35 и выходы 36 и 37. 0

Устройство работает следующим образом.

На вход } устройства поступают весовые множители вида

Wn ехр j27pl/n ; le 0,n-i,- ре о, п-1..(1)

На вход 2 устройства поступают данные k-й подстроки исходной последовательности из N отсчетов. По сле загрузки (п-1)-го злемента k-й подстроки при поступлении последнего п-го элемента подстроки систолической матрицей 3 выполняется преобразование вида

IK) izlре

Ср - Z1 x(k-l)n + 1 + I-WJ, , (2)

, .г

где Ср - элемент с ном.ером р (р О,

п-1) обработанной k-й подстроки, являющейся результатом обработки на первой ступени вычислений.

С выхода 5 первой систолической

матрицы 3 результаты С- вь полнения

п-точечного ДПФ поступают на вторую ступень обработки. Указанные результаты поступают на первый вход первой дополнительной систолической матрицы 6, где домножаются на дополнительные весовые множители поступающие на второй вход 8 указанной матрицы. Лолучен1Я,1е результаты умножения вида

/ С

W

(Si)

(3)

поступают на первый вход второго модуля 7 первой дополнительной матрицы 6. На вход 9 второго модуля 7 по- ступаот весовые множители вида . Вычислительные модули 7 дополнительной систолической матрицы 6 реализуют вычисления:

с - Vr Sr : Тп). (4)

k.o

причем элементы результата с разными вомерами от О до (п-1)-го формируются параллельно-последовательно в модулях 7 дополнительной систолической

матрицы 6, а промежуточные результаты суммирования хранятся в регистрах соответствующ1с каналов 11 блока кон- вейерш..1х регистров 10. Результаты вычислений по выражению (4), являющиеся результатами выполнения второй ступени вычислений, снимаются с общего выхода 12 блока конвейерных регистров 10 и поступают на вход еле- дующей дополнительной систолической матритда 6, которая выполняет действия, аналогичные выражению (4), формируя результаты следующей ступени вычислений. При зтом на второй вход 8 i-й дополнительной систолической матрицы 6 поступают весовые множитет т И 4 f

ЛИ вида W ,где i е 1, т-1. Результаты обработки снимаются с общего выхода 12 последнего блока конвейерных регистров 10,которьй является выходом 13 устройства. Если ц 1, то в данном случае реализуется вьшолнение п-мерного ДПФ над т-мерными данными вида п П . ..п, причем каждая систо- лическая матрица 3 или 6 вьтолняет обработку по одной из координат. Если дополнительные множители W (i € 1, ni-1) принадлежат к классу ДЭФ, то выполняется п-точечное БПФ по основанию п, причем п-точечная бабочка реализуется путем ДПФ подстроки длиной п отсчетов. Если дополнительные весовые множители W,, , поступающие на входы 9 дополнительных систолических матриц, квантованы на малое число уровней, то устройство выполняет преобразование в Фурье-подобном базисе, например комплексных прямоугольных функций, комплексном базисе Уолша, базисе пилообразных функций. При этом каждый модуль 4 первой систолической матрицы 3 реализует следующие функции (фиг.2):

W

вх ex

вх

Каждьй модуль 7 дополнительной (систолической матрицы 6 реализует функции (фиг.З):

Bt ex

ex BX W

Устройство управляется тактовыми импульсами по входу 14 синхронизации.

- - юis 20м 25 зо

35

40

45

50

55

Формула изобретения

2, Устройство по п. 1, отличающееся тем, что вычислитель- йый модуль первой матрицы содержит первый и второй регистры, умножитель И сумматор, причем первым входом вычислительного модуля является инфор- Йационнь1й вход первого регистра, пер|вый выход которого является первым ыходом модуля, второй выход первого регистра подключен к первому входу |умножителя, второй вход которого яв- ртяется вторым входом модуля, выход 1умножителя подключен к первому входу сумматора, выход которого является :вторым выходом модуля, третьим выходом которого является первый выход второго регистра, второй выход которого подключен к второму входу сумматора, информационный вход второго ре- тистра является третьим входом моду- |ля, тактЬвым входом которого явпяют- |ся соединенные между собой тактовые входы первого и второго регистров.

Фи9.2

3« Устройство по п, 1, о т л и - ч а ю ц е е с я тем, что вычисли- тельный модуль j-й (л 2, М) матри- цы содержит регистр, умножитель и сумматор, причем первый вход умножителя,, является первым входом модуля, вторым входом которого является ин- формациоиньй вход регистра, выход умножителя подключен к первому входу сумматора и является первым выходом модуля-, вторым выходом которого является первый выход регистра, второй выход которого подключен к второму

входу умножителя, выход сумматора является третьим выходом модуля, третьим входом которого является второй вход сумматора, тактовый вход регистра является тактовым входом модуля.

а первый и второй выявляются соответствеино первым и вторым выходами канала, вторые выходы каналов соединены между собой и являются выходом j-ro блока конвейерных регистров, тактовым входом которого являются соединенные меяду собой тактовые входы п регистров.

входом канала, ходы п регистра

гЗ

37

«г.

| Аллен Д, Архитектура вычислительных устройств | |||

| ТИИЭР, т | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Системы параллельной обработки/Под ред | |||

| Д.Ивенса, М.: Мир, 1986,cv 416. | |||

Авторы

Даты

1988-05-30—Публикация

1986-12-22—Подача