t

Изобретение относится к радиотехнике и может найти применение при создании многоканальных систем с частотным разделением каналов,

Целью изобретения является повышение точности устройства„

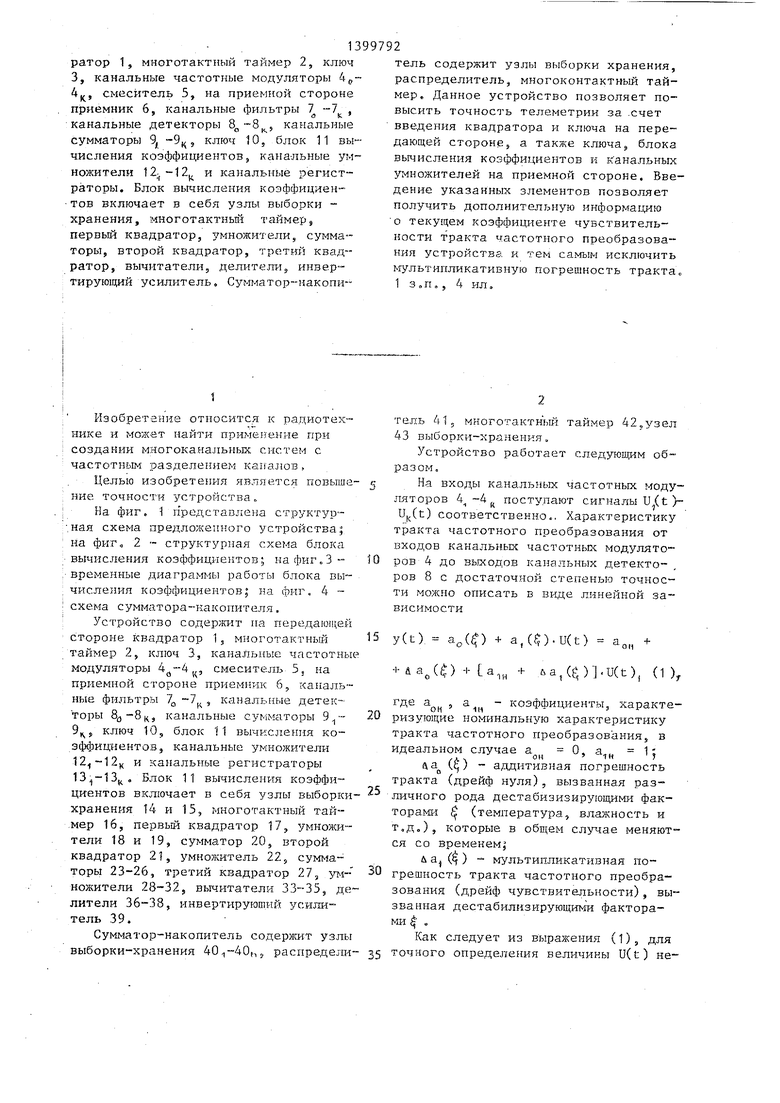

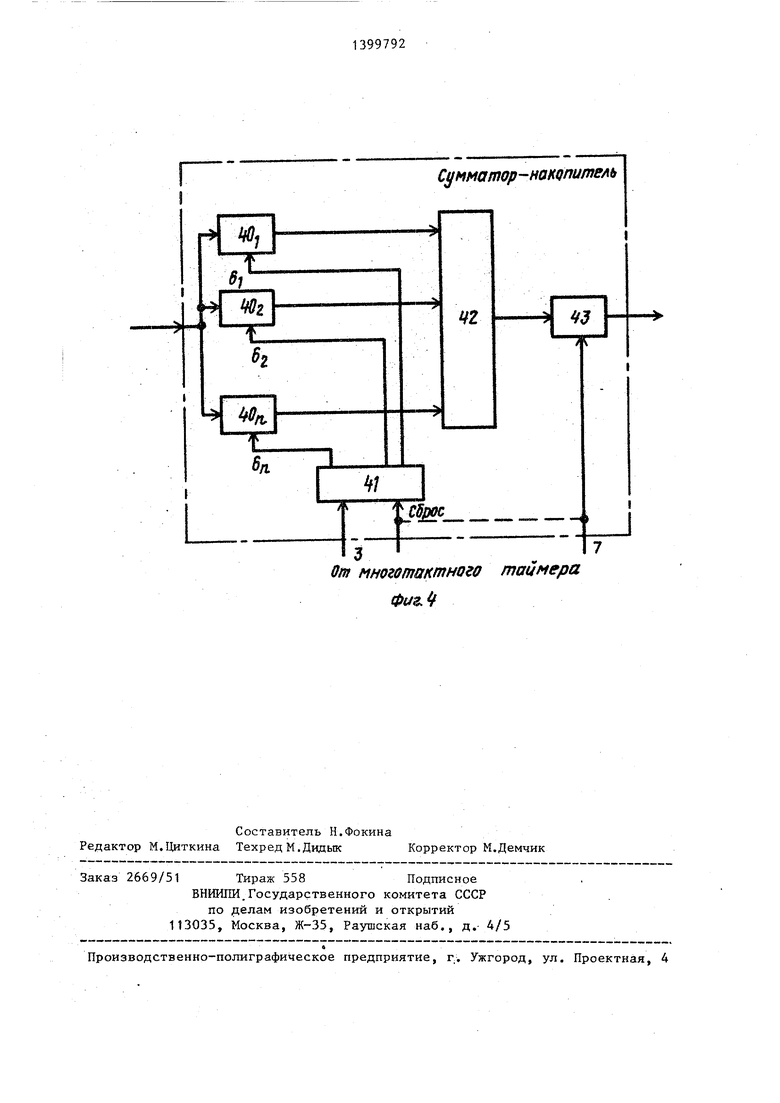

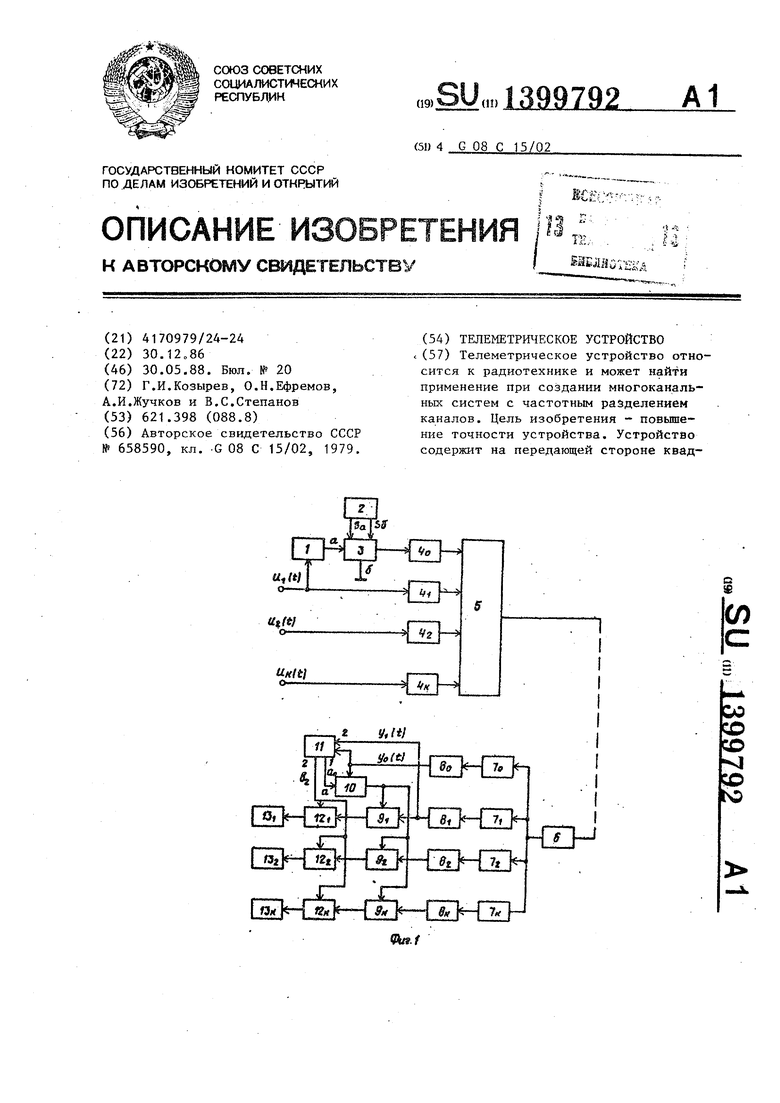

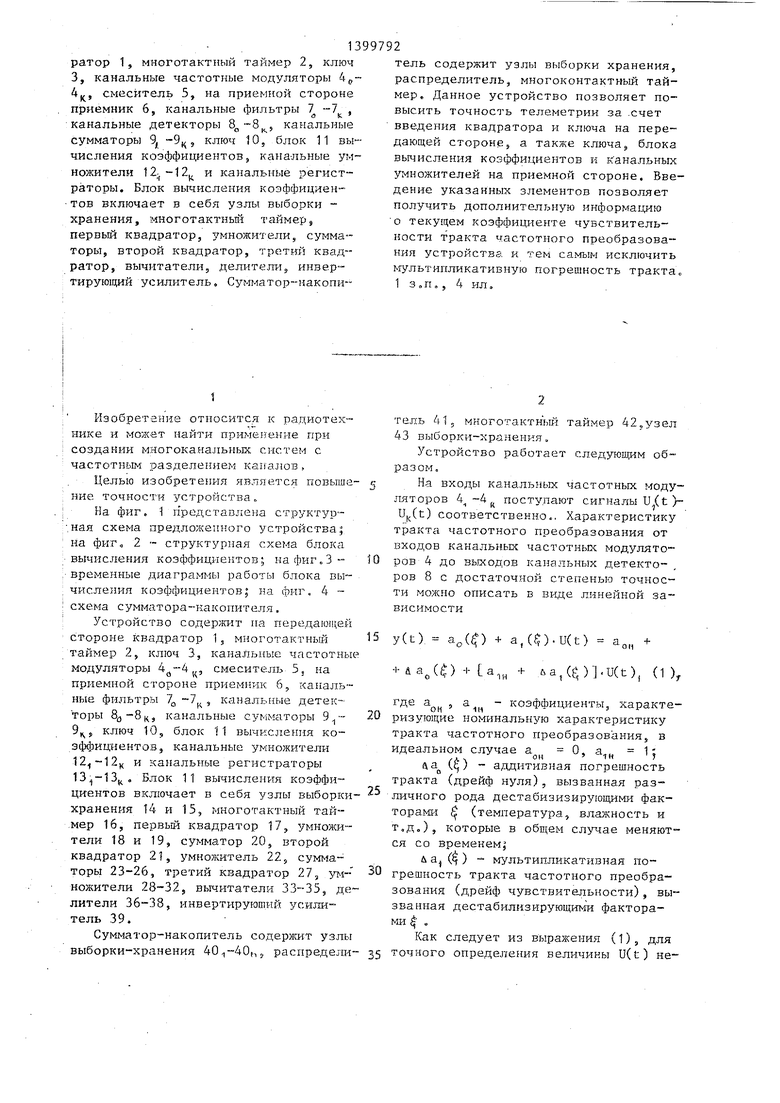

На фиг, 1 п редстав.чеиа структур™ ;нал схема предложенного устройства; на фиг, 2 - структурная схема блока вычисления коэффициентов; на фиг.3 - временные диаграммы работы блока вычисления коэффициентов; на фиг. 4 - схема сумматора-накопителя.

Устройство содер/кит на передающей стороне квадратор 1, многотактный таймер 2, ключ 3, канальные частотны модуляторы , смеситель 5. на приемной стороне приемник 6, канальные фильтры 7о -7 , канальные детекторы , канальные сумматоры ключ 10, блок 11 вычисления коэффициентов, канальные умножители и канальные регистраторы 13;,-13ц о Блок 11 вычисления коэффициентов включает в себя узлы выборхси хранения 14 и 15, многотактный тай- .мер 16, первый квадратор 17, умножители 18 и 19, сумматор 20, второй квадратор 21, умножитель 22, сумматоры 23-26, третий квадратор 27, уы ножители 28-32, вычитатели 33-35, делители 36-38, инвертируюший усилитель 39.

Сумматор-накопитель содержит узлы выборки-хранения 40i-40t, j распредели2

тель 41, многотактный таймер 42,узел 43 выборки-хранения.

Устройство работает следующим образом,

На входы канальных частотньж модуляторов 4 -4 j поступают сигналы U/t)- U|(t) соответственно.. Характеристику тракта частотного преобразования от входов канальных частотных модуляторов 4 до выходов канальных детекторов 8 с достаточной степенью точности мо.жно описать в виде линейной зависимости

y(t). а(О + a,(O-U(t) а„„ 4f-aa(O -i- а,, + ua/t;).U(t), {1 ),

где а

он

- коэффициенты, характеризующие номинальную характеристику тракта частотного преобразования, в идеальном случае а О, а 1

ft а () - аддитивная погрешность тракта (дрейф нуля), вызванная различного рода дестабизизирующими факторами (температура, влажность и т.До), которые в общем случае меняются со временем,

л а ( ) - мультипликативная погрешность тракта частотного преобразования (дрейф чувствительности), вызванная дестабилизирующими факторами „

Как следует из выражения (1), для

точного определения величины U(t) необходимо постоянно уточнять коэффициенты а() и а, () :

U(t) --- y(t) -- э.

а.

В

вход пает ра 1 .

положении а ключей 3 и 10 на

модулятора 4 посту- с выхода квадрато- Тогда на выходах канальных дечастотногосигнал U,{t)

(

тектьров чим

8. и 8

соответственно полуа.

a..

+ а, U;(t); -t- a/U, (t).

Выразив выражение

у (t) через у. (t), получим

y.,(t) Ь, + Ь,у, (t) + b,y(t), (4)

где b

+ -

Ъ -

Таким образом, вычислив параметры b., к Ъ выражения (4), можно определить коэффициенты а и а , с помощью (5) и, подставив их в (2), произвести точную оценку величины входного сигнала U(t) с учетом аддитивной и мультипликативной погрешности тракта частотного преобразования.

Коррекцию коэффициента чувствительности а обычно требуется производить периодически. Для упрощения постоянного учета дрейфа нуля в интервале между коррекциями коэффициен та а в схеме предлагаемого устройства предусмотрено положение б ключей 3 и 10. В этом случае учет аддитивной погрешности, т.е. коррекция коэффициента ЕО характеристики тракта частотного преобразования, осуществляется аналогично прототипу.

Работой ключа 3 управляет много- тактный таймер 2 с помощью попеременной подачи на управляющие входы ключа импульсов S сх и Sg. При подаче управляющего импульса S выход квадратора 1 подключается к входу канального частотного модулятора 4о т.е. на вход устройства поступает сигнал Uq ). При подаче на другой уп

10

равляю1Щ й вход ключа 3 импульса Sg- на вход частотного модулятора 4 поступает сигнал Ug 0. При условии, что U(t) О, в течение всего интер- вала измерения U Ug-, Данное неравенство используется для синхронной работы ключей 3 и 10 на приемной стороне. Сигнал y(t) с .выхода канального детектора 8.5 подается одновременно на сигнальный вход б ключа 10 и его управляющие входы. Если значв - ние у превышает некоторьй опйрный

находится в входы канальных сумматоров 9-9 ., поступает сигуровень и„, то ключ 10 5 положении а и на вторые

м

20

25

30

35

11.

Если у и

Qh 5 б

нал с выхода блока то ключ 10 находится в положении и на вторые входы канальных сумматоров поступает сигнал с выхода каналь кого детектора 8о , В качестве Unc можно взять сигнал, равный С U(t), где ) -априорное среднее значение сигнала U (t)| С - коэффициент пропорциональности, зависящий от вида и (t) и шумов в линии связи, О С 1.

В положении а ключей 3 и 10 коррекция аддитивной и мультипликативной погрешности тракта частотного преобразования осуществляется с помощью вычисления параметров Ь.,, b 2. в блоке 11 путем обработки результатов нескольких временных сечений X (t, ), y,(t, ), y(, y,(t.j),..., ), y(tj) методом наименыпих квадратов:

Q (t,,

0

t-т

ьл

+ ъ

О1

y;(t,)}

i- i

min

t,)(6)

При использовании указанного мето45

(7)

50

55

h

f-:T

2

y,(t, )i

Z, y;(t:.);

d:: ye(t,)z.;

(8)

1

y(t-); у (t, ) - результаты наблюдений сигналов УО (t ) и у (t) в моменты аремени t., 1 1,п.

Решая систему (7) относительно Ь и Ь-, находим

8,Т - V,T, bi -5-

,,

q т 2 Ч J. . J-,

На фиг. 2 представлена структурная блока 11 вычисления коэффицИен- T0B, осуществляюшего расчет парамет- р|)в Ь , и b(j согласно выражениям (9) И (10) с учетом обозначений (8), а коэффициента ао с помощью вы- р жения (5).

Блок вычисления коэффициентов ра- бфтает следуюищм образом.

Изменяющиеся во времени сигналы yKt) и y(t ) (см.временные диаграмма 1 и 2 на фиг. 3) поступают на из13997926

пителя 20, Принцип работы сумматоров- накопителей 20j 23-26 заключается в суммировании поступающих на них сигналов в моменты времени t-, ,п и хранении полученного суммарного сигнала до прихода следующей пачки из п последоватедьных импульсов и сигналов. Примерная структурная схе- JQ ма сумматора-накопителя, выполняющего указанные функции, представлена на

фиг. 4.

I

На управляющие входы узлов выборки-хранения 40 ,-40г, поступают сигна15 лы с распределителя 41 импульсов

(временные диаграммы на фиг.3). Учитывая принцип работы узлов 40,- 40 f, и вид поступаемых на ник сигналов, после окончания импульсов 3 (фиг. 3) в момент времени t на входах сумматора 3 будут дежурить сигналы с измерительного входа узлов , установившиеся в моменты времени tj, i , а на выходе сумматора 24 и на измерительном входе сумматора 25 - сумма этих сигналов, которая в момент подачи импульса 7 (фиг, 3) с многотактного таймера 42 (фиг. 4) считывается с вькода сумма30 тора 3 и хранится на выходе узла 43 выборки-хранения до прихода следующего импульса 7 через время п Т, . При использовании самоходного рас.- пределителя 41 импульсов (автопере(9)

(10)

20

25

мерительные входы узлов 14 и 15 выбс|рки-хранения. На управляюнще входы 5ключателя на схемах задержки) для

ydлoв 14 и 15 выборки-хранения посту-фазирования и управления работой

па|ют короткие импульсы с многоконтак-сумматора-накопителя достаточно

тн|ого таймера 16 длительностью 7 иимпульсов 7 (фиг. 3), задний

„фронт которых используется для

периодом Т, --- 1 (диаграмма 3 на 40установки распределителя импульфиг. 3). Выборка сигналов y(t) исходное состояние. При испольу (t) происходит в моменты временизовании тактового распределителя в

t , t,, ..., время действия им- естве тактовых импульсов могут

ПУЛЬСОВ. В остальное время сигналь:использоваться импульсы 3 (фиг. 3),

на вьпсоде узлов 14 и-15 сохраняют 5подаваемые на вход узлов 14 и 15 высвое значение, равное у„ (t ), у (t- ), -борки-хранения с многотактного тайме.- -;- 117ра 5 шиг.).

1 « 1,п на момент окончания импульса

На выходе сумматора-накопителя 20

) У (tj ). Сигнал с вы- - 1 , t

Т (диаграммы 4 и 3 на фиг. 3).

Дальнейшая работа блока 11 связа- 2) формируется сигнал S на с реализацией выражении (9), (10)

и (5) с учетом обозначений (8).п и о

Сигнал у (t) с выхода узла 14 поступает на вход квадратора 17 и из входов умножителей 18 и 19.

С выхода квадратора 17 сигнал, равный 55 хода умножителя 18, равный y(t) Z,-, Z. y(t;), поступает на вход квадра- поступает на вход сумматора-накопи- тора 21, а также на один из входов теля 23, на выходе которого после п умножителей 18, 19 и сумматора-нако- временных сечений t формируется сиг11 1

I - 1

На выходе сумматора-накопителя 20

2) формируется сигнал S ч

) У (tj ). Сигнал с вы1 , t

и о

I - 1

нал Т,

I -1

у, (t,)

С выхода

умножителя 19 сигнал, равный у(С ) Уц(с .), поступает на вход сумматора- накопителя 24, на выходе которого

792

Выходной сигнал умножителя 28, равньй S,T,, поступает на один из входов вычитателя 33, на другой вход которого подается сигнал , с выхода умножителя 32. Выходной сигнал вычитателя 33, равный - ,Т,, подается на первый вход делителя 37, с выхода которого сигнал, равный па

| название | год | авторы | номер документа |

|---|---|---|---|

| Телеметрическое устройство | 1989 |

|

SU1674200A2 |

| Многоканальное телеизмерительное устройство | 1986 |

|

SU1399798A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1387173A1 |

| Радиоимпульсный фазометр | 1984 |

|

SU1226330A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Устройство для вычисления дискретного спектра действительного временного ряда | 1974 |

|

SU525960A1 |

| Устройство для моделирования функций с помощью частных сумм сигналов Уолша | 1990 |

|

SU1741121A2 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

Телеметрическое устройство относится к радиотехнике и может найти применение при создании многоканальных систем с частотным разделением каналов. Цель изобретения - повышение точности устройства. Устройство содержит на передающей стороне квад

10

формируется сигнал S, (t-)y(t. ),

раметру

.

, поступаb - S2Yj-I §i Ti S,,T,j, - т, ет на выход блока 11 и на второй вход делителя 38, с выхода которого сигСи гнал с выхода квадратора 21, равный „ал, равный Ь,/Ь, подается на вход Z., подается на вход сумматора-нако- js инвертирующего усилителя 39. Выходной пителя 25, на выходе которого после сигнал с инвертирующего усилителя 39,

момента времени t формируется сиг -bl

нал Т л

Z.. Аналогичньм образом 20 ступает на выход блока вычисления

коэффициентов,

1 --1

формируется сигнал на выходе сумматора-накопителя 26, равный

Vi

i:yo(t,) z.

1-1

Работа блоков 27-39 (фиг.2) непосредственно связана с реализацией выражений (9), (10) и (5).

Сигналы S (2 с выхода сумматора-накопителя 20 и Т 2 с выхода сумматора- накопителя 25 подаются на вход умножителя 29, выходнойсигнал которого, равный , подается на один из входов вьгчитателя 35. На второй вход вы- читателя 35 подается сигнал с выхода квадратора 27, равный Т,. На выходе вычитателя 33 формируется сигнал

м

равньй знаменателю выражений (9) и (Ю), которьй подается на вторые входы делителей 36 и 37, на первые входы которых подаются сигналы, равные числителям выражений (9) и (10). Сигнал с выхода умножителя 31, равный S Т подается на второй вход вычитателя 34, на первь й вход которого поступает сигнал с выхода умножителя 30, равный V;,.,. Выходной сигнал вычитателя 34, равный S.,Tg - - V Т,, поступает на первьй вход делителя 36, с выхода которого сигнал,

, SiT2 - V,T,

равный параметру b ,

J-i

подается на один из входов делителя 38.

раметру

, поступаb - S2Yj-I §i Ti S,,T,j, - т, равньй коэффициенту а..

-bl

2b,

noступает на выход блока вычисления

коэффициентов,

Таким образом, блок 11 (фиг; 1) осуществляет расчет параметров Ь, и b 2 и коэффициента а. за п временных сечений t входных сигналов, ,п; п 3. При этом точность расчета величин b 2 и а повышается с ростом динамики сигналов y(t), yo(t) и, соответственно, сигнала U,(t) (фиг. 1), так как в этом случае увеличивается модуль знаменателя выражений (9) и (10), .Расстояние между временными сечениями выбирается из Условия, что за время (t, - t ,) коэффициент йд() и а,() практически не изменяются.

Рассчитанное в блоке 11 вычисления коэффициентов согласно (5) значение а через ключ 10 (положение а) поступает на вторые входы канальных сумматоров (фиг. 1), на первые входы которых поступают сигналы у (t) УJ.(t) с выходов канальных детекторов 8-8, С выходов канальных сумматоров сигналы, равные y.(t) - а , поступают на вторые входы канальных умножителей 12 .,-12 , на первые входы которых поступает величина j

-- с выхода блока 11. С выходов канальных умножителей сигна

лы, равные U(t) --- yj(t) - ,

i 1jk, т.е. с учетом коррекции дрейфа нуля и дрейфа чувствительности, поступают на входы канальных регистраторов 13,-13..

91399792

ормула изобретения 1, Телеметрическое устройство, соержащее на передающей стороне канальные частотные модуляторы выходы оторых соединены с соответствующими ходами смесителя, выход которого чеез линию связи на приемной стороне подключен к входу приемника, выход приемника соединен с входами каналь- ю ньк фильтров, выход каждого канального фильтра подключен к входу соответствующего канального детектора, выход каждого из которых, кроме первого, подключен к первому входу соответст- вующего канального сумматора, канальные регистраторы, отличающееся тем, что, с целью повышения точности устройства, в него введены на передающей стороне квадратор, мно-20 готактньй таймер и ключ, выход квадратора и вход второго канального частотного модулятора являются информационным входом устройства, выход квадратора соединен с первым входом 25 ключа, второй вход которого пойк лючен к шине нулевого потенциала, третий и четвертый входы ключа соединены соответственно с первым и вторым выходами многотактного таймера, выход ключа подключен к входу первого канального частотного модулятора, на приемной стороне - блок вычисления коэффициентов, ключ и группа умножителей, вых:од первого канального детектора соединен с первыми входами блока вычисления коэффициентов и ключа, второй вход блока вычисления коэффициентов подключен к выходу второго канального детектора, первый выход блока вычисления коэффициентов соединен с вторым входом ключа, выход которо- го подключен к вторьгм входам каналь- ных сумматоров, второй выход блока вычисления коэффициентов соединен с первыми входами умножителей, вторые входы которых подключены к выходам соответствующих канальных сумматоров, выходы умножителей соединены с соответствующими входами канальных регистраторов.

2о Устройство по П.1, отличающееся тем, что блок вычисления коэффициентов содержит узлы выборки-хранения, многотактный таймер, квадраторы, умножители, сумматоры, вь1читатели, делители и инвертирующий усилитель,, первые входы первого и второго узлов выборки-хранения явля30

35

40

45

50

ю в и о в в к т с вы в л т к т т с п п в ч в в и в к н с и п и в т в т н к

55

с х п х в л к т

0 5

0

5

0

5

0

0

ются соответственно первым и вторым входами блока, вторые входы первого и второго узлов выборки-хранения объединены и соединены с первым выходом многотактного таймера, второй выход которого подключен к первым входам первого, второго, третьего, четвертого и пятого сумматоров, выход первого узла выборки-хранения соединен с входом первого квадратора и первыми входами первого и второго умножителей, выход второго узла выборки-хранения подключен к второму входу второго умножителя и первому входу третьего умножителя, выход первого квадратора соединен с вторыми входами первого и третьего умножителей, первого сумматора и входом второго квадратора, выход первого умножителя подключен к второму входу второго сумматора, выход второго умножителя соединен с вторым входом третьего сумматора, выходы второго квадратора и третьего умножителя подключены соответственно к вторым входам четвертого и пятого сумматоров, выход первого сумматора соединен с первыми входами пятого и щестого умножителей, выход второго сумматора подключен к входу третьего квадратора и первым входам четвертого и седьмого умножителей, выход третьего сумматора соединен с вторым входом четвертого умножителя и первым входом восьмого умножителя, выход четвертого сумматора подключен к вторым входам пятого и восьмого умножителей, вькод пятого сумматора соединен с вторыми входами шестого и седьмого умножителей, выходы пятого умножителя и третьего квадратора подключены соответственно к первому и второму входам первого вычитателя, выходы четвертого и шестого умножителей соединены соответственно с первым и вторым входами второго вычитателя, выходы седьмого и восьмого умножителей соответственно подключены к первому и второму входам третьего

с первым входом первого делителя, выход второго вычитателя подключен к первому входу второго делителя, выход первого вычитателя соединен с вторыми входами второго и первого делителей, выход первого делителя подключен к первому входу третьего делителя, второй вход которого соединен

с выходом второго делителя, выход торого является первым выходом блока, третьего делителя подключен к входу выход второго делителя является вто- инвертирующего усилителя, выход ко- рым выходом блока.

От многотактного таймера Фа.

Сумматор-накопитель

| Телеметрическое устройство | 1977 |

|

SU658590A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-30—Подача