00

со

(О

00 о ;о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1300543A2 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1462406A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для программного управления намоточным станком | 1987 |

|

SU1451648A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1984 |

|

SU1265833A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано для вывода графической информации из ЭВМ. Цель изобретения - повьпиение быстродействия устройства - достигается введением счетчика 2 адреса, одновибра- торов 8 и 9 и соответствующих функциональных связей, а также выполнением распределителя 4 импульсов. В состав распределителя импульсов входят сдвигающий регистр, дешифратор, две групш элементов И, шесть элементов И и три триггера. Изобретение позволяет выполнять маскирование, перестановку и размножение частей изображения путем указания адресов модификации, за счет чего повьшаетс. быстродействие устройства при вьшоде графической информации. 1 з.п. ф-лы, 3 ил. с $ (Л

iO // 12 15 сраг.

Изобретение относится к вычислительной технике и автоматике и моясе быть использовано для вывода графической информации из ЭВМ.

Цель изобретения - повышение бысродействия устройства.

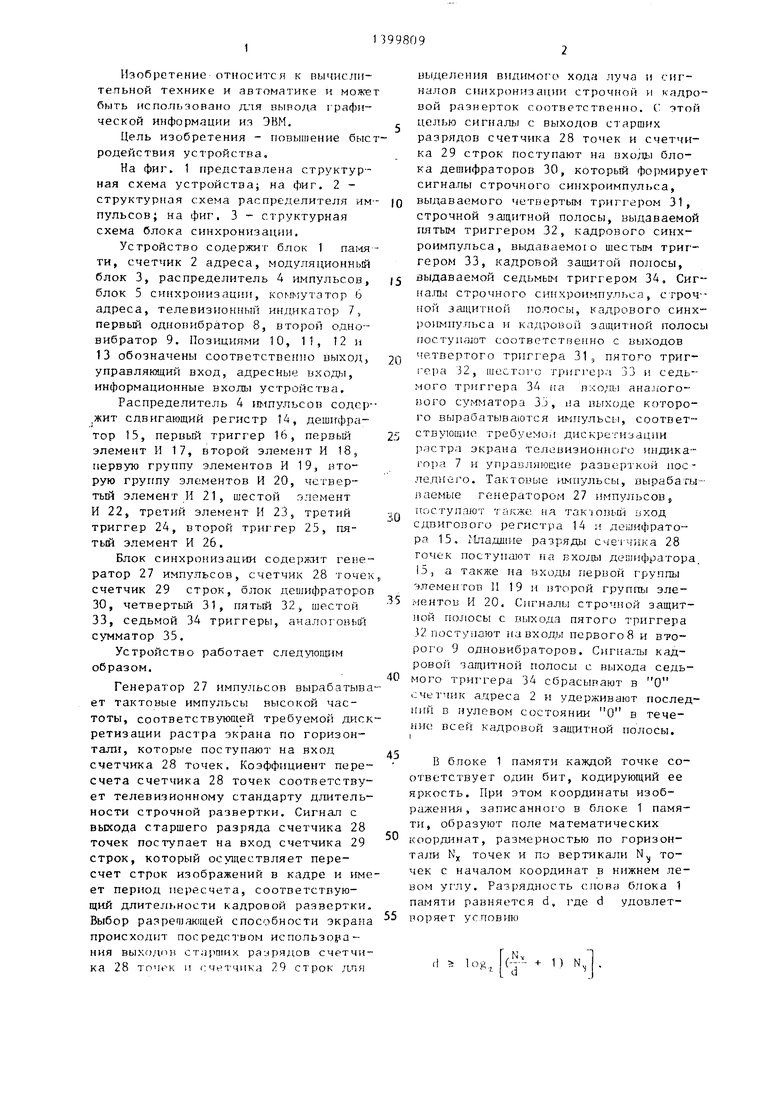

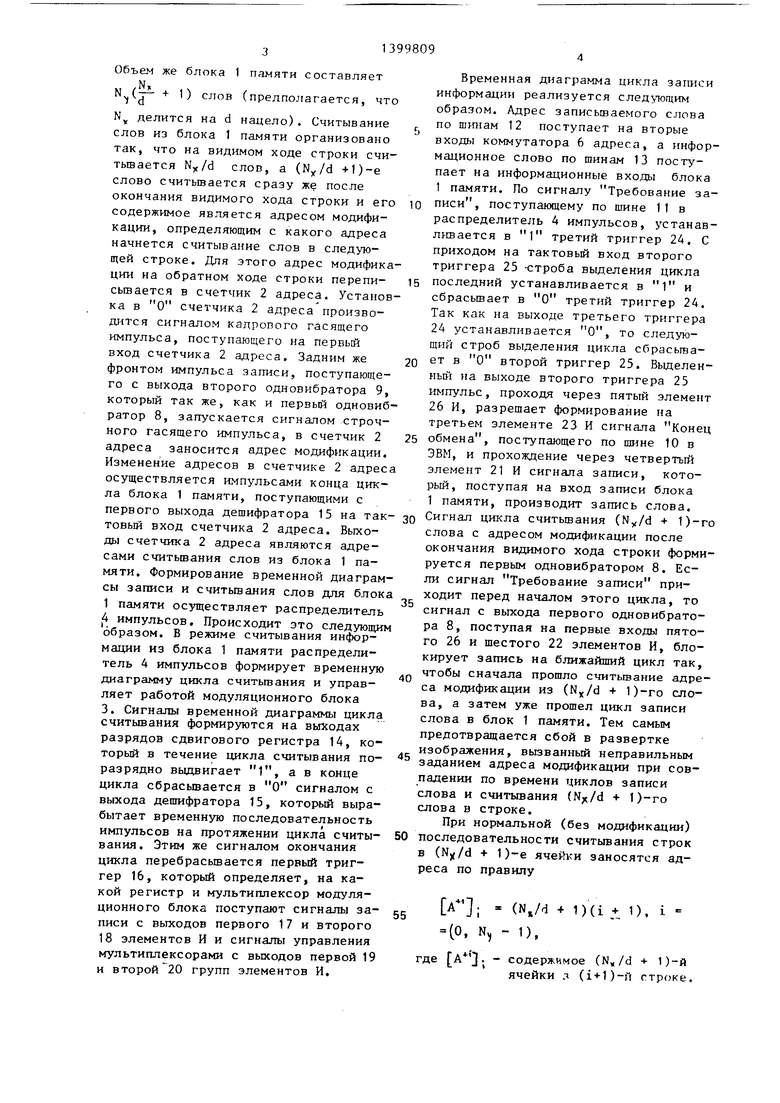

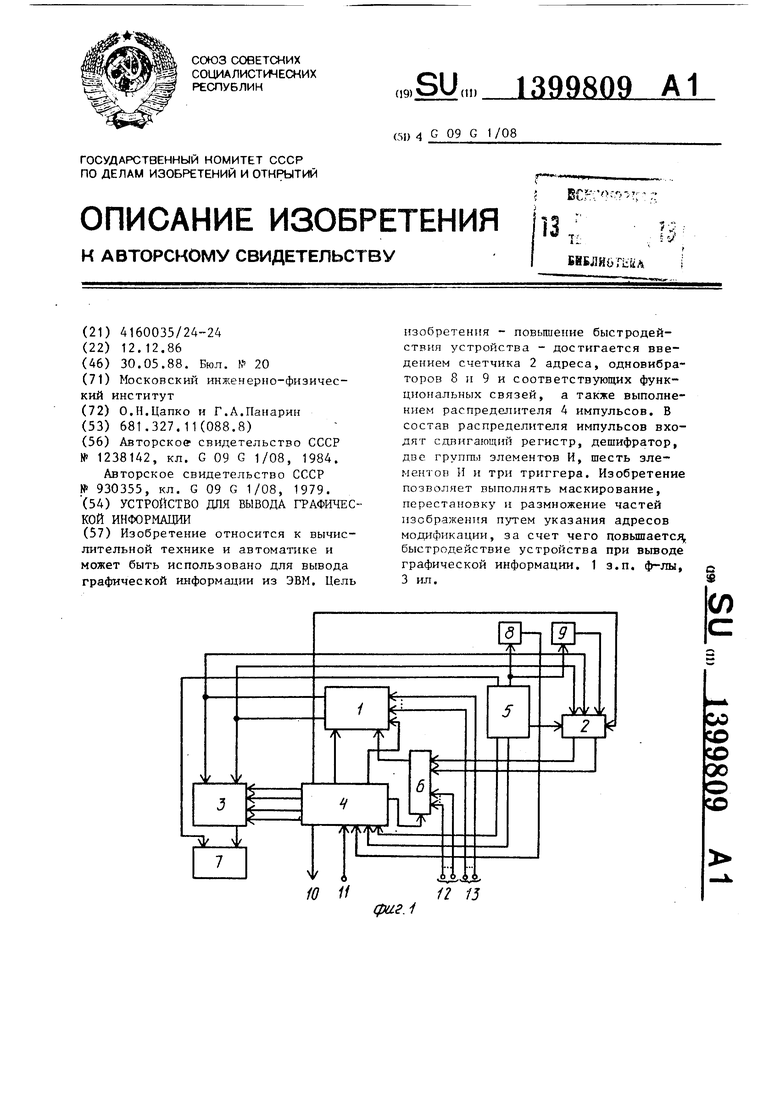

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема распределителя импульсов; на фиг, 3 - структурная схема блока синхронизации.

Устройство содержит блок 1 ти, счетчик 2 адреса, модуляционный блок 3, распределитель 4 импульсов, блок 5 синхронизации, коьп утатор 6 адреса, телевизионный индикатор 7, первый одновибратор 8, второй одно-вибратор 9. Позициями 10, 11, 12 и 13 обозначены соответственно выход, управляющий вход, адресные входы, информационные входы устройства.

Распределитель 4 импульсов содер,жит сдвигающий регистр 14, дешифратор 15, первый триггер 16, первьш элемент И 17, второй элемент И 18, первую группу элементов И 19, вторую группу элементов И 20, четвертый элемент И 21, шестой элемент И 22, третий элемент И 23, третий триггер 24, второй триггер 25, пятый элемент И 26.

Блок синхронизации содерж1гг генератор 27 импульсов, счетчик 28 точек счетчик 29 строк, блок дешифраторов 30, четвертый 31, пятый 32, шестой 33, седьмой 34 триггеры, аналогоньй сумматор 35.

Устройство работает следуютцим образом.

Генератор 27 импульсов вырабатывает тактовые импульсы высокой частоты, соответствующей требуемой дискретизации растра экрана по горизонтали, которые поступают на вход счетчика 28 точек. Коэффициент пересчета счетчика 28 точек соответствует телевизионному стандарту длительности строчной развертки. Сигнал с выхода старшего разряда счетчика 28 точек поступает на вход счетчика 29 строк, который осуществляет пересчет строк изображений в кадре и имеет период пересчета, соответствующий длител,ности кадровой развертки. Выбор разрешающей способности экрана происходит посредством использора- ния ВЫХОДИ} старших раурядов счетчика 28 точек и счетчика 29 строк для

5

0

выделения видимого хода луча и сигналов синхр(1низации строчной и кадровой разверток соответственно. ( этой . целью сигналы с выходов старших

разрядов счетчика 28 точек и счетчика 29 строк поступают на входа) блока дешифраторов 30, который формирует сигналы строчного си}1хроимпульса,

О выдаваемого четвертьм триггером 31, строчной защитной полосы, выдаваемой пятым триггером 32, кадрового синхроимпульса, выдаваемого шестым триггером 33, кадровой защитой полосы, выдаваемой седьмым триггером 34. Сиг- на.га; строчного синхроимпульса, строчной защитной полосы, кадрового синхроимпульса и клдрово защитной полосы поступают соответственно с выходов четвертого триггера 31 пятого триггера 32, шестого триггера 33 и седьмого триггера 34 на входы ана.1юго- вого cy fмaтopa 3j, на выходе которого вырабатываются импульсы, соответ5 ствующие требуемой дискретизации

растра экрана телевизионного индика- гора 7 ы управ.ая1ош,ие разверткой пос- леднв ч:). Тактовые импульсы, вырабатываемые генератором 27 импульсов,

, поступают также ня так юньй сдвигового регистра 14 и дешифратора 15, Младшие разряды сче 1чнка 28 точек поступшот на входы дешифратора 15., а такл(е на входы первой группы элементоп И 19 и второй группы эле5 ментов И 20, С 1гналы строчной защитной полосы с выхода пятого триггера 32 поступают на входы первого 8 и второго 9 одновибраторов. Сигналы кадровой защитной полосы с выхода седь0 мого триггера 34 сбрасывают в О

счетчик адреса 2 и удерживают последний в нулевом состоянии О в течение всей кадровой защитной полосы. I

, В блоке 1 памяти каждой точке соответствует один бит, кодирующий ее яркость. При этом координаты изображения, записанного в блоке 1 памяти, образуют поле математических координат, размерностью по горизонтали NX точек и по вертикали N точек с началом координат в нижнем левом углу. Разрядность слова блока 1 памяти равняется d, где d удовлет- 5 поряет условию

0

1 log 1(--.NV

ч- 1) N,

Объем же блока N,

1 памяти составляет + 1) слов (предполагается, что делится на d нацело). Считывание

(d

NV .

слов ИЗ блока 1 памяти организовано так, что на видимом ходе строки счи- тьшается слов, а ( +)-е слово считьшается сразу же после окончания видимого хода строки и его содержимое является адресом модификации, определяющим с какого адреса начнется считывание слов в следующей строке. Для этого адрес модификации на обратном ходе строки перепи- сьгоается в счетчик 2 адреса. Установка в О счетчика 2 адреса производится сигналом кадропого гасящего импульса, поступающего на первый вход счетчика 2 адреса. Задним же фронтом импульса записи, поступающего с выхода второго одновибратора 9, который так же, как и первый одновиб- ратор 8, запускается сигналом строчного гасящего импульса, в счетчик 2 адреса заносится адрес модификации. Изменение адресов в счетчике 2 адреса осуществляется импульсами конца цикла блока 1 памяти, поступающими с

Временная диаграмма цикла загаюи информации реализуется следующим образом. Адрес записываемого слова

J- по шинам 12 поступает на вторые

входы коммутатора 6 адреса, а информационное слово по шинам 13 поступает на информационные входы блока 1 памяти. По сигналу Требование за10 писи, поступающему по шине 11 в

распределитель 4 импульсов, устанав- Л1-тается в 1 третий триггер 24. С приходом на тактовьй вход второго триггера 25 -строба выделения цикла

15 последний устанавливается в 1 и сбрасьтает в О третий триггер 24. Так как на выходе третьего триггера 24 устанавливается О, то следую- щий строб выделения цикла сбрасьгеа20 ет в О второй триггер 25. Выделен- ньш на выходе второго триггера 25 импульс, проходя через пятый элемент 26 И, разрешает формирование на третьем элементе 23 И сигнала Конец

25 обмена, постгупающего по шине 10 в ЭВМ, и прохождение через четвертый элемент 21 И сигнала записи, который, поступая на вход записи блока 1 памяти, производит запись слова.

первого выхода дешифратора 15 на так- зо Сигнал цикла считьшания (Ny/d -ь 1)-го

товый вход счетчика 2 адреса. Выходы счетчика 2 адреса являются адресами считьшания слов из блока 1 памяти. Формирование временной диаграм- сы записи и считьшания слов для блока 1 памяти осуществляет распределитель |4 импульсов. Происходит это следующим образом. В режиме считывания информации из блока 1 памяти распределитель 4 импульсов формирует временную диаграмму цикла считьгаания и управляет работой модуляционного блока 3. Сигналы временной диаграммы цикла считывания формируются на выходах

разрядов сдвигового регистра 14, который в течение цикла считывания поII А (I

I 1

35

40

45

разрядно вьщвигает

а в конце

слова с адресом модификации после окончания видимого хода строки формируется первым одновибратором 8. Если сигнал Требование записи приходит перед началом этого цикла, то сигнал с выхода первого одновибратора 8, поступая на первые входы пятого 26 и шестого 22 элементов И, блокирует запись на ближайший цикл так, чтобы сначала прошло считьтание адреса модификации из ( + 1)-го слова, а затем уже прошел цикл записи слова в блок 1 памяти. Тем самым предотвращается сбой в развертке изображения, вызванный неправильным заданием адреса модификации при совпадении по времени циклов записи

цикла сбрасьгоается в О сигналом с выхода дешифратора 15, который выра- бытает временную последовательность импульсов на протяжении цикла считывания. Этим же сигналом окончания цикла перебрасьтается первый триггер 16, который определяет, на какой регистр и мультиплексор модуляционного блока поступают сигналь) записи с выходов первого 17 и второго 18 элементов И и сигналы управления мультиплексорами с выходов первой 19 и второй 20 групп элементов И.

Временная диаграмма цикла загаюи информации реализуется следующим образом. Адрес записываемого слова

по шинам 12 поступает на вторые

входы коммутатора 6 адреса, а информационное слово по шинам 13 поступает на информационные входы блока 1 памяти. По сигналу Требование записи, поступающему по шине 11 в

распределитель 4 импульсов, устанав- Л1-тается в 1 третий триггер 24. С приходом на тактовьй вход второго триггера 25 -строба выделения цикла

последний устанавливается в 1 и сбрасьтает в О третий триггер 24. Так как на выходе третьего триггера 24 устанавливается О, то следую- щий строб выделения цикла сбрасьгеает в О второй триггер 25. Выделен- ньш на выходе второго триггера 25 импульс, проходя через пятый элемент 26 И, разрешает формирование на третьем элементе 23 И сигнала Конец

обмена, постгупающего по шине 10 в ЭВМ, и прохождение через четвертый элемент 21 И сигнала записи, который, поступая на вход записи блока 1 памяти, производит запись слова.

5

0

5

слова с адресом модификации после окончания видимого хода строки формируется первым одновибратором 8. Если сигнал Требование записи приходит перед началом этого цикла, то сигнал с выхода первого одновибратора 8, поступая на первые входы пятого 26 и шестого 22 элементов И, блокирует запись на ближайший цикл так, чтобы сначала прошло считьтание адреса модификации из ( + 1)-го слова, а затем уже прошел цикл записи слова в блок 1 памяти. Тем самым предотвращается сбой в развертке изображения, вызванный неправильным заданием адреса модификации при совпадении по времени циклов записи

слова и считывания (N;t/d + 1)-го слова в строке.

При нормальной (без модификации) 50 последовательности считывания строк в (Ny/d + 1)-е ячейки заносятся адреса по правилу

55

- (N./ i

(0, N, - 1),

1)(i + О. i

где - содержимое (N,/d -4- 1)-й ячейки .т ()-й строке.

При изменении последовательности считывания строк, например, при модификации, начиная с j-й строки, достаточно все адреса модификации, начиная с j-ro слова сверху, изменить на константу модификации.

Предлагаемое устройство обеспечивает повышение быстродействия устройства для вывода графической информации, так как позволяет выполнят маскирование, перестановку и размножение частей изображения путем указания адресов модицикации в ( + + 1)-е ячейки блока 1 памяти без перегенерации модифицируемых фрагментов.

Формула изобретения

1, Устройство для вывода графической информации, содержащее блок памяти, модуляционный блок, телевизионный индикатор, распределитель импульсов, коммутатор адреса, блок синхронизации, выходы блока памяти соединены с информационными входами модуляционного блока, адресные входы блока памяти соединены с выходом коммутатора адреса, а управляюп1ие входы блока памяти соединены с первым и вторым выходами распределителя импульсов, выход модуляционного блок соединен с видеовходом телевизионного индикатора, управляющие входы модуляционного блока соединены с выходами группы распределителя импульсов, синхровход телевизионного индикатора соединен с первым выходом блока синхронизации, первый и второй синхровходы распределителя импульсов соединены с вторым и третьим выходами блока синхронизации, управляющий вход коммутатора адреса соединен с третьим выходом распределителя им- пульсов,отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик адреса, первый и второй одно вибраторы, информационные входы счет чика адреса соединены с выходами блока памяти, выходы счетчика адреса соединены с первыми информационными входами коммутатора адреса, управляющие входы счетчика адреса соеди- иены с четвертым выходом распределителя импульсов и выходом второго одновибратора соответственно, синхровход счетчика адреса соединен с

5

0

5

0

5 0 5 0 g

четвертым выходом блока синхронизации, входы одновибраторов соединены с пятым выходом блока синхронизации, выход первого одновибратора соединен с первым управляющим входом распределителя импульсов,второй управляющий вход распределителя импульсов является управлнюп4им входом устройства, вторые информационные входы коммутатора адреса являются адрес- ньми входами устройства, пятый выход распределителя импульсов является выходом сигнала Конец обмена устройства, информационные входы блока памяти являются информационными входами устройства.

Кдл 1

О т 5л. 28 Отдл27

8

элемента И является пятым выходом распределителя, вторые входы второго элемента И и элементов И второй группы соединены с прямым выходом первого триггера, выходы первого и второго элементов И и элементов И первой и второй групп являются груп пой выходов распределителя.

К Ьл.2

K§/iJ

10 КЬб

Ф1.2

Кдя.

f

Кдп

Фш

Ы ш g

N

/(.2 ,

Ф

Kdfl.7

| Устройство для вывода графической информации | 1984 |

|

SU1238142A2 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-12—Подача