(5 ) УСТРОЙСТВО ДЛЯ ВЫВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1986 |

|

SU1399809A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1300543A2 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1345240A1 |

| Устройство для вывода графической информации | 1984 |

|

SU1238142A2 |

| Устройство для вывода графической информации | 1984 |

|

SU1238143A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

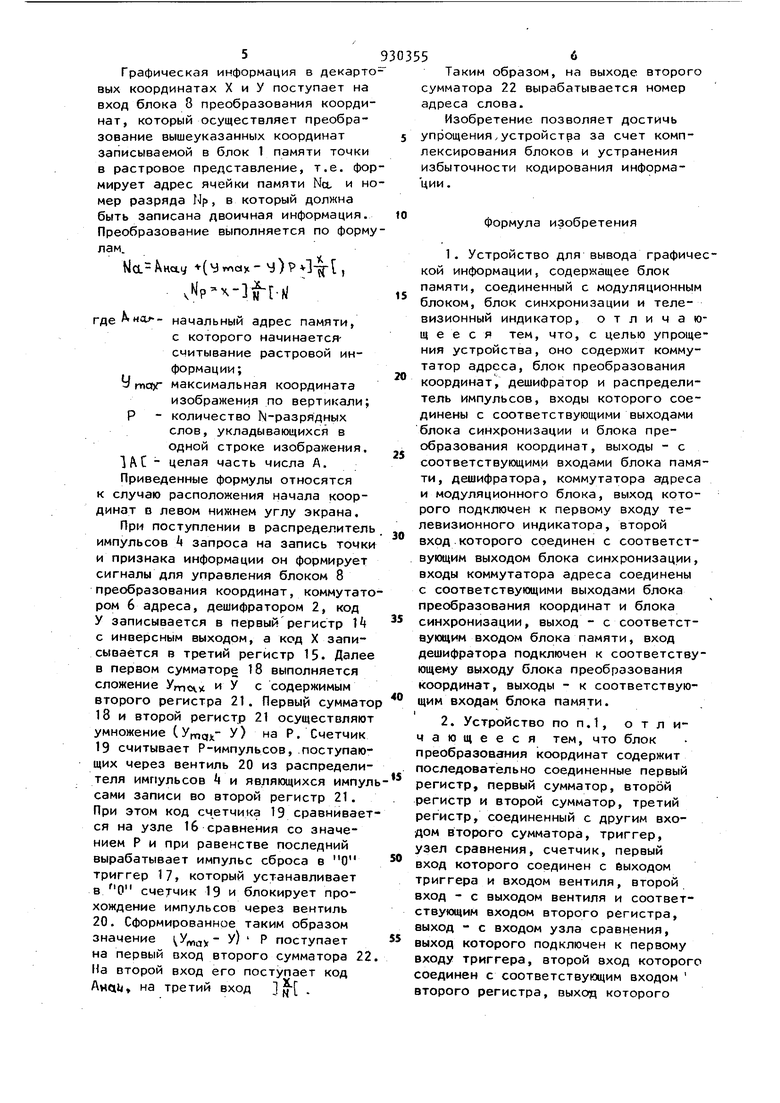

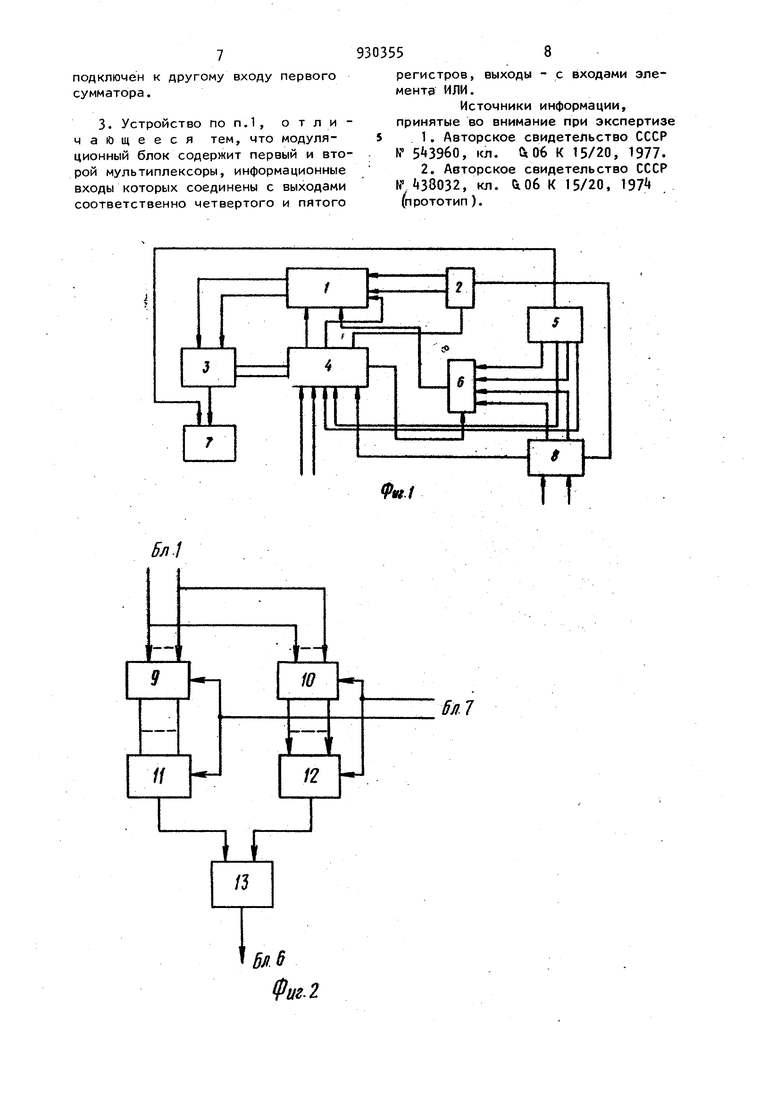

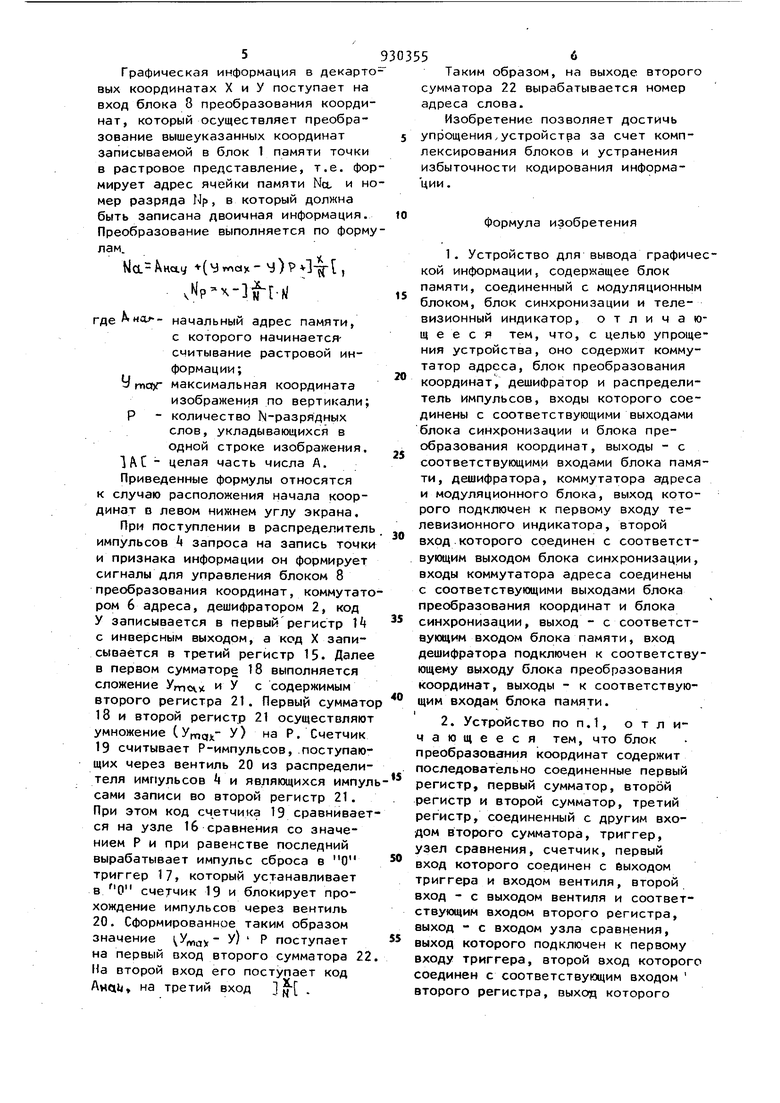

Изобретение относится к вычислительной технике и предназначено для вывода графической информации. Известно устройство для отображения графической информации, содержащее вычислительный блок; блоки формирования кадра изображения, блок памяти, блок коммутации и воспроизве дения информации, соединенных таким образом, что обеспечивается индикация на экране электронно-лучевой трубки графических черно-белых изобр жений D . Недостатком этого устройства является аппаратурная сложность. Наиболее близким техническим решением является устройство для вывода графической информации, содержащее блок памяти, соединенный с модуляционным блоком, блок синхронизации и телевизионный индикатор 2 . Недостатком этого устройства является большая аппаратурная сложность . Цель изобретения - упрощение устройства о . Поставленная цель .достигается тем, что устройство для вывода графической информации содержит коммутатор адреса, блок преобразования координат, дешифратор и распределитель импульсов, входы которого соединены с соответствующими выходами блока синхронизации и блока преобразования координат, выходы с соответствующими входами блока памяти, дешифратора, коммутатора адреса и модуляционного блока, выход которого подключен к первому входу телевизионного индикатора, второй вход которого соединен с соответствующим выходом блока синхронизации, входы коммутатора адреса соединены с соответствующими выходами блока преобразования координат и блока синхронизации выход - с соответствующим входо блока памяти, вход дешифратора подключен к соответствующему выходу блока пре образования координат, выходы - к соответствующим входам блока памяти. Блок преобразования координат содержит последовательно соединенные первый регистр, первый сумматор, второй регистр и второй сумматор, третий регистр, соединенный с другим входом второго сумматора, триггер, узел сравнения, счетчик, первый вход которого соединен с выходом триггера и входом вентиля, второй вход -с выходом вентиля и соответствующим В ХОДОМ второго регистра, выход - с входом узла сравнения, выход которого подключен к первому входу триггера, второй вход которого соединен с соответствующим входом второго регистра, выход которого подключен к другому входу первого сумматора„ Модуляционный блок содержит первый и второй мультиплексоры, информационные входы которых соединены с выходами соответственно четвертого и пятого регистров, выходы с входами элемента ИЛИ. На фиг.1 представлена блок-схема устройства; на фиг, 2 J 3 - функциональные схемы модуляционного блока и блока преобразования координат соответственно. Устройство содержит блок 1 памят дешифратор 2, модуляционный блок 3, распределитель импульсов, блок 5 синхронизации, коммутатор 6 адреса, телевизионный индикатор 7, блок 8 преобразования координат, четвертый регистр 9, пятый регистр 10, первый мультиплексор 11, второй мул типлексор 12, элемент ИЛИ 13, первь1Й- регистр 14, третий регистр 15, узел сравнения 16, триггер 17, первый сумматор 18, счетчик 19, вентил 20, второй регистр 21 и второй сумматор 22. Устройство работает следук-щим образом. Блок 5 синхронизации вырабатывает импульсы, соответствующие требуемой дискретизации растра экрана телевизионного индикатору 7 и управ ления разверткой последнего. Эти импульсы поступают на распределитель импульсов, осуществляя его временную привязку к телевизионному синхросигналу. Считывание информации из блока памяти 1 осуществляется следующим образом. 8 режиме считывания по сигналу из распределителя t импульсов коммутатор адреса 6 подключает выходы блока 5 синхронизации к адресным входам блока 1 памяти, которые вырабатывают адреса считываемых ячеек из блока 1 памяти о Одновременно с этим распределитель t импульсов, управля.ющий записью и считыванием информации из блока 1 памяти, формирует временную диаграмму цикла считывания. При подаче на блок 1 памяти всех вышеуказанных сигналов с его выхода поступает информация для записи в четвертый и пятый регистры 9 и 10 модуляционного блока 3- За один кадр осуществляется считывание всего блока 1 памяти.. В блоке 1 памяти каждой точке экрана телевизионного индикатора 7 соответствует один бит, а высвечивание точки на экране происходит при записи в соответствующий бит блока памяти единичной информации. Блок 1 памяти организован в виде N-разрядных слов с возможностью выборочной записи в любой разряд слова, который выбирается при записи дешифратором 2 по номеру требуемого разряда Np, выдаваемого третьим регистром 15 блока 8 преобразования координат. Считываемые из блока 1 памяти слова поочередно записываются в четвертый и пятый регистры 9 и 10. Формирование видеосигнала осуществляется последовательным опросом разрядов упомянутых регистров 9 и 10 первым и вторым мультиплексорами 11 и 12. При этом в интервале опроса четвертого регистра 9 в пятый регистр 10 производится запись следующего слова из блока 1 памяти, а соответствующий записываемому регистру мультиплексор блокируется. После окончания опроса происходит обратная процедура - в четвертый регистр 9 записывается слово из блока 1 памяти, а пятый регистр 10 опрашивается вторым мультиплексором 12. Сигналы с выходов мультиплексоров 11 и 12 проходят через элемент ИЛИ 13 и образуют видеосигнал, который подается на вход видеоусилителя телевизионного индикатора 7. Графическая информация в декарто вых координатах X и У поступает на вход блока 8 преобразования координат, который осуществляет преобразование вышеуказанных координат записываемой в блок 1 памяти точки в растровое представление, т.е. фор мирует адрес ячейки памяти Net и но мер разряда NP, в который должна быть записана двоичная информация. Преобразование выполняется по форму лам. М(1 нау ( У с1х - S ) Р -|-1 , X-llr-fi Mp-v-T i начальный адрес памяти, с которого начинаетсясчитывание растровой информации;У mcv максимальная координата изображения по вертикали; Р - количество N-разрядных слов, укладывающихся в одной строке изображения. 1 Л С - целая часть числа А. Приведенные формулы относятся к случаю расположения начала координат о левом нижнем углу экрана. При поступлении в распределител I импульсов ч запроса на запись точк и признака информации он формирует сигналы для управления блоком 8 преобразования координат, коммутато ром 6 адреса, дешифратором 2, код У записывается в первый регистр 14 с инверсным выходом, а код X записывается в третий регистр 15. Далее в первом сумматоре 18 выполняется сложение и У с содержимым второго регистра 21. Первый суммато 18и второй регистр 21 осуществляют умножение (Утрх У) на Р. Счетчик 19считывает Р-импульсов, поступающих через вентиль 20 из распределителя импульсов k и являющихся импул сами записи во второй регистр 21. При этом код счетчика 19 сравнивает ся на узле 16 сравнения со значением Р и при равенстве последний вырабатывает импульс сброса в О триггер 17, который устанавливает в О счетчик 19 и блокирует прохождение импульсов через вентиль 20. Сформированное таким образом значение У«,ау- У) Р поступает на первый вход второго сумматора 22 На второй вход его поступает код на третий вход J- . Таким образом, на выходе второго сумматора 22 вырабатывается номер адреса слова. Изобретение позволяет достичь упрощения.устройства за счет комплексирования блоков и устранения избыточности кодирования информации. Формула изобретения 1.Устройство для вывода графической информации, содержащее блок памяти, соединенный с модуляционным блоком, блок синхронизации и телевизионный индикатор, отличающееся тем, что, с целью упрощения устройства, оно содержит коммутатор адреса, блок преобразования координат, дешифратор и распределитель импульсов, входы которого соединены с соответствующими выходами блока синхронизации и блока преобразования координат, выходы - с соответствующими входами блока памяти, дешифратора, коммутатора адреса и модуляционного блока, выход которого подключен к первому входу телевизионного индикатора, второй вход которого соединен с соответствующим выходом блока синхронизации, входы коммутатора адреса соединены с соответствующими выходами блока преобразования координат и блока синхронизации, выход - с соответствующим входом блока памяти, вход дешифратора подключен к соответствующему выходу блока преобразования координат, выходы - к соответствующим входам блока памяти. 2.Устройство по П.1, отличающееся тем, что блок преобразования координат содержит последовательно соединенные первый регистр, первый сумматор, второй регистр и второй сумматор, третий регистр, соединенный с другим входом второго сумматора, триггер, узел сравнения, счетчик, первый вход которого соединен с выходом триггера и входом вентиля, второй вход - с выходом вентиля и соответствующим входом второго регистра, выход - с входом узла сравнения, выход которого подключен к первому входу триггера, второй вход которого соединен с соответствующим входом второго регистра, выход которого

подключен к другому входу первого сумматора.

регистров, выходы - с входами элемента ИЛИ,

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР N , кл. U06 К 15/20, 1977.

(прототип).

IT

«1

6л. 7

:

X .

il

Sb

t

Ч:

.

Авторы

Даты

1982-05-23—Публикация

1979-07-09—Подача