4 СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1986 |

|

SU1399809A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1462406A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1399811A1 |

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

| Устройство для вывода графической информации | 1982 |

|

SU1078450A2 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Устройство для вывода графической информации | 1983 |

|

SU1150643A1 |

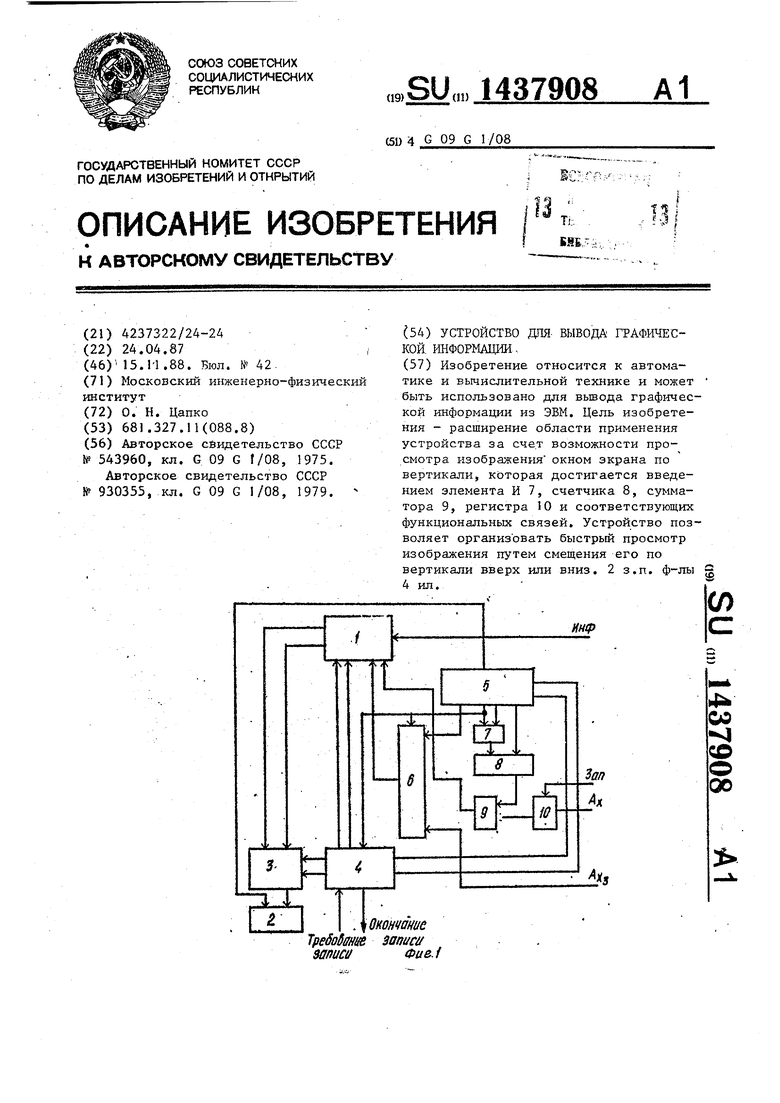

Изобретение относится к автоматике и вычислительной технике и может быть использовано для вьшода графической информации из ЭВМ. Цель изобретения - расширение области применения устройства за счет возможности просмотра изображения окном экрана по вертикали, которая достигается введением элемента И 7, счетчика 8, сумматора 9, регистра 10 и соответствующих функциональных связей. Устройство позволяет организовать быстрый просмотр изображения путем смещения его по вертикали вверх или вниз. 2 з.п. ф-лы Ц 4 ил. с (Л с:

Tpeffofffm запиа/ записа 0ue.f

Изобретение относится к автоматике .и вычислительной технике и предназначено для вывода информации из ЭВМ.

Цель изобретения - расширение области применения устройства путем обеспечения возможности просмотра изображения окном экрана по вертикали.

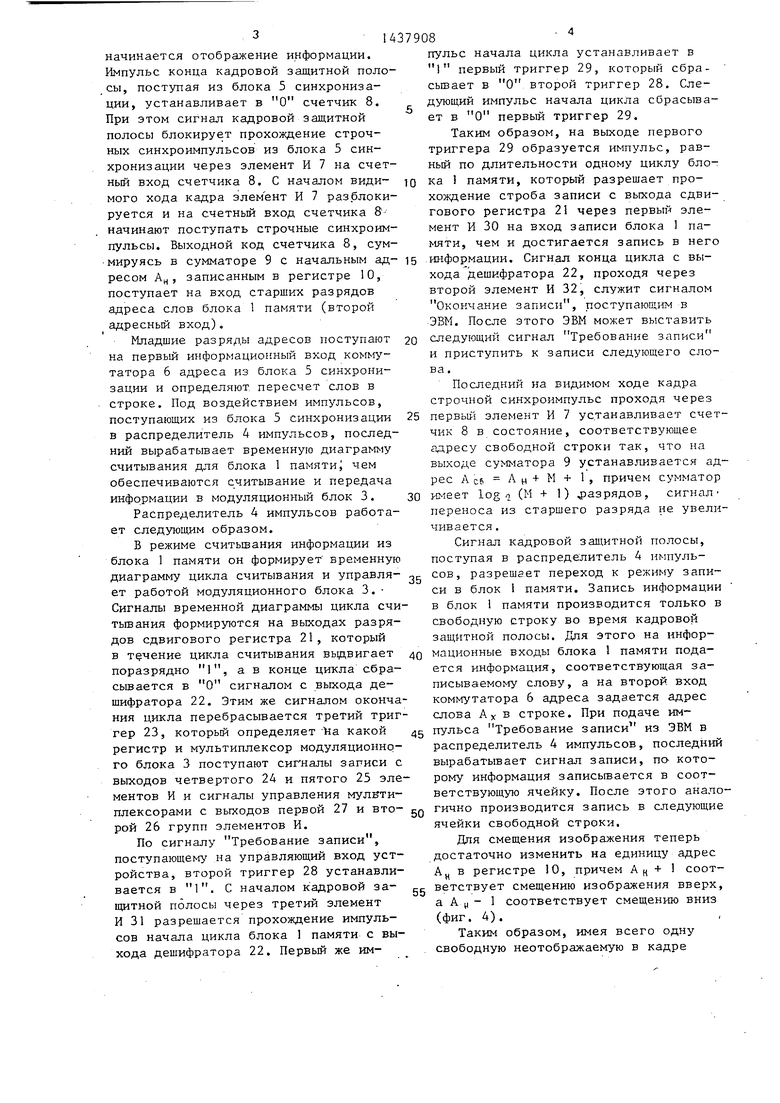

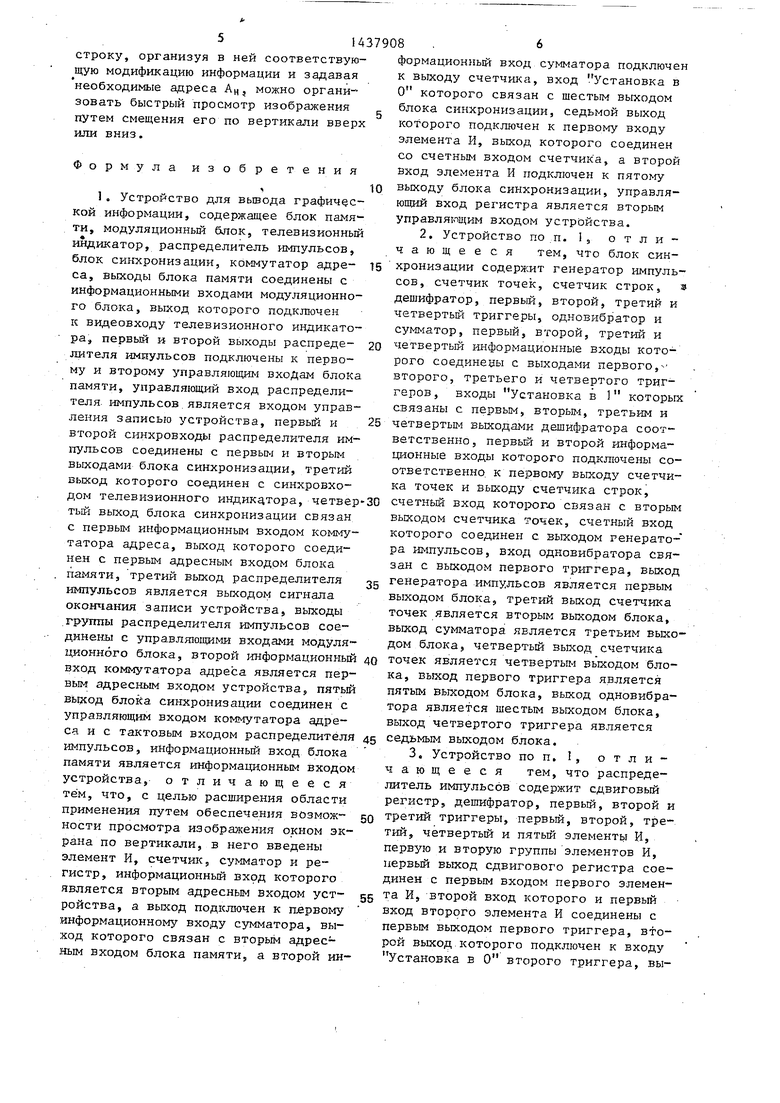

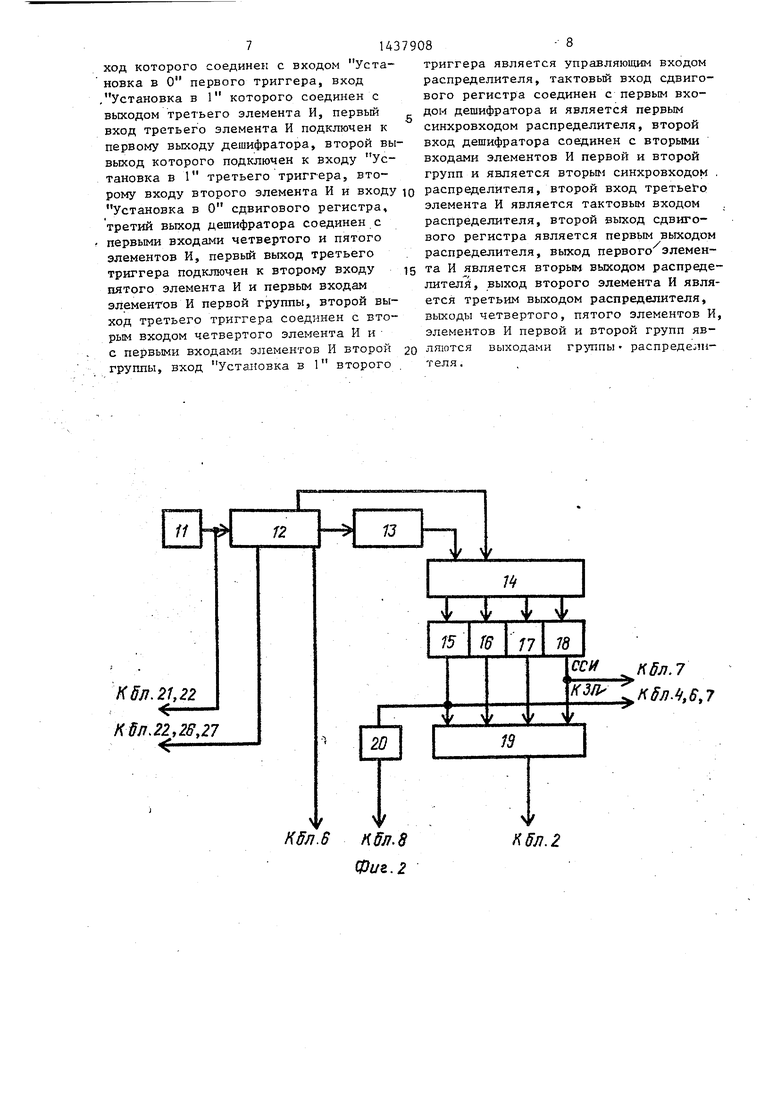

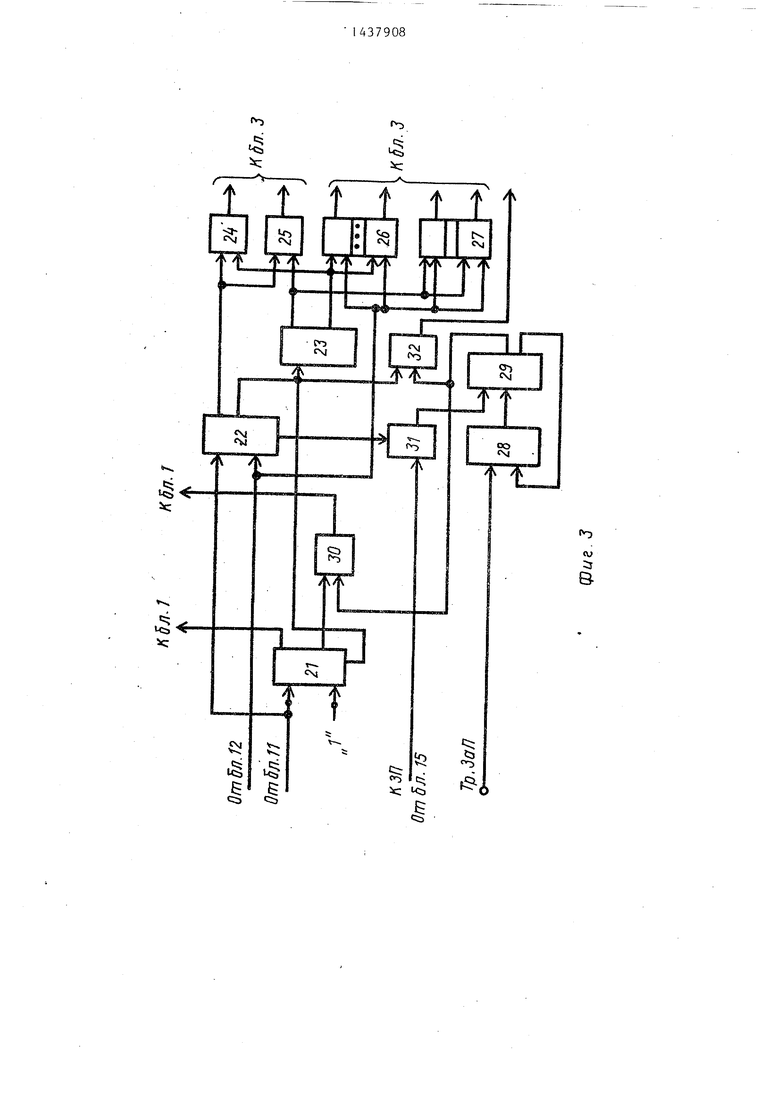

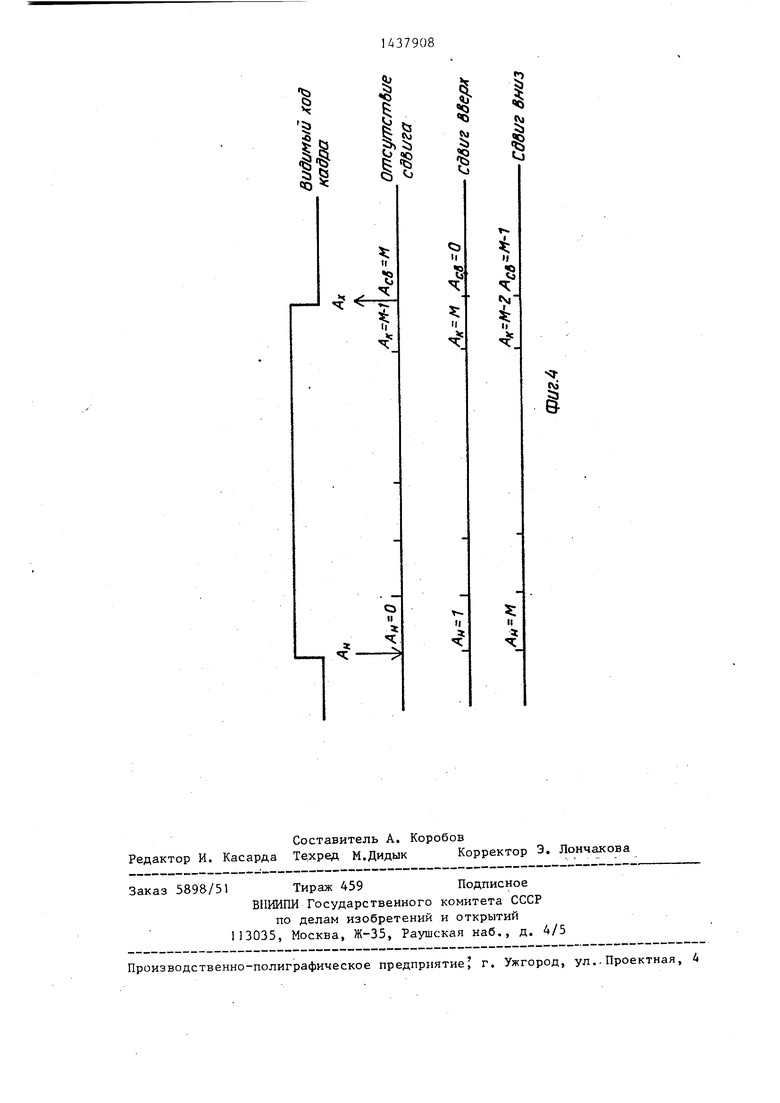

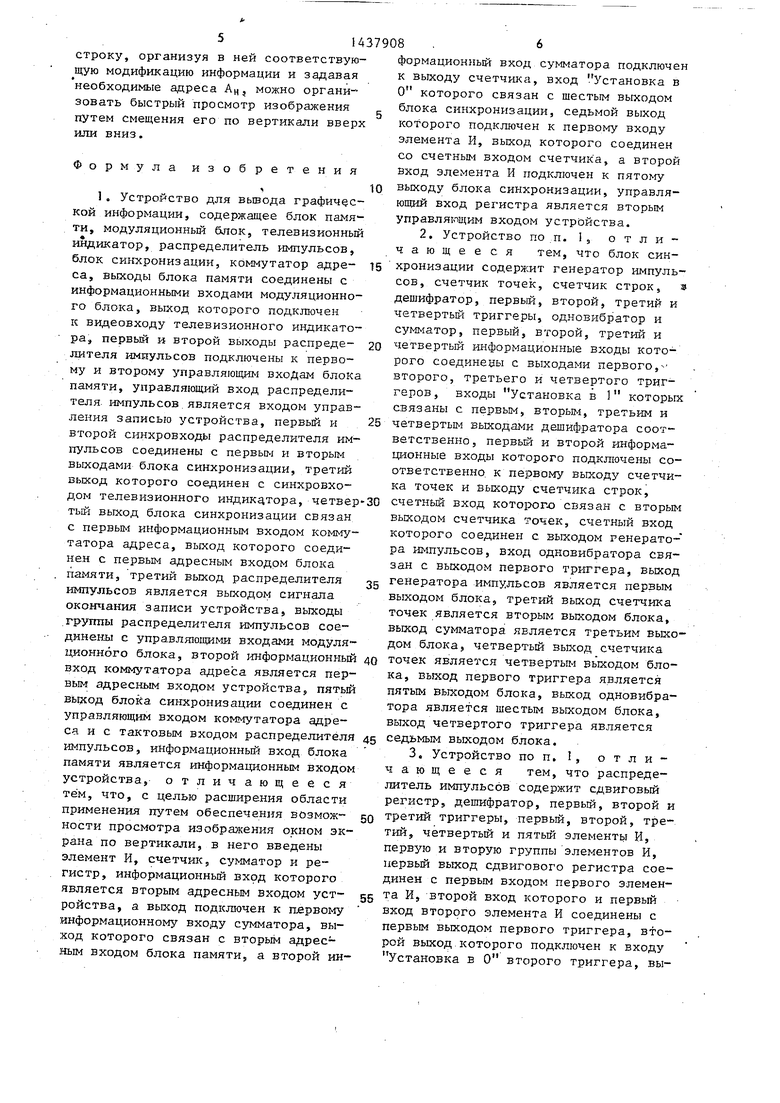

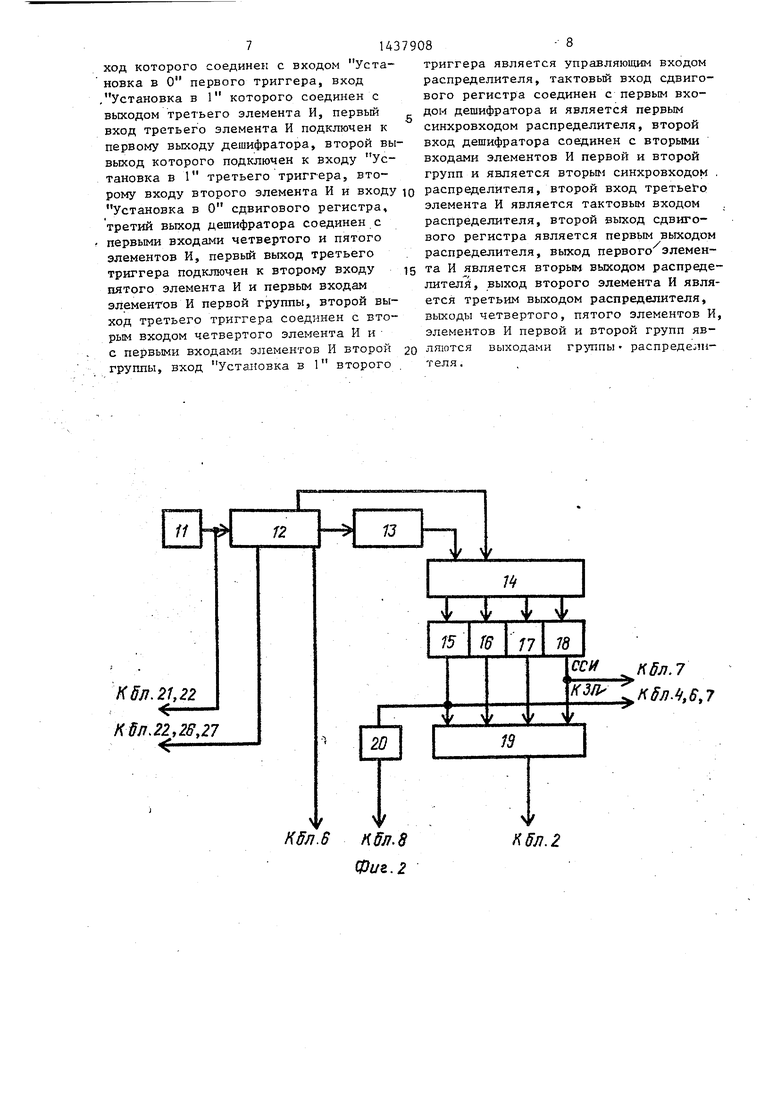

На фиг. 1 представлена структурная схема устройства; на фиг 2 - синхронизация; на фиг. 3 - структурная схема распределителя импульсов; на фцг„ 4 - изменение адресов считывания информации из блока памяти при сдвиге изображения вверх или вниз.

Устройство содержит блок памяти, телевизионный индикатор 2, модуляционный блок 3, распределитель 4 импульсов, блок 5 синхронизации, KOMi-iy- татор 6 адреса, элемент И 7, счетчик 8, сумматор 9, регистр 10.

Блок .синхронизации содержит генера тор П импульсов, счетчик 12 точек, счетчик 3 строк, дешифраторы 14, пер вьш триггер 15, второй триггер 16, третий триггер 17, четвертый триггер 18, сумматор 19, одновибратор 20.

Распределитель импульсов содержит сдвиговый регистр 21, дешифратор 22, третий триггер 23, четвертый элемент И 24, пятый элемент.И 25, вторую груп пу элементов И 26, первую группу элементов И 27J второй триггер 28, пер- 9ьй триггер 29, первый элемент И 30, трет1-ш элемент И 31, второй элемент И 32.

Устройство работает следующим обра зон.

Генератор 1 импульсов формирует импульсы высокой частоты, соответствующей требуемой, дискретизации растра экрана по горизонтали, которые поступают на счетный вход счетчика 12 точек. Коэффициент пересчета счетчика 12 точек соответствует телевизионному стандарту длительности строчной развертки. Сигнал с выхода старшего разряда счетчика 12 точек поступает на счетный вход счетчика 13 строк, который осуществляет пересчет строк изображения в кадре и имеет дериод пересчета, соответствующий длительности кадровой развертки. Сигналы с выходов счетчика 12 точек и счетчика 13 строк поступают на информационные вхо ды дешифратора 14.

Дешифратор 14 вырабатывает управляющие сигналы переброса первого 1-5, второго 16, третьего 17 и четвертого

0

5

0

5

0

5

0

5

0

5

18 триггеров. Первый триггер 15 формирует сигналы кадровых защитных полос; второй триггер 16 вырабатывает кадровые импульсы; третий триггер 17 - сигналы строчных зашитных полос; четвертый триггер формирует строчные синхроимпульсы. Полученные таким образом компоненты телевизионной синхросмеси преобразуются сумматором 19 в стандартный синхросигнал, который поступает на синхровход телевизионного индикатора 2,

Тактовые импульсы с выхода генератора 11 импульсов поступают на такто- вход сдвигового регистра 2Ь и пер-® вый вход дешифратора 22. Выходы младших разрядов счетчика 12 точек-поступают на второй вход дешифратора 22 и на вторые, входы первой 27 и второй 26 групп элементов И..

Строчные синхроимпульсы с выхода четвертого триггера 18 поступают на первый вход элемента И 7, на второй вход которого подаются импульсы кадровой защитной полосы с выхода первого триггера 15. Кроме-того, импульсы кадровой защитной полосы подаются на управляющий вход коммутатора 6 адреса, на второй вход третьего элемента И 31 и на вход одновибратора 20, который формирует имт льс сброса в О счетчика 8. Выходы старших разрядов счетчика 12 точек являются м,падшими разрядами адресрв считывания CJIOB из блока 1 памяти и пересчитьшают число слов, укладывающихся в строке изображения.

В блоке 1 памяти каждой точке экрана соответствует один бит, а высве- чивание точкр) на экране происходит при записи единицы в соответствующий бит блока 1 памяти. Последний организован в виде К-разрядны : слов, причем в одной строке изображения укладывается 2 слов. Bcei o же на экране размещается М строк изображения. В блоке 1 памяти хранится информация об М-1 строке изображения, причем вая строка на экране не отображается и является свободной. Счетчик 8 адресов строк изображения имеет коэффициент пересчета М + 1 и является двоичным счетчиком.

Считывание информации из блока 1 памяти осуществляется следующим образом.

Из ЭВМ в регистр 10 заносится адрес АН начальной строки, с которой

начинается отображение информации. Импульс конца кадровой защитной полосы, поступая из блока 5 синхронизации, устанавливает в О счетчик 8. При этом сигнал кадровой защитной полосы блокирует прохождение строчных синхроимпульсов из блока 5 синхронизации через элемент И 7 на счетный вход счетчика 8. С началом видимого хода кадра элемент И 7 разблокируется и на счетный вход счетчика 8- начинают поступать строчные синхроимпульсы. Выходной код счетчика 8, сум- мируясь в сумматоре 9 с начальным ад- ресом АИ, записанным в регистре 0, поступает на вход старших разрядов адреса слов блока 1 памяти (второй адресный вход),

Младшие разряды адресов поступают на первый информационный вход коммутатора 6 адреса из блока 5 синхронизации и определяют пересчет слов в строке. Под воздействием импульсов, поступающих из блока 5 синхронизации в распределитель 4 импульсов, последний вырабатывает временную диaгpa мy считывания для блока 1 памятиi чем обеспечиваются считывание и передача информации в модуляционный блок 3.

Распределитель 4 импульсов работает следующим образом.

В режиме считывания информации из блока 1 памяти он формирует временную диаграмму цикла считывания и управляет работой модуляционного блока 3. Сигналы временной диаграммы цикла счи тьшания формируются на выходах разря

дов сдвигового регистра 21, который в течение цикла считывания вьщвигает поразрядно 1, а в конце цикла сбра- сьшается в О сигналом с выхода дешифратора 22. Этим же сигналом окончания цикла перебрасывается третий триггер 23, который определяет tia какой регистр и мультиплексор модуляционного блока 3 поступают сигналы записи с выходов четвертого 24 и пятого 25 элементов И и сигналы управления мультиплексорами с выходов первой 27 и второй 26 групп элементов И.

По сигналу Требование записи, поступающему на управляющий вход устройства, второй триггер 28 устанавливается в 1. С началом к адровой защитной полосы через третий элемент И 31 разрешается прохождение импульсов начала цикла блока 1 памяти с выхода дешифратора 22. Первый же им

10

15

37908

пульс начала цикла устанавливает в 1 первый триггер 29, который сбра- сьшает в О второй триггер 28. Следующий импульс начала цикла сбрасывает в О первый триггер 29.

Таким образом, на вькоде первого триггера 29 образуется импульс, равный по длительности одному циклу блока 1 памяти, который разрешает прохождение строба записи с выхода сдвигового регистра 21 через первый элемент И 30 на вход записи блока 1 памяти, чем и достигается запись в него информации. Сигнал конца цикла с выхода дешифратора 22, проходя через второй элемент И 32, служит сигналом Окончание записи, поступающие в ЭВМ. После этого ЭВМ может выставить следующий сигнал Требование записи и приступить к записи следующего слова.

Последний на видимом ходе кадра строчной синхроимпульс проходя через первьш элемент И 7 устанавливает счетчик 8 в состояние, соответствующее адресу свободной строки так, что на выходе сумматора 9 устанавливается ад20

25

рес А се. А ц + М + 1 , причем сумматор имеет log-1 (М + 1) эазрядов, сигнал переноса из старшего разряда не увеличивается .

Сигнал кадровой защитной полосы, поступая в распределитель 4 импульсов, разрешает переход к режиму записи в блок 1 памяти. Запись информации в блок 1 памяти производится только в свободную строку во время кадровой защитной полосы. Для этого на информационные входы блока 1 памяти подается информация, соответствующая записываемому слову, а на второй вход коммутатора 6 адреса задается адрес слова АХ в строке. При подаче импульса Требование записи из ЭВМ в распределитель 4 импульсов, последний вырабатывает сигнал записи, по- которому информация записывается в соответствующую ячейку. После этого аналогично производится запись в следующие ячейки свободной строки.

Для смещения изображения теперь достаточно изменить на единицу адрес А( в регистре 10, причем А f + 1 соот- ветствует смещению изображения вверх.

а А

соответствует смещению вниз

(фиг. 4).

Таким образом, имея всего одну свободную неотображаемую в кадре

строку, организуя в ней соответствующую модификацию информации и задавая необходимые а,цреса Ац, можно организовать быстрый просмотр изображения путем смещения его по вертикали вверх или вниз.

Формула изобретения

2, Устройство по ,п. 1

отличающееся тем, что блок синхронизации содержит генератор импульсов, счетчик точек, счетчик строк, з дешифратор, первый, второй, третий и четвертый триггеры, одновибратор и сумматор, первый, второй, третий и четвертый информационные входы которого соединены с выходами первого, второго, третьего и четвертого триггеров, входы Установка в 1 которых связаны с первым, вторым, третьим и четвертым выходами дешифратора соответственно , первый и второй информационные входы которого подключены соответственно, к первому выходу счетчика точек и выходу счетчика строк, счетный вход которого связан с вторым выходом счетчика точек, счетный вход которого соединен с выходом генератора импульсов, вход одновибратора связан с выходом первого триггера, выход генератора импульсов является первым выходом блока, третий вькод счетчика точек является вторым выходом блока, вьпсод сумматора является третьим выходом блока, четвертый выход счетчика точек является четвертыг- выходом блока, выход первого триггера является пятым выходом блока, выход одновибратора является шестым выходом блока, выход четвертого триггера является седьмым выходом блока.

элементов И, первый выход третьего . распределителя, выход первого элемен- триггера подключен к второму входу 15 та И является вторым выходом распреде- пятого элемента И и первым входам лителй, выход второго элемента И явля- элементов И первой группы, второй вы- ется третьим выходом распределителя, ход третьего триггера соединен с вто- выходы четвертого, пятого элементов И, рым входом четвертого элемента И и элементов И первой и второй групп яв- с первыми входами элементов И второй 20 ляются выходами распредели- группы, вход Установка в 1 второго . теля.

триггера является управляющим входом распределителя, тактовьй вход сдвигового регистра соединен с первым входом дешифратора и является первым синхровходом распределителя, второй вход дешифратора соединен с вторыми входами элементов И первой и второй групп и является вторым синхровходом .

элемента И является тактовым входом распределителя, второй выход сдвигового регистра является первым выходом

и

12

Кбл.21,22

: ШИШВШШ

Kfffl 22,2ff,27

У

/{ff.S

Фи.2

распределителя, второй вход третье1 о

триггера является управляющим входом распределителя, тактовьй вход сдвигового регистра соединен с первым входом дешифратора и является первым синхровходом распределителя, второй вход дешифратора соединен с вторыми входами элементов И первой и второй групп и является вторым синхровходом

распределителя, второй вход третье1 о

распределителя, выход первого элемен- та И является вторым выходом распреде- лителй, выход второго элемента И явля- ется третьим выходом распределителя, выходы четвертого, пятого элементов И элементов И первой и второй групп яв- ляются выходами распредели- теля.

элемента И является тактовым входом распределителя, второй выход сдвигового регистра является первым выходом

13

П.

f

15

Г6

/7

78

ecu КВл.7

К5л..6.7

f f f f

20

13

V

.2

Ъ

«Ъ

1

§§

iC

I

I

Сэ

и

ш

:

n

t

i

ll

SI

II

ч

5:

It

ч:

| Устройство для отображения информации | 1975 |

|

SU543960A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-11-15—Публикация

1987-04-24—Подача