Изобретение относится к вычислительной технике, в частности к приоритетным устройствам, и может быть использовано в системах, управляющих доступом к некоторому общему ресурсу.

Известно устройство для подключения абонентов к общей магистрали 1, содержащее триггеры, логические схемы, формирователи импульсов и транзисторы.

Недостаток устройства состоит в том, что оно требует значительных затрат оборудования.

Известно многоканальное устройство для подключения абонентов к общей магистрали , содержащее в каждом канале генератор импульсов, триггеры разрешения, запроса и памяти запроса и элементы И.

Недостаток устройства в том, что оно не позволяет проводить анализ кодов устройств, запрашивающих магистраль.

Наиболее близким к изобретению по технической сущности и достигаемому результату является многоканальное устройство для подключения абонентов к общей магистрали 3, содержащее в каждом канале логические элементы, соединенные с каждым разрядом шины значения и шины дополнения общей мапистрали, запоминающее устройство и схему управления, соединенные выходами с логическими элементами, а также узел обработки значений в виде многораз1рядного компаратора, соединенный входами с логическими элемента ми, а выходом - со схемой управления.

Достоинство устройства - повыщенная скорость обработки приоритетов, которая достигается за счет параллельного выполнения сравнения многих приоритетных критериев системы.

Одна,ко для приоритетной обработки в

10 известном устройстве необходимо последовательно сравнить значения двоично-кодированных разрядов приоритетных критериев и их дополнений, устанавливаемые на

15 магистрали всеми каналами, с соответствующими значениями двоично-кодированных разрядов критерия и его дополнения данного канала, после чего только сравнение полученных результатов может в оп20тимальном варианте привести к исключению конкретного канала, имеющего малый приоритет.

Помимо большого числа достаточно

25 сложных операций, которые необходимо произвести в каждом канале для обработки приоритетов, существенным недостатком устройства является неопределенность количества щагов сравнения, которое в оп30тимальном случае равно одному, а в неоптимальном случае при большом числе каналов может быть достаточно большим.

Кроме того, реализация этого способа требует удвоенного количества логических элементов и шин обш;ей магистрали для проведения сравнения критериев в прямых и дополнительных кодах.

Таким образом, известное устройство требует значительных затрат оборудования и (Имеет малое быстродействие.

Цель изобретения - со1крагцение оборудования 1И повышение быстродействия.

Поставленная цель достигается тем, что в многоканальное устройство для подключения абонентов к общей магистрали, содержаш,1ее в каждом канале регистр, группу элементов И и бл,ок управления, причем каждый разрядный выход регистра канала соединен с первым входом соответствующего элемента И канала, выходы элементов И канала - с соответствующей группой выходов устройства, первый вход блока управления ка.нала связан с соопветстпуюгцим запросным входом устройства, вторые входы блоков управления .каналов- с тактовым входом устройства, а вход регистра канала - с соответствующим кодовыМ входом устройства, введены в каждый канал два дешифратора, два коммутатора и сумматор по mod 2. При этом группа выходов блока управления канала соединена с входами деш/ифраторов канала, группы выходов первого и второго дешифраторов канала - с группами управляющих входов соответственно первого и второго коммутаторов канала, информационные входы первого коммутатора канала - с соответствующей группой входов устройства. Информационные входы второго коммутатора канала связаны с разрядными 1выходам1и |регн1Стра, еыходы коммутато1р01в .канала через cyMiMaTOip по mod 2 1санала-с третьим входом блока управления ка;нала, выход которого подключен к вторым входам элементов И канала.

Поставленная дель достигается тем, что блок управления .каиала сод ржит триггер ,и 10четч1И1к, 1П;р1Ичв.м (первый, второй .и.ходы триггера соединены соответственло с in-eipiBbiiM и третыим входами блока уп1ра влеиия, а первый, второй входы и -разрядные г.ыхады счетчнка-соотеететвевно с вторым входом блока управления, -с выходом триггера и с грултой выходов бло1ха управлеЙГ.ИЯ.

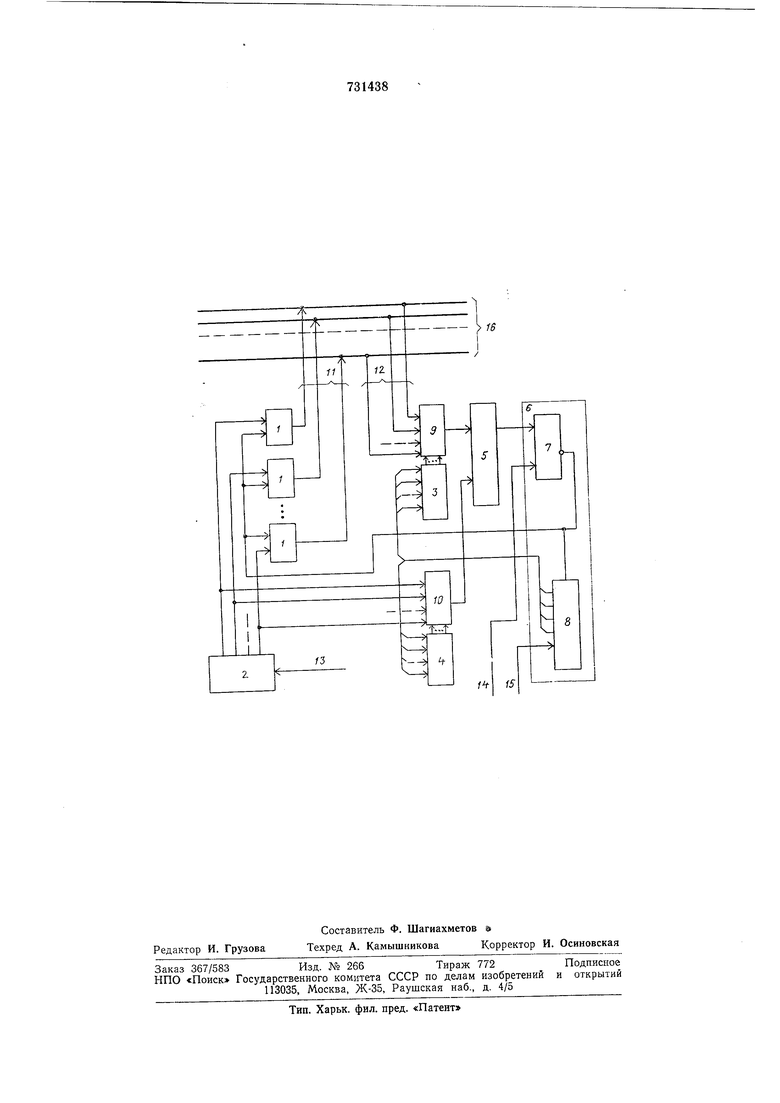

Структурная схема одного канала уст }iO«iCT Ba 1П|рИ1веден.а ц а чертеже.

Калал устройспва юодержит элементы И /, регистр 2, дешифраторы 3, 4, сумматор 3 ио mod 2, блок 6 управления, содержащий триггер 7 и счетчик 8. Канал содержит так- же коммутаторы 9, 10. Позицией 11 обозначена одаа ,из групп выходов устройства, .полицией /2-одна из групл входов устрой)стиа, лозицией 13-один из кодовых входов

устройства, позицией 14 - один из запросных входов ycTipioEciiBa, позицией 15.- тактовый вход устройства, ;Поз,пдией 16-общая магистраль.

Устройство работает следующим образам.

В .репистр 2 зааисывают адрес данного канала, соответствующий критерию его приоритета и представляющий собой двоичнее л-разрядное число, после чего адресную шнну общей магистрали подключают к входам коммутатора РНК выходам элементов И /. Требование на приоритетное обслуживание вход 14 ,станавлиаает тр.ишгер 7 блока 6 управления в состоян-ие «1, которым разрещается работа элементов И 1 и (Счетчика 5 блока 6 управления.

Па адресную щ|И|Ну общей магистрали 16 из регистра 2 через элементы И / выставлястся адрес данного канала в виде «-разрядноао двоичного числа. Поскольку требование :на обсл1уж1И1ва«ие может возникнуть сдНсвре:Ме,н«10 в 1 ескольких каиал-ах, на адресной шине устанавливается р-езультирующее число «проводного или.

Далее счетчиком 8 блока 6 уиравленсгя на входах двщифраторов 3, 4 устанавливают первое кодовое число, после чего состоян/не старшего разряда адресной щииы Mai-истрали 16 через ком-мутатор 9 и состояiHHc старшего разряда адреса данного канала через ксммутатср dO вводят в сумматор 5.

Результат сложения, равный «О, оандстельствует о то.м, что на адресной шине

магистрали 16 существует ;более высокий

ад|рес другого канала, триггер 7 блока

управления устанавливают в состояние «О,

сбр.асььвают счетчик 5 и закрывают эле.менты П 1, чем снимают адрес данного канала

с общей ма1гистрали 16.

Если результат слаж10ния равен «1, счетчик 8, работающий от тактовых н,мпульсов с входа 15, выставляет следующее Ч1НСЛО на входах дешифраторов 3 и 4, после чего сумматором 5 производят обработку состояния следующего (разряда адресной шины и адреса данного канала, записанного в регистре, и так шаг за щагом. Число Ш;агав обра1ботки -во всех случаях одно и то же И раино разрядности адресной шииы общей .магистрали 16. По око.нча1Н1И1Н обработки irap.aiHTHpOBaiHo подключение к общей малистрали только одного к.а.нала, ;1меющего наивысший адрес.

Изобретение позволяет упростить процедуру приоритетной обработки запросов, прнмени.в поразрядное сложен ие двоичных чисел вместо оравнения двоично-кодированных разрядов. Например, в известном устройстве только для одноступенчатой приоритетной обра|бо11ки одного двоично-кодированного разряда требуется нр01вести три оягерацни оравиенпя, а для м.ногосту|Пенчатой соответственно больше, в то время

как в изобретении для обработки каждого двоичного разряда производят только одну олфацию-,оум,М:Ир01вание по «.модулю 2. Кроме толо, не требуется лередача дополнительного кода.

Предлагаемое устройство требует вдвое меньшее количество шнн приоритетной Обработжи в общей ма.гистрали и COOTIBCTCTвенно 1вдвое меньшее количество эле-ментоа для ввода и вывода приоритетных критер|иев.

Ф о р М у л а и 3 о i6 р е т е ,н .и я

il. Много калальное устройство для нодключенйя або|Нентав « абш,ей магистралей, содержаш,ее в каждом канале регистр, груплу элементов И и блок управления, Лричем каждый раз-рядный выход регистра канала соединен с первым входом 1соот1ветствуюш,его элемента И канала, выходы элементов И канала соединены с соответствующей груялой выходов устройст;ва, лервый вход блока управления а ;анала соединен с соответсивующим зал.рооным входом устройсива, вторые входы блоков управления калалюв соединены с тактовым входом устройс11В1а, а вход регистра калала соединен с соответствующим кодовым входом устройства отличающееся тем, что, с целью сокращения оборудования, оно содержит (В .каждом канале два дещифратора, два коммутатора и сумматор по mod 2, Лричем грулла выходов блока управления

канала соединена с входами дещифраторов калала, группы выходов первого и второго дешифраторов канала соединены с группами управляющих входов соответственно первого :и второго коммутаторов калала, информационные входы первого коммутатора канала соединены с соответствующей группой входов устройства, информационные входы второго коммутатора канала соединены с разрядными выходами регистра, выходы коммутаторов канала через сумматор по mod 2 канала соединены с третьим входом блока управления канала, выход которого соединен с вторымивходами элементов И канала.

2. Устройство iHo и. 1, о т л и чающееся те;М, что блок управления канала содержит триггер и счетчик, причем первый, второй входы триггера соединены соответственно с первым и третьим входами блока управления, а первый, второй входы и разрядные выходы счетчика соединены соответственно с вторым входом блока управления, с выходом триггера и с группой выходов блока лш.оавления.

.i

Источники информации, принятые во Внимание лри экоиертизе:

1.Автооокое свидетельство СССР 317064, кл. G 06 F 9/18, 1971.

2.Авторское свидетельство СССР № 476566, кл. G 06 F 9/18, 1975.

3.Патент ФРГ Л 2210426, кл. 42 т 9 1975 (лрототил).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство с динамическим приоритетом | 1982 |

|

SU1049908A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072046A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для подключения источников информации с изменяемыми приоритетами к магистрали | 1983 |

|

SU1166111A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1985 |

|

SU1401459A1 |

| Устройство для реализации быстрого преобразования Фурье последовательности с нулевыми элементами | 1983 |

|

SU1119025A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1986 |

|

SU1388863A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

Авторы

Даты

1980-04-30—Публикация

1977-10-12—Подача