Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах цифровой обработки сигналов.

Цель изобретения - повышение быстродействия устройства.

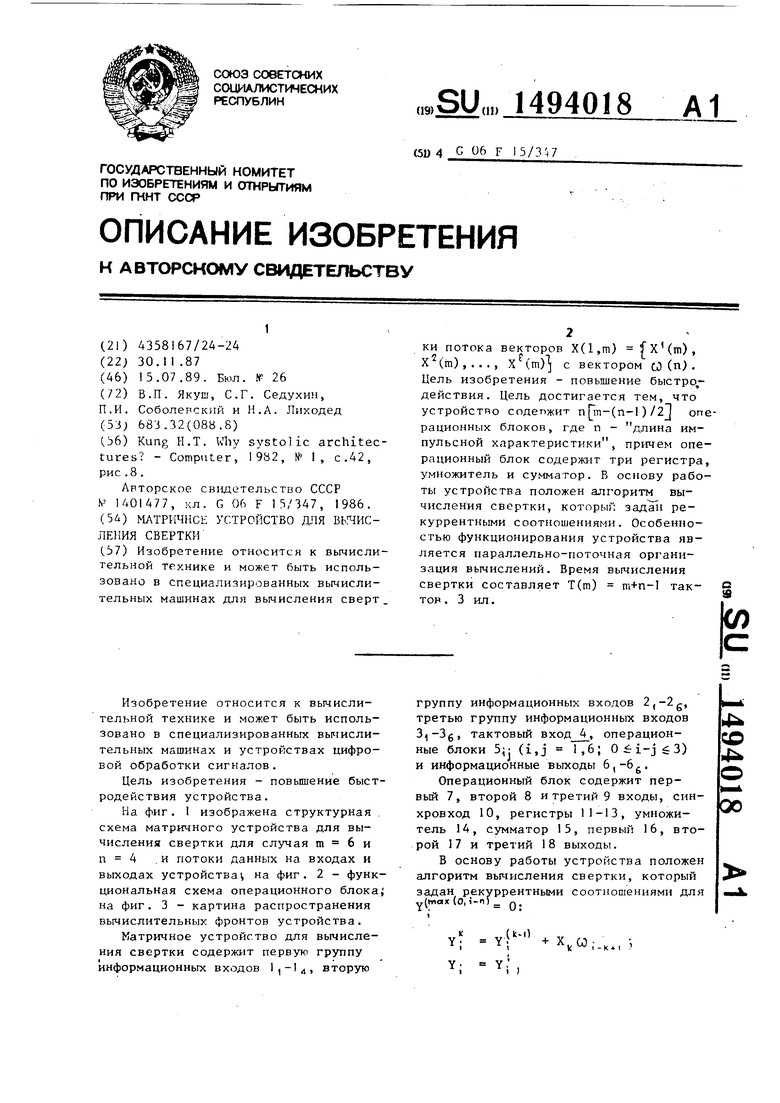

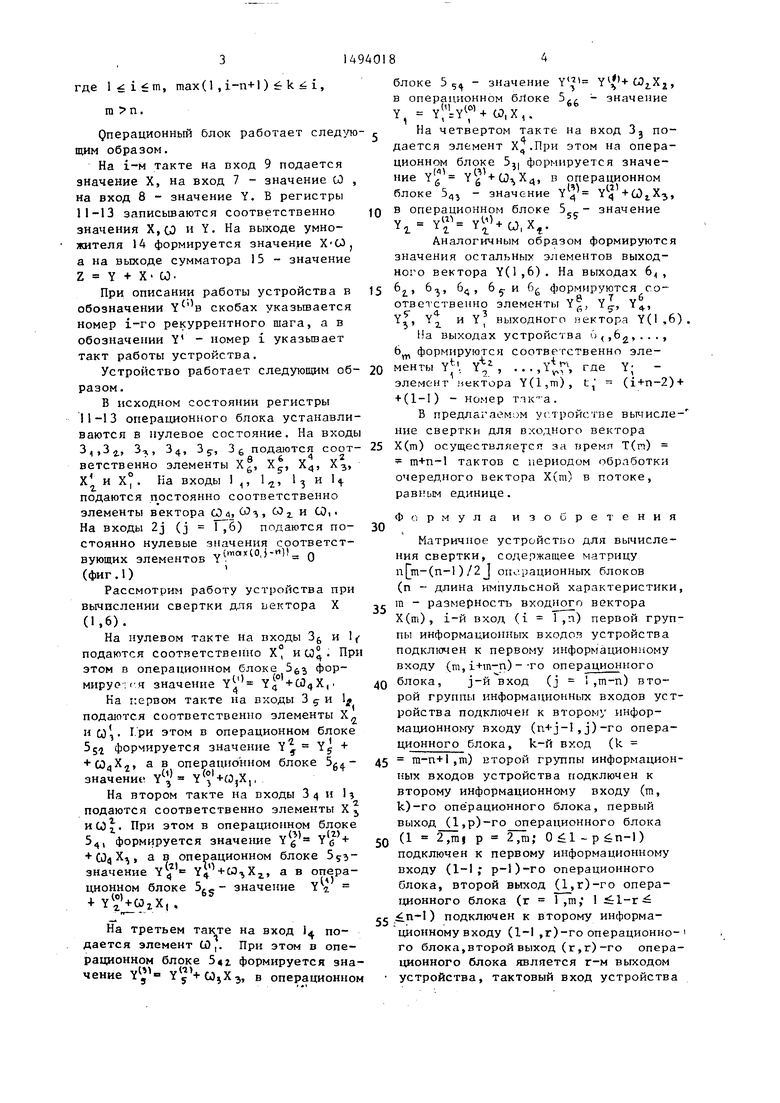

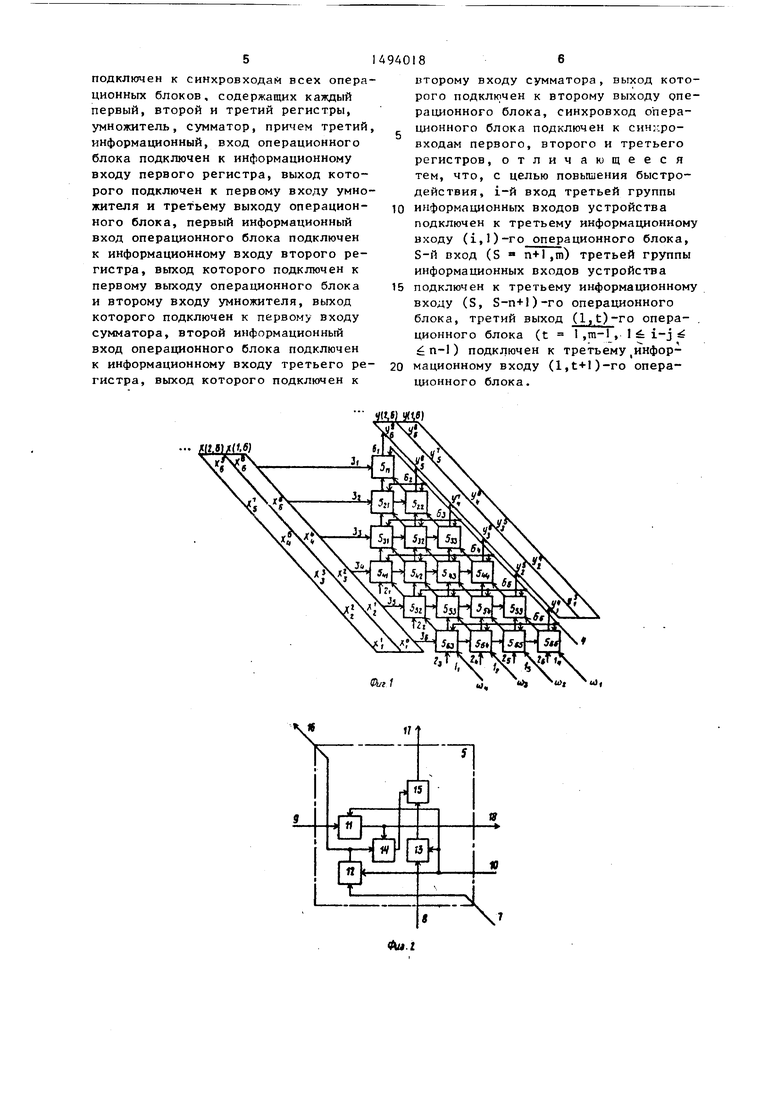

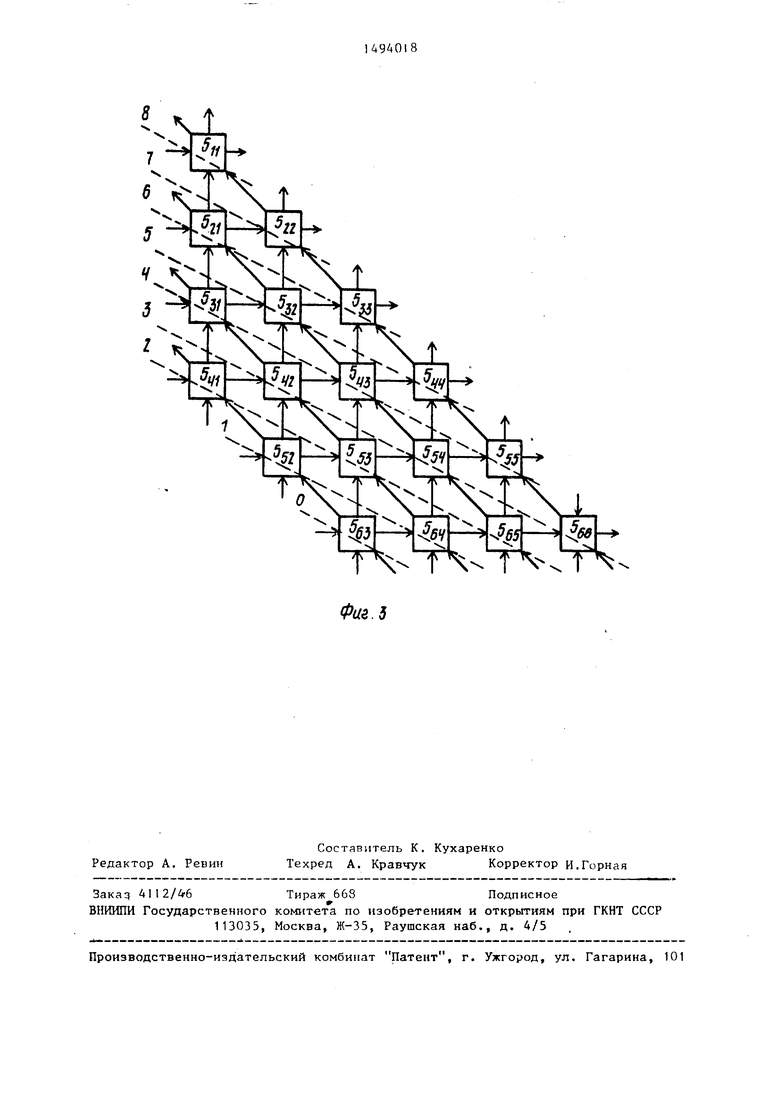

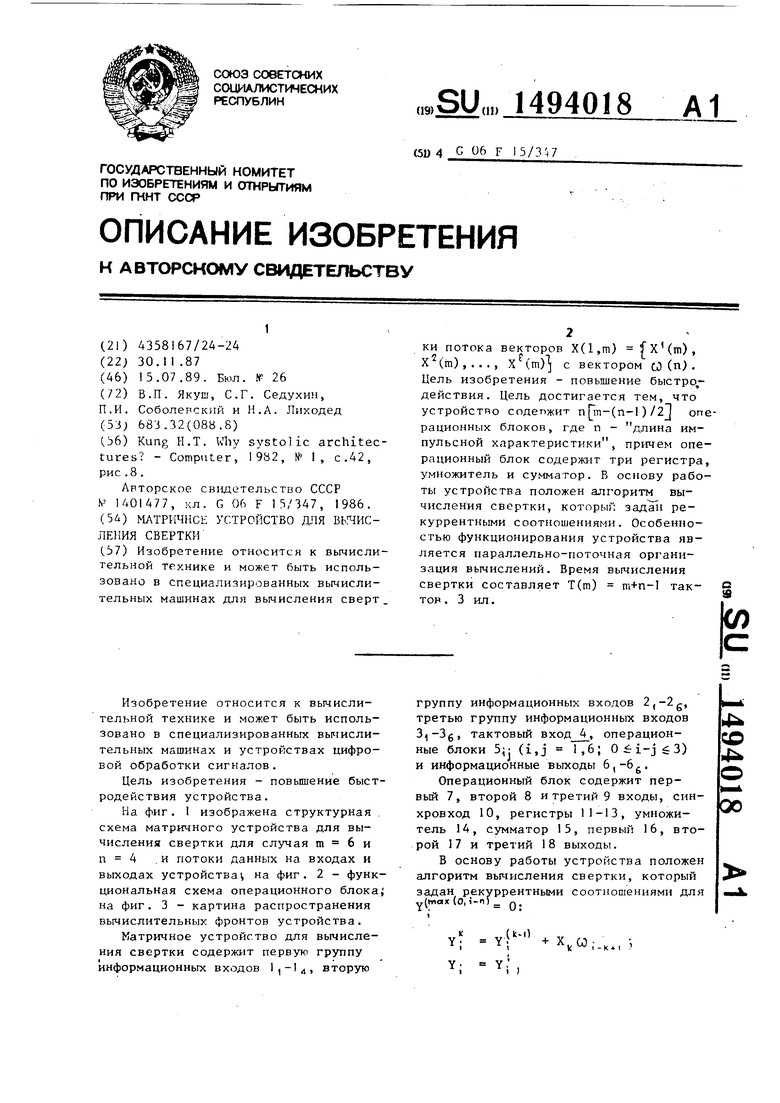

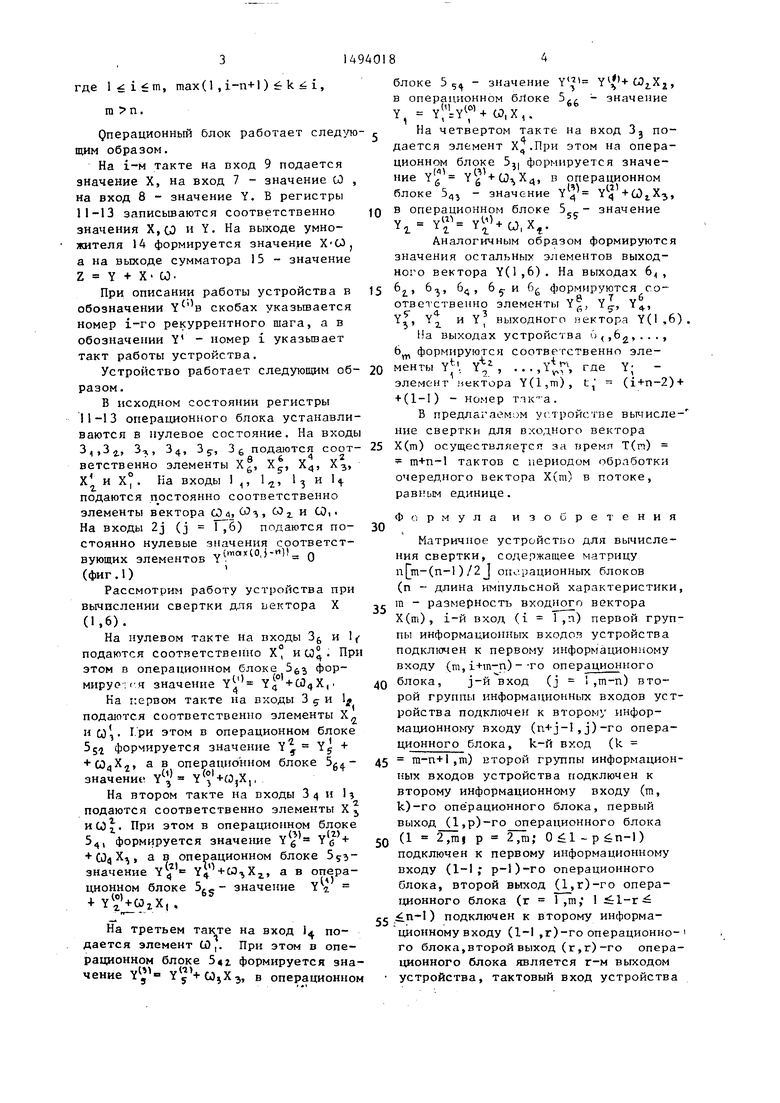

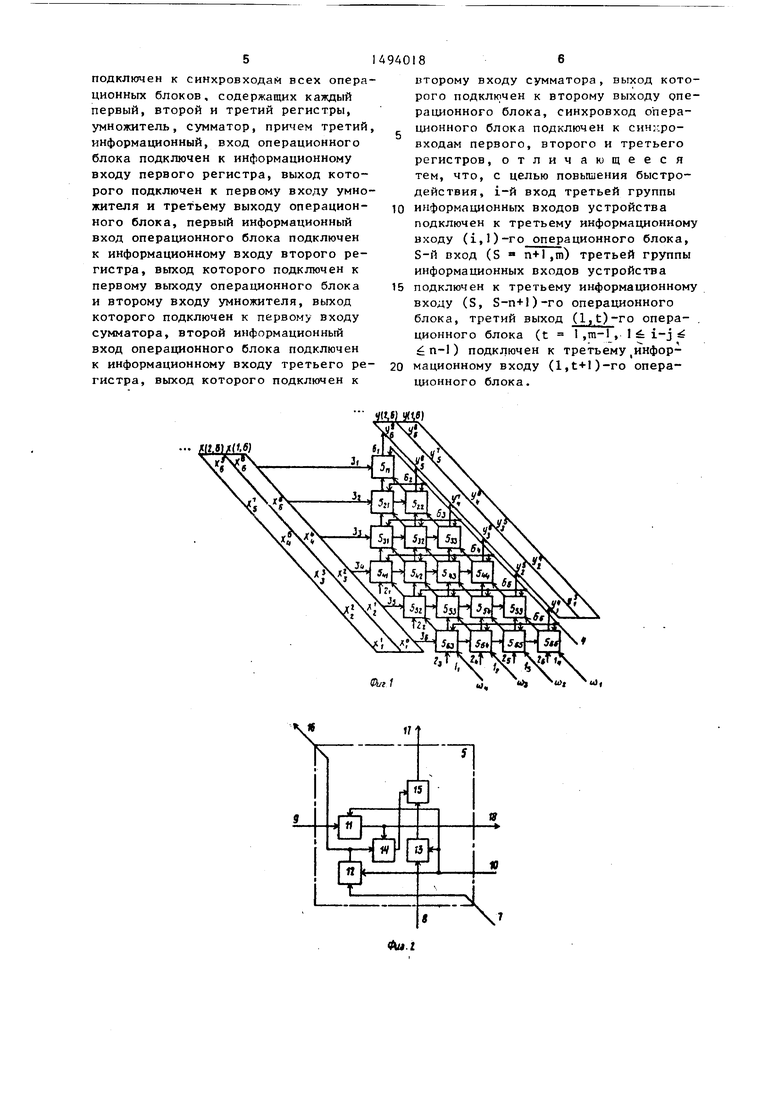

На фиг. 1 изображена структурная схема матричного устройства для вычисления свертки для случая m 6 и п 4 ,и потоки данных на входах и выходах устройства на фиг. 2 - функциональная схема операционного блока; на фиг. 3 - картина распространения вычислительных фронтов устройства.

Матричное устройство для вьмисле- ния свертки содержит первую группу информационных входов l,- вторую

группу информационных входов 2,-2g, третью группу информационных входов 3,-3g, тактовый , операционные блоки (i,j 1,6; ) и информационные выходы 6,-6g,

Операционный блок содержит первый 7, второй 8 и третий 9 входы, син- хровход 10, регистры 11-13, умножитель 14, сумматор 15, первый 16, второй 17 и третий 18 выходы.

В основу работы устройства положен алгоритм вычисления свертки, который задан рекуррентными соотношениями для

„(wax (о, i-n) Q.

4

4

00

Y Y

. Y:,

где , max(l , i-n+1) 6 k ё t, ra n.

рперационный блок работает следило щим образом.

На i-M такте на пход 9 подается значение X, на вход 7 - значение СО , на вход 8 - значение Y. В регистры 11-13 записьшаются соответственно значения Х.ОЭ и Y. На выходе умножителя 14 формируется значение Х-СЗ, а на выходе сумматора 15 - значение Z Y + Х- СОПри описании работы устройства в обозначении скобах указьшается номер i-ro рекуррентного шага, а в обозначении Y - номер i указьшает такт работы устройства.

Устройство работает следующим об- разом.

В исходном состоянии регистры 11-13 операционного блока устанавливаются в нулевое состояние. На входы . ч, 34, Зд-, Зб подаются соот- ветственно элементы Х, Х, Х, Хз, х и Х| . На входы I , 1 , Ц и 1 подаются постоянно соответственно элементы вектора C3n,(J, СО2. и СО,. На входы 2J (J 1,6) подаются по- стоянно нулевые значения соответствующих элементов у О (фиг. 1)

Рассмотрим работу устройства при вычислении свертки для вектора X (1,6).

На нулевом такте на входы 3 и ( подаются соответственно Х° иС0° . При этом в операционном блоке З Фор- мируок я значение (

На rtepBOM такте на входы ; к g подаются соответственно элементы Х, исОз- Р этом в операционном блоке Sj-i формируется значение Y Yj + , а в операционном блоке значение (0,X,,

На втором такте на входы 3 } и 1 подаются соответственно элементы X j иСЗ. При этом в операционном блоке 5, формируется значе1ше Y2 Wo , a в операционном блоке Зуз- значение Y , а в операционном блоке 5,в - значение Y ,X,.

На третьем такте на вход Ц подается элемент СО,. При этом в операционном блоке 5«2. формируется значение YJ Yy , в операционном

блоке 5 5 - значение Y +t02 XJ, в операционном блоке 5,,- - значение Y, .X,.

На четвертом такте на вход 3, пол3

дается элемент Х.При этом на операционном блоке 5j| формируется значение Yg Yg +COi,X(,, в операционном блоке 5 - значение Y Y +COl.Xз, в операционном блоке 5,,.- значение

Y - f у 1 г 1 и,

Аналогичным образом формируются значения остальных элементов выходного вектора Y(l,6). На выходах 6, , 6, 6, 6, 6 и 6 формируются соответственно элементы Y, Y, Y., Y, Yj и Y выходного нектора Y(l,6)

На выходах устройства и.б,..., Yl формируются соответственно элементы , ..., t-де Y; - элемент ,чектора Y(l,Tn), t, - (i+n-2) + + (1-I) - номер т )К а.

В предлагаемом устройстве вычисление свертки для входного вектора Х(т) осуществляеусп за время Т(та) i m+n-l тактов с периодом обработки очередного вектора Х(т) в потоке, равным единице.

Формула изобретения

Матричное устройство для вычисления свертки, содержащее матрицу (n-l)/2j операционных блоков (п - длина импульсной характеристики га - размерность входного вектора Х(т), i-й вход (i 1,п) первой группы информационных входов устройства подключен к первому инфopмaциoн ioмy входу (т,i+m-n)- то операционного блока, j-й вход (J 1,m-n) второй группы информационных входов устройства подключен к второму информационному входу (n+j-,j)-ro опера- ционного блока, k-й вход (k га-п+1,т) второй группы информационных входов устройства подключен к второму информационному входу (т, k)-ro опе рационного блока, первый выход (1,р)-го операционного блока (1 2) р ZTiii; ) подключен к первому информационному входу (1-1; р-1)-го операционного блока, второй выход (1,г)-го опера- 1Д10ННОГО блока (г 1 ,т, 1 п-1) подключен к второму информационному входу (1-1 ,г)-го операционного блока,второй выход (г ,г)-го операционного блока является г-м выходом устройства, тактовый вход устройства

,в)

Фиг1

.тт;

ц)) tt),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления деконволюции | 1987 |

|

SU1494017A1 |

| Матричное устройство для вычисления свертки | 1986 |

|

SU1401477A1 |

| Устройство для вычисления свертки | 1988 |

|

SU1587539A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1679502A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦЫ НА ВЕКТОР | 1991 |

|

RU2011222C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для воспроизведения зависимостей вида @ | 1985 |

|

SU1288692A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления булевых дифференциалов | 1989 |

|

SU1777132A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для вычисления свертки потока векторов X(L, M) ={X1(M), X2(M), ...XL(M)} с вектором Ω(N). Цель изобретения - повышение быстродействия. Цель достигается тем, что устройство содержит N [M-(N-1)/2] операционных блоков, где N - "длина импульсной характеристики", причем операционный блок содержит три регистра, умножитель и сумматор. В основу работы устройства положен алгоритм вычисления свертки, который задан рекуррентными соотношениями. Особенностью функционирования устройства является параллельно-поточная организация вычислений. Время вычисления свертки составляет T(M)=M+N-1 тактов. 3 ил.

8

Фие.5

Авторы

Даты

1989-07-15—Публикация

1987-11-30—Подача