о

01

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1984 |

|

SU1226535A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Устройство для контроля аппарата магнитной записи | 1985 |

|

SU1269206A2 |

| Устройство для детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи | 1986 |

|

SU1327172A1 |

| Устройство для контроля аппарата магнитной записи | 1984 |

|

SU1229822A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля аппарата магнитной записи | 1984 |

|

SU1247942A2 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1383449A1 |

Изобретение относится к вычислительной технике, может быть использовано для контроля блоков памяти и является усовершенствованием изобртения по а.с. № 1226535. Целью изобретения является сокращение времени контроля. Устройство содержит счетчик адресов, счетчик циклов, счетчик неисправностей, счетчик переполнения, оперативный накопитель, генератор импульсов, делитель частоты, коммутаторы, с первого по четвертый блоки сравнения, с первого по четвертый блоки выбора режима, блок управления, ждущие мультивибраторы, триггеры, элемент И, элементы ИЛИ, дещифратор. Достижение цели изобретения обеспечивается введением режима ускоренной проверки с подсчетом количества ощибок за один проход адресного пространства контролируемого блока памяти. Если число ощибок оказывается меньще граничного, задаваемого оператором в блоке управления, делается вывод о том, что общее количество ошибок в блоке памяти не больще допустимого, и блок памяти признается годным. 1 ил. i (Л

N3

Изобретение относится к вычислительной технике, может быть использовано для контроля блоков памяти и является усовершенствованием изобретения по авт. св. № 1226535.

Цель изобретения - сокращение времени контроля.

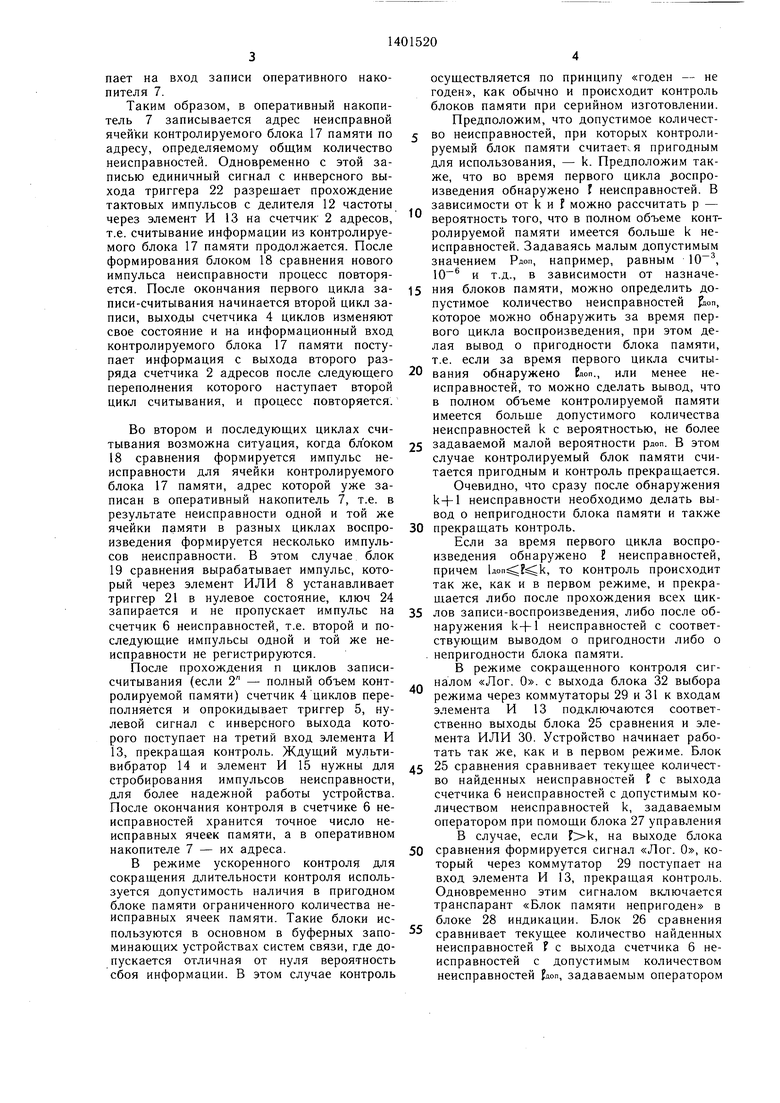

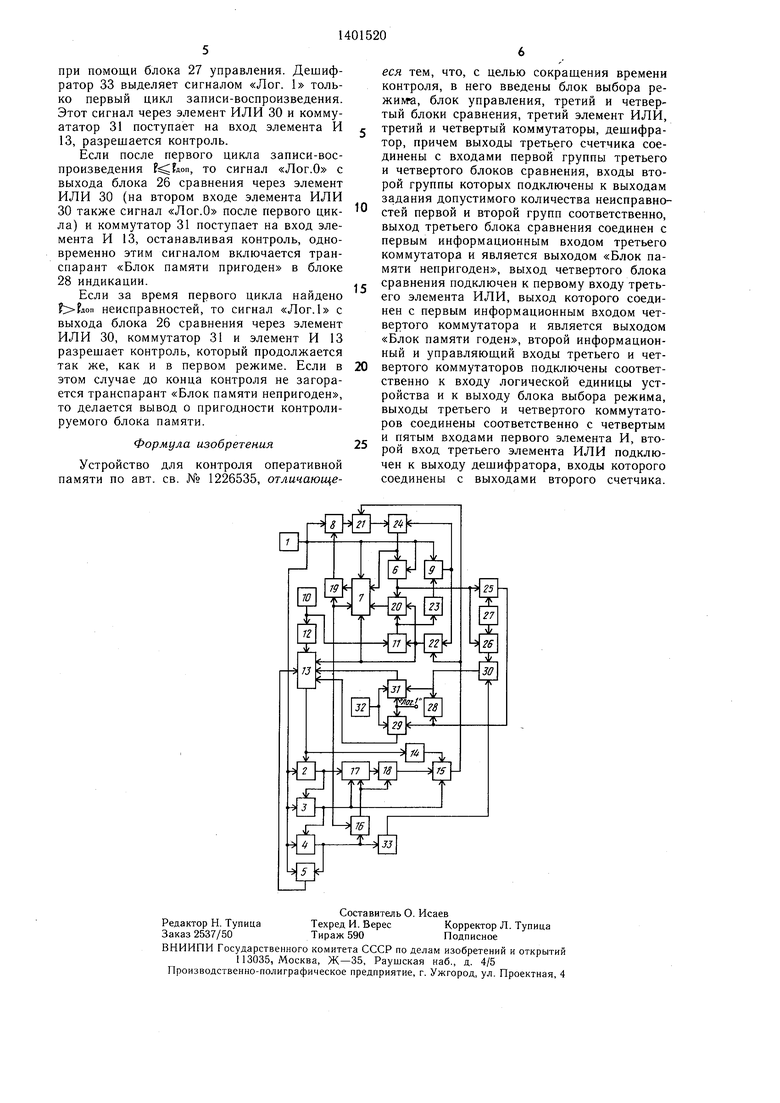

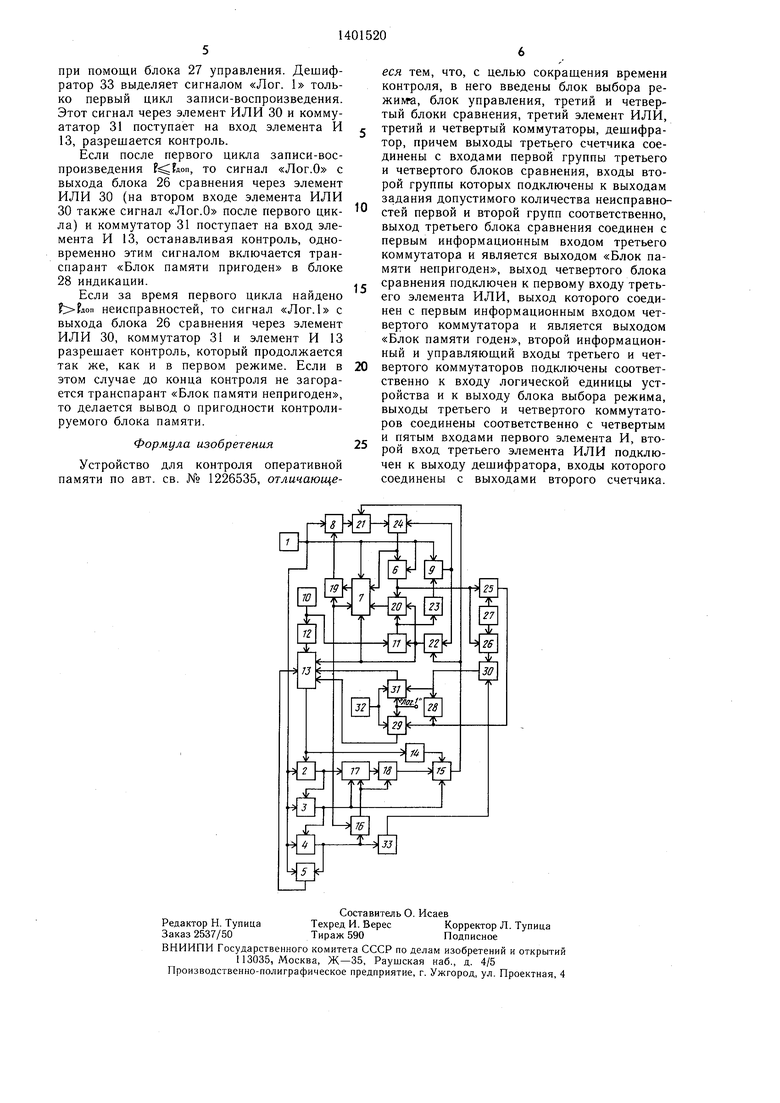

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит блок 1 начальной установки, счетчик 2 адресов, триггер 3, счетчик 4 циклов, триггер 5, счетчик 6 неисправностей, оперативный накопитель 7, элементы ИЛИ 8 и 9, генератор 10 импульсов, счетчик 11 переполнения, делитель 12 частоты, элемент И 13, ждущий мультивибратор 14, элемент И 15, первый коммутатор 16, контролируемый блок 17 памяти, первый блок 18 сравнения, второй блок 19 сравнения, второй коммутатор 20, триггеры 21 и 22, ждущий мультивибратор 23, ключ 24, третий 25 и четвертый 26 блоки сравнения, блок 27 управления, блок 28 индикации, третий коммутатор 29, элемент ИЛИ 30, четвертый коммутатор 31, блок 32 выбора режима, дещифратор 33.

Устройство работает следующим образом.

В режиме полного контроля блок выбора режима управляющим сигналом «Лог. 1 пропускает на четвертый и пятый входы элемента И 13 через коммутаторы 29 и 31 сигнал «Лог. 1, с их вторых информационных входов. В исходном состоянии сигналом «Лог. 1 поступающим из блока 1 начальной установки, обнулены счетчики адресов 2 и циклов 4, триггеры 3 и 5 и оперативный накопитель 7. Этим же сигналом, прощедшим через элементы ИЛИ 8 и 9, обнулены соответственно триггеры 21 и 22. Единичными сигналами с инверсных выходов триггеров 5 и 22, а также единичными сигналами с выходов коммутаторов 29 и 31, поступающими на входы элемента И 13, разрещается прохождение тактовых импульсов с генератора 10 через делитель 12 частоты на вход счетчика 2 адресов. Контролируемый блок 17 памяти нулевым сигналом с выхода триггера 3 включен в режим записи. Адресные входы оперативного накопителя 7, который единичным сигналом с инверсного выхода триггера 22 включен в режим записи, подключены через коммутатор 20 к выходам счетчика 6 неисправностей.

После прихода сигнала начала контроля из блока 1 начальной установки («Лог. О) счетчик 2 адресов начинает формировать адреса для записи информации в контролируемый блок 17 памяти. В первый цикл записи в контролируемый блок 17 памяти записывается информация, поступающая через коммутатор 16 с выхода первого разряда счетчика 2 адресов. После записи информации в полный объем контролируемого блока 17 памяти счетчик 2 адресов

5

переполняется и опрокидывает триггер 3, единичный сигнал с выхода которого переводит контролируемый блок 17 памяти в , режим воспроизведения. Так как во время

цикла записи-считывания счетчик 4 циклов не изменяет своего состояния, то сигнал, поступающий с коммутатора 16 на первый вход блока 18 сравнения, во время цикла считывания идентичен сигналу, который записан в контролируемый блок 17 памяти

0 во время цикла записи. Таким образом, информация, которая записана в контролируемый блок 17 памяти, сравнивается с воспроизведенной из него блоком 18 сравнения, который в случае несовпадения выс дает импульс неисправности.

Предположим, что произошло несовпадение и импульс неисправноти через элемент И 15 поступает на входы триггеров 21 и 22. Нулевой сигнал с инверсного выхода триггера 22 не позволяет тактовым импульсам

0 поступать с выхода элемента И 13 на вход счетчика 2 адресов, на выходах которого теперь хранится адрес неисправной ячейки памяти. Этот же нулевой сигнал с инверсного выхода триггера 22 переводит оперативный накопитель 7 в режим воспроизведения, переключает коммутатор 20 так, что адресные входы оперативного накопителя 7 подключены к выходам счетчика 11, а также разрешает счет счетчику И, на вход которого поступают такQ товые импульсы с больщой частотой непосредственно с генератора 10 импульсов.

Одновременно триггер 21 опрокидывается в единичное состояние, разрешая прохождение импульсов через ключ 24. Так как в первом цикле считывания во

5 время прохода каждого импульса неисправности в оперативном накопителе 7 не хранится адрес неисправной ячейки контролируемого блока 17 памяти, которой соответствует этот импульс, то в первом цикле считывания блок 19 сравнения не выраба0 тывает импульсов, которые могли бы опрокинуть через элемент ИЛИ 8 триггер 21, и ключ 24 пропускает на счетчик 6 неисправностей импульсы, которые формирует ждущий мультивибратор 23 после переполнения

с счетчика 11, т.е. после перебора всех адресов оперативного накопителя 7.

Одновременно импульс с выхода ждущего мультивибратора 23 через элемент ИЛИ 9 поступает на установочный вход триггера 22 и обнуляет его. Единичный

0 сигнал с инверсного выхода триггера 22 переводит оперативный накопитель 7 в жим записи, обнуляет счетчик 11 и переключает коммутатор 20, который соединяет адресные входы оперативного накопителя 7 с выходами счетчика 6 не5 исправностей, который уже сосчитал импульс, пришедщий с выхода ждущего мультивибратора 23 через элемент ИЛИ 9 и ключ 24. Одновременно этот импульс поступает на вход записи оперативного накопителя 7.

Таким образом, в оперативный накопитель 7 записывается адрес неисправной ячейки контролируемого блока 17 памяти по адресу, определяемому общим количество неисправностей. Одновременно с этой записью единичный сигнал с инверсного выхода триггера 22 разрешает прохождение тактовых импульсов с делителя 12 частоты через элемент И 13 на счетчик 2 адресов, т.е. считывание информации из контролируемого блока 17 памяти продолжается. После формирования блоком 18 сравнения нового импульса неисправности процесс повторяется. После окончания первого цикла записи-считывания начинается второй цикл записи, выходы счетчика 4 циклов изменяют свое состояние и на информационный вход контролируемого блока 17 памяти поступает информация с выхода второго разряда счетчика 2 адресов после следующего переполнения которого наступает второй цикл считывания, и процесс повторяется.

Во втором и последующих циклах считывания возможна ситуация, когда блоком

18сравнения формируется импульс неисправности для ячейки контролируемого блока 17 памяти, адрес которой уже записан в оперативный накопитель 7, т.е. в результате неисправности одной и той же ячейки памяти в разных циклах воспроизведения формируется несколько импульсов неисправности. В этом случае блок

19сравнения вырабатывает импульс, который через элемент ИЛИ 8 устанавливает триггер 21 в нулевое состояние, ключ 24 запирается и не пропускает импульс на счетчик 6 неисправностей, т.е. второй и последующие импульсы одной и той же неисправности не регистрируются.

После прохождения п циклов записи- считывания (если 2 - полный объем контролируемой памяти) счетчик 4 циклов переполняется и опрокидывает триггер 5, нулевой сигнал с инверсного выхода которого поступает на третий вход элемента И 13, прекращая контроль. Ждущий мультивибратор 14 и элемент И 15 нужны для стробирования импульсов неисправности, для более надежной работы устройства. После окончания контроля в счетчике 6 неисправностей хранится точное число неисправных ячеек памяти, а в оперативном накопителе 7 - их адреса.

В режиме ускоренного контроля для сокращения длительности контроля используется допустимость наличия в пригодном блоке памяти ограниченного количества неисправных ячеек памяти. Такие блоки используются в основном в буферных запоминающих устройствах систем связи, где допускается отличная от нуля вероятность сбоя информации. В этом случае контроль

0

осуществляется по принципу «годен - не

годен, как обычно и происходит контроль

блоков памяти при серийном изготовлении.

Предположим, что допустимое количество неисправностей, при которых контролируемый блок памяти считает;.я пригодным для использования, - k. Предположим также, что во время первого цикла .эоспро- изведения обнаружено Г неисправностей. В зависимости от k и Г можно рассчитать р - вероятность того, что в полном объеме контролируемой памяти имеется больще k неисправностей. Задаваясь малым допустимым значением Рдоп, например, равным 10, и т.д., в зависимости от назначе5 ния блоков памяти, можно определить допустимое количество неисправностей рюп, которое можно обнаружить за время первого цикла воспроизведения, при этом делая вывод о пригодности блока памяти, т.е. если за время первого цикла считы0 вания обнаружено Едоп., или менее неисправностей, то можно сделать вывод, что в полном объеме контролируемой памяти имеется больще допустимого количества неисправностей k с вероятностью, не более

5 задаваемой малой вероятности рдоп. В этом случае контролируемый блок памяти считается пригодным и контроль прекращается. Очевидно, что сразу после обнаружения k-|-l неисправности необходимо делать вывод о непригодности блока памяти и также

0 прекращать контроль.

Если за время первого цикла воспроизведения обнаружено S неисправностей, причем , то контроль происходит так же, как и в первом режиме, и прекращается либо после прохождения всех цик5 лов записи-воспроизведения, либо после обнаружения k-j-1 неисправностей с соответствующим выводом о пригодности либо о . непригодности блока памяти.

В режиме сокращенного контроля сиг0

налом «Лог. О, с выхода блока 32 выбора

режима через коммутаторы 29 и 31 к входам элемента И 13 подключаются соответственно выходы блока 25 сравнения и элемента ИЛИ 30. Устройство начинает работать так же, как и в первом режиме. Блок

5 25 сравнения сравнивает текущее количество найденных неисправностей с выхода счетчика 6 неисправностей с допустимым количеством неисправностей k, задаваемым оператором при помощи блока 27 управления В случае, если k, на выходе блока

0 сравнения формируется сигнал «Лог. О, который через коммутатор 29 поступает на вход элемента И 13, прекращая контроль. Одновременно этим сигналом включается транспарант «Блок памяти непригоден в блоке 28 индикации. Блок 26 сравнения

сравнивает текущее количество найденных неисправностей F с выхода счетчика 6 неисправностей с допустимым количеством неисправностей доп, задаваемым оператором

при помощи блока 27 управления. Дешифратор 33 выделяет сигналом «Лог. 1 только первый цикл записи-воспроизведения. Этот сигнал через элемент ИЛИ 30 и комму- ататор 31 поступает на вход элемента И 13, разрешается контроль.

Если после первого цикла записи-воспроизведения , то сигнал «Лог.О с выхода блока 26 сравнения через элемент ИЛИ 30 (на втором входе элемента ИЛИ 30 также сигнал «Лог.О после первого цик- ла) и коммутатор 31 поступает на вход элемента И 13, останавливая контроль, одновременно этим сигналом включается транспарант «Блок памяти пригоден в блоке 28 индикации.

Если за время первого цикла найдено Рдоп неисправностей, то сигнал «Лог. 1 с выхода блока 26 сравнения через элемент ИЛИ 30, коммутатор 31 и элемент И 13 разрешает контроль, который продолжается так же, как и в первом режиме. Если в этом случае до конца контроля не загорается транспарант «Блок памяти непригоден, то делается вывод о пригодности контролируемого блока памяти.

Формула изобретения

Устройство для контроля оперативной памяти по авт. св. № 1226535, отличающе

5

0

5

вся тем, что, с целью сокращения времени контроля, в него введены блок выбора ре- жилга, блок управления, третий и четвертый блоки сравнения, третий элемент ИЛИ, третий и четвертый коммутаторы, дешифратор, причем выходы треть,его счетчика соединены с входами первой группы третьего и четвертого блоков сравнения, входы второй группы которых подключены к выходам задания допустимого количества неисправностей первой и второй групп соответственно, выход третьего блока сравнения соединен с первым информационным входом третьего коммутатора и является выходом «Блок памяти непригоден, выход четвертого блока сравнения подключен к первому входу третьего элемента ИЛИ, выход которого соединен с первым информационным входом четвертого коммутатора и является выходом «Блок памяти годен, второй информационный и управляющий входы третьего и четвертого коммутаторов подключены соответственно к входу логической единицы устройства и к выходу блока выбора режима, выходы третьего и четвертого коммутаторов соединены соответственно с четвертым и пятым входами первого элемента И, второй вход третьего элемента ИЛИ подключен к выходу дешифратора, входы которого соединены с выходами второго счетчика.

| Устройство для контроля оперативной памяти | 1984 |

|

SU1226535A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1988-06-07—Публикация

1986-08-05—Подача