Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля блоков памяти.

Цель изобретения повьппение надежности устройства для контроля блоков памяти.

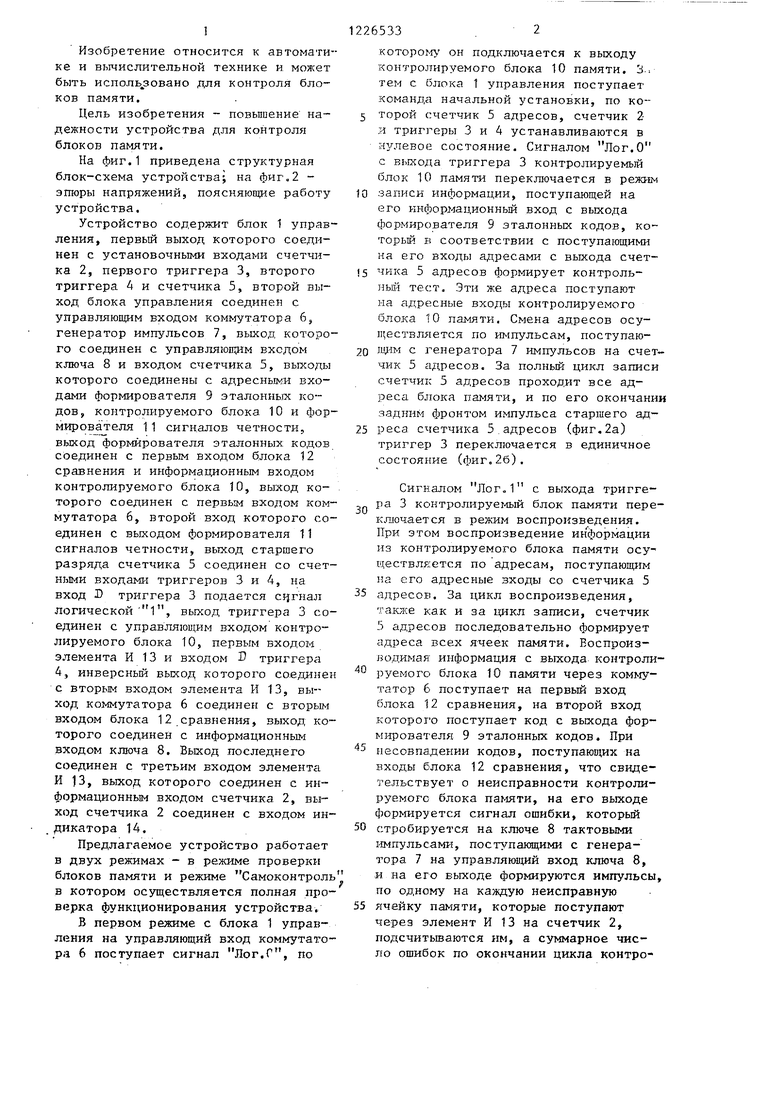

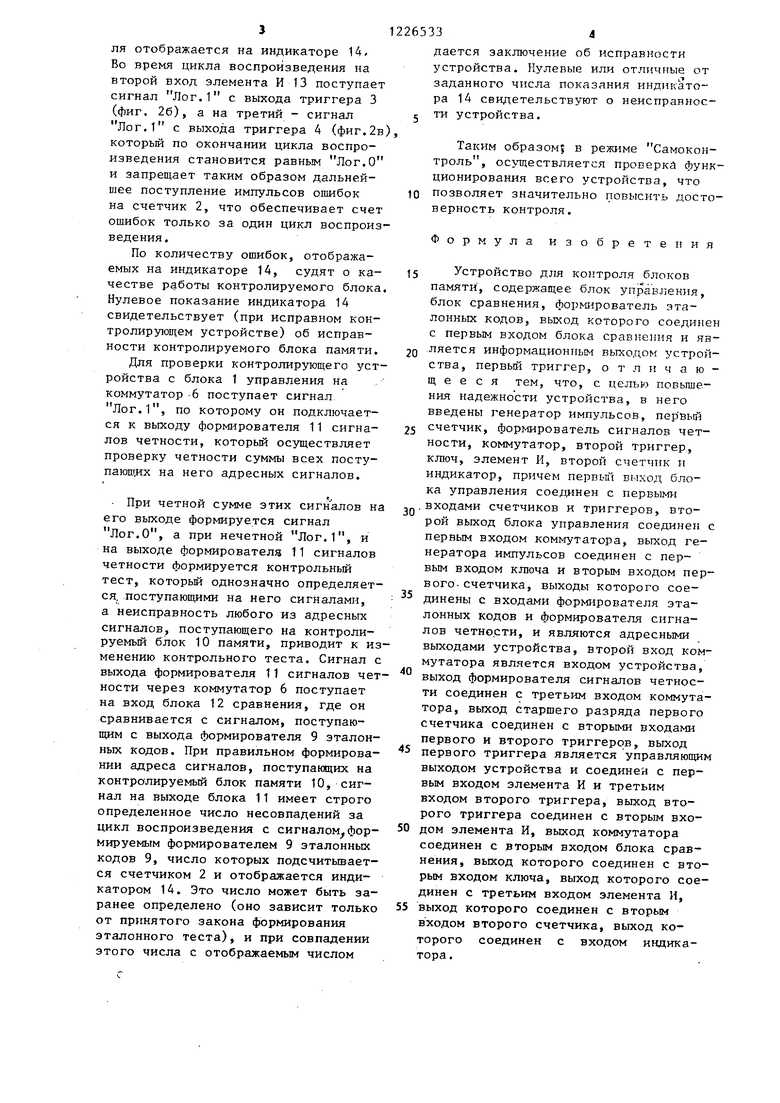

На фиг.1 приведена структурная блок-схема устройства; на фиг,2 - эпюры напряжений, поясняющие работу устройства.

Устройство содержит блок 1 управления, первый выход которого соединен с установочными входами счетчика 2, первого триггера 3, второго триггера 4 и счетчика 5, второй выход блока управления соединен с управляющим входом коммутатора 6, генератор импульсов 7, выход, которого соединен с управляющим входом ключа 8 и входом счетчика 5, выходы которого соединены с адресными входами формирователя 9 .(х кодов, контролируемого блока 10 и фор- миров.теля 11 сигналов четности, выход формирователя эталонных кодов соединен с первым входом блока 12 сравнения и информационным входом контролируемого блока 10, выход которого соединен с первым входом коммутатора б, второй вход которого соединен с выходом формирователя 11 сигналов четности, выход старшего разряда счетчика 5 соединен со счетными входами триггеров 3 и 4, на вход D триггера 3 подается сигнал логической 1, выход триггера 3 соединен с управляющим входом контролируемого блока 10, первым входом элемента И 13 и входом D триггера 4, инверсньй выход которого соедд1нен С вторым входом элемента И 13, выход коммутатора 6 соединен с вторым входом блока 12 сравнения, выход которого соединен с информационным входом ключа 8. Выход последнего соединен с третьим входом элемента И 13, выход которого соединен с информационным входом счетчика 2, выход счетчика 2 соединен с входом индикатора 14.

Предлагаемое устройство работа€ т в двух режимах - в режиме проверки блоков памяти и режиме Самоконтроль в котором ос5тцествляется полная проверка функционирования устройства,

В первом режиме с блока 1 управления на управляющий вход коммутатора 6 поступает сигнал Лог.Г, по

1226533 . 2

которо -1 он подключается к выходу контролируемого блока 10 памяти. 3.. тем с блока 1 управления поступает команда начальной установки, по ко5 торой :четчик 5 адресов, счетчик 2 л триггеры 3 и 4 устанавливаются в нулевое состояние. Сигналом Лог.О с выхода триггера 3 контролируемьм блок 10 памяти переключается в режим

10 записи информации, поступающей на его кнформационньй вход с выхода формирователя 9 эталонных кодов, который в соответствии с поступающими на его входы адресами с выхода счет 5 чика 5 адресов формирует контрольный тест. Эти же адреса поступают ыа адресные входы контролируемого блока to памяти. Смена адресов осу- 111;ествляется по импульсам, поступаю20 лщм с генератора 7 импульсов на счетчик 5 адресов. За полный цикл записи счетчик 5 адресов проходит все адреса блока памяти, и по его окончании задним фронтом импульса старшего ад-

25 реса с гетчика 5. адресов (фиг.2а) триггер 3 переключается в единичное состояние (фиг,2б).

30

Сигналом Лог.1 с выхода триггера 3 контролируе1 1ый блок памяти пере- к.гаочается в режим воспроизведения. При этом воспроизведение информации из контролируемого блока памяти осуществляется по адресам, поступающим на его адресные входы со счетчика 5

35 адресов. За цикл воспроизведения, таклсе как и за гщкл записи, счетчик 5 адресов последовательно формирует адреса всех ячеек памяти. Боспроиз- водимая информация с выхода контроли руемого блока 10 памяти через коммутатор 6 поступает на первый вход блока 12 сравнения, на второй вход которого поступает код с выхода формирователя 9 эталонных кодов. При

45

несовпадении кодов, поступающих на

входы блока 12 сравнения, что свидетельствует о неисправности контролируемого блока памяти, на его выходе формируется сигнал ошибки, который

50 стробируется на ключе 8 тактовыми импульсами, поступающими с генератора 7 на управллкш ий вход ключа 8, и на его выходе формируются импульсы, по одному на каждую неисправную

55 ячейку памяти, которые поступают через элемент И 13 на счетчик 2, подсчитьшаются им, а суммарное число ошибок по окончании цикла контро

Сигналом Лог.1 с выхода триггера 3 контролируе1 1ый блок памяти пере- к.гаочается в режим воспроизведения. При этом воспроизведение информации из контролируемого блока памяти осуществляется по адресам, поступающим на его адресные входы со счетчика 5

адресов. За цикл воспроизведения, таклсе как и за гщкл записи, счетчик 5 адресов последовательно формирует адреса всех ячеек памяти. Боспроиз- водимая информация с выхода контролируемого блока 10 памяти через коммутатор 6 поступает на первый вход блока 12 сравнения, на второй вход которого поступает код с выхода формирователя 9 эталонных кодов. При

несовпадении кодов, поступающих на

входы блока 12 сравнения, что свидетельствует о неисправности контролируемого блока памяти, на его выходе формируется сигнал ошибки, который

стробируется на ключе 8 тактовыми импульсами, поступающими с генератора 7 на управллкш ий вход ключа 8, и на его выходе формируются импульсы, по одному на каждую неисправную

ячейку памяти, которые поступают через элемент И 13 на счетчик 2, подсчитьшаются им, а суммарное число ошибок по окончании цикла контро3

ля отображается на индикаторе 14. Во время цикла воспроизведения на второй вход элемента И 13 поступает сигнал Лог.1 с выхода триггера 3 (фиг. 26), а на третий - сигнал Лог.1 с выхода триггера 4 (фиг.2в которьй по окончании цикла воспроизведения становится равным Лог.О и запрещает таким образом дальнейшее поступление импульсов ошибок на счетчик 2, что обеспечивает счет ошибок только за один цикл воспроизведения.

По количеству ошибок, отображаемых на индикаторе 14, судят о качестве работы контролируемого блока Нулевое показание индикатора 14 свидетельствует (при исправном контролирующем устройстве) об исправности контролируемого блока памяти.

Для проверки контролирующего устройства с блока 1 управления на коммутатор -6 поступает сигнал Лог,1, по которому он подключается к выходу формирователя 11 сигналов четности, которьй осуществляет проверку четности суммы всех посту- паюидх на него адресных сигналов,

При четной сумме этих сигн алов на его выходе формируется сигнал Лог,О, а при нечетной Лог.1, и на выходе формирователя 11 сигналов четности формируется контрольньй тест, которьй однозначно определяется, поступающими на него сигналами, а неисправность любого из адресных сигналов, поступающего на контроли- руемьй блок 10 памяти, приводит к изменению контрольного теста. Сигнал с выхода формирователя 11 сигналов чет ности через коммутатор 6 поступает на вход блока 12 сравнения, где он сравнивается с сигналом, поступающим с выхода формирователя 9 эталонных кодов. При правильном формировании адреса сигналов, поступающих на контро лнруемьй блок памяти 10, сигнал на выходе блока 11 имеет строго определенное число несовпадений за цикл воспроизведения с сигналом формируемым формирователем 9 эталонных кодов 9, число которых подсчитьшает- ся счетчиком 2 и отображается индикатором 14, Это число может быть заранее определено (оно зависит только от принятого закона формирования эталонного теста), и при совпадении этого числа с отображаемым числом

265334

дается заключение об исправности устройства. Нулевые или отличные от заданного числа показания индикатора 14 свидетельствуют о неисправнос- г ти устройства.

Таким образом в режиме Самоконтроль, ос тцествляется проверка функционирования всего устройства, что 10 позволяет значительно повысить достоверность контроля.

Формула изобретения

15 Устройство для контроля блоков памяти , содержащее блок управления, блок сравнения, формирователь эталонных кодов, выход которого соединен с первым входом блока сравне 1ия и ян2Q .ляется информационпьм выходом устройства, первьш триггер, отличающееся тем, что, с целью повьше- ния надежности устройства, в него введены генератор импульсов, первьп1

25 счетчик, формирователь сигналов четности, коммутатор, второй триггер, ключ, элемент И, второй счетчик п индикатор, причем первьд выход блока управления соединен с первыми

-„.входами счетчиков и триггеров, второй выход блока управления соединен с первым входом коммутатора, выход генератора импульсов соединен с первым входом ключа и вторым входом первого- счетчика, выходы которого сое- : динены с входами фopм: poвaтeля эталонных кодов и формирователя сигналов четности, и являются адресными выходами устройства, второй вход коммутатора является входом устройства, выход формирователя сигналов четности соединен с третьим входом коммутатора, выход старшего разряда первого счетчика соединен с вторыми входами первого и второго триггеров, выход

40

45

первого триггера является управпяющкн

выходом устройства и соединен с первым входом элемента И и третьим входом второго триггера, выход второго триггера соединен с вторым входом элемента И, выход коммутатора соединен с вторым входом блока сравнения, выход которого соединен с вторым входом ключа, выход которого соединен с третьим входом элемента И,

выход которого соединен с вторым входом второго счетчика, выход которого соединен с входом индикатора ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для приема телесигналов | 1983 |

|

SU1137497A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля блоков памяти. Целью изобретения является повьшение надежности устройства за счет осуществления режима Самоконтроль, в котором осуществляется проверка функционирования всего устройства. Устройство содержит блок управления, счетчики, триггеры, коммутатор, генератор импульсов, ключ, формирователь эталонных кодов, формирователь сигналов четности, блок сравнения, элемент И, индикатор. Показания индикатора свидетельствуют об исправности работы контролируемого блока памяти, а также самого устройстёа, 2 ил. с 9

| Устройство для контроля блоков оперативной памяти | 1979 |

|

SU888211A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU926725A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-23—Публикация

1984-08-13—Подача