1

Изобретение относится к вычислительной технике и ав1юматике и может быть использовано для контроля магнитных и полупроводниковых блоков оперативной памяти.

Целью изобретения является повышение достоверности контроля.

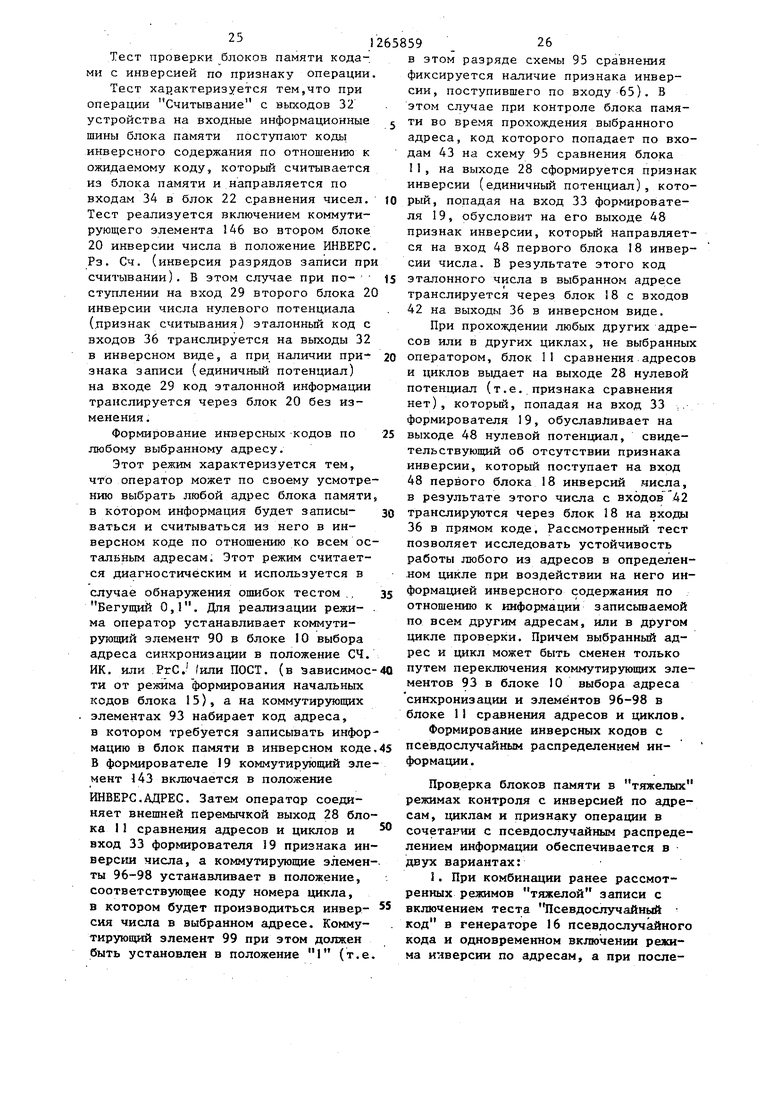

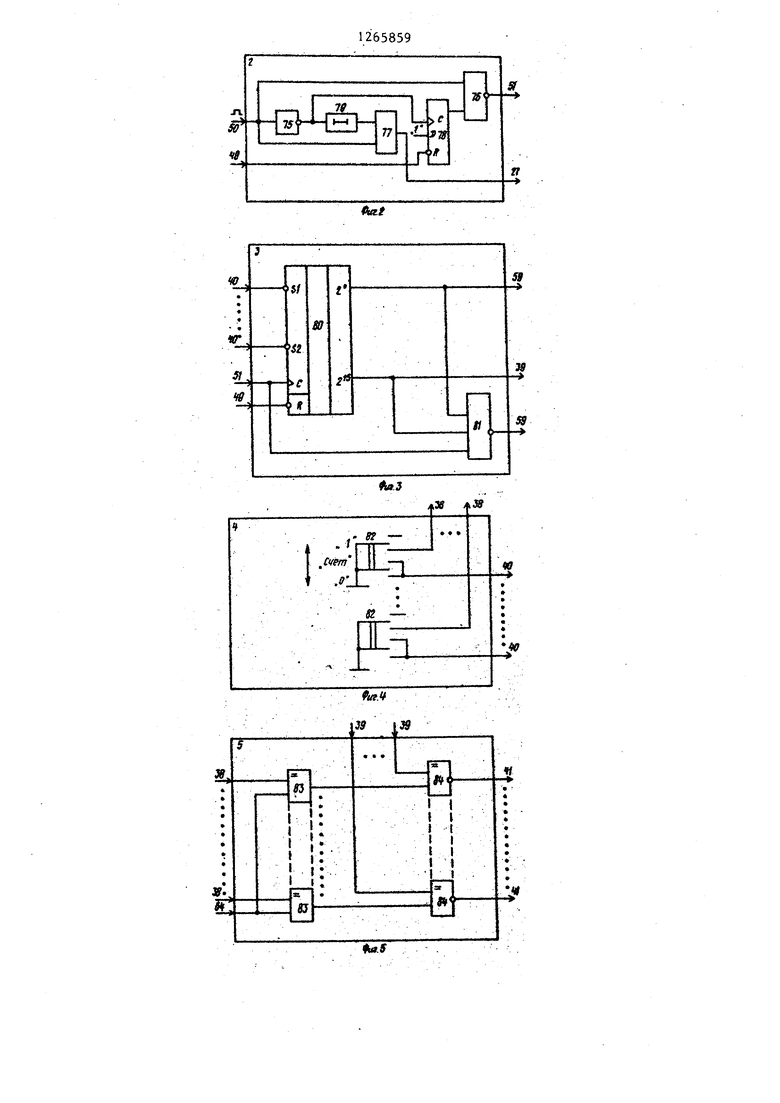

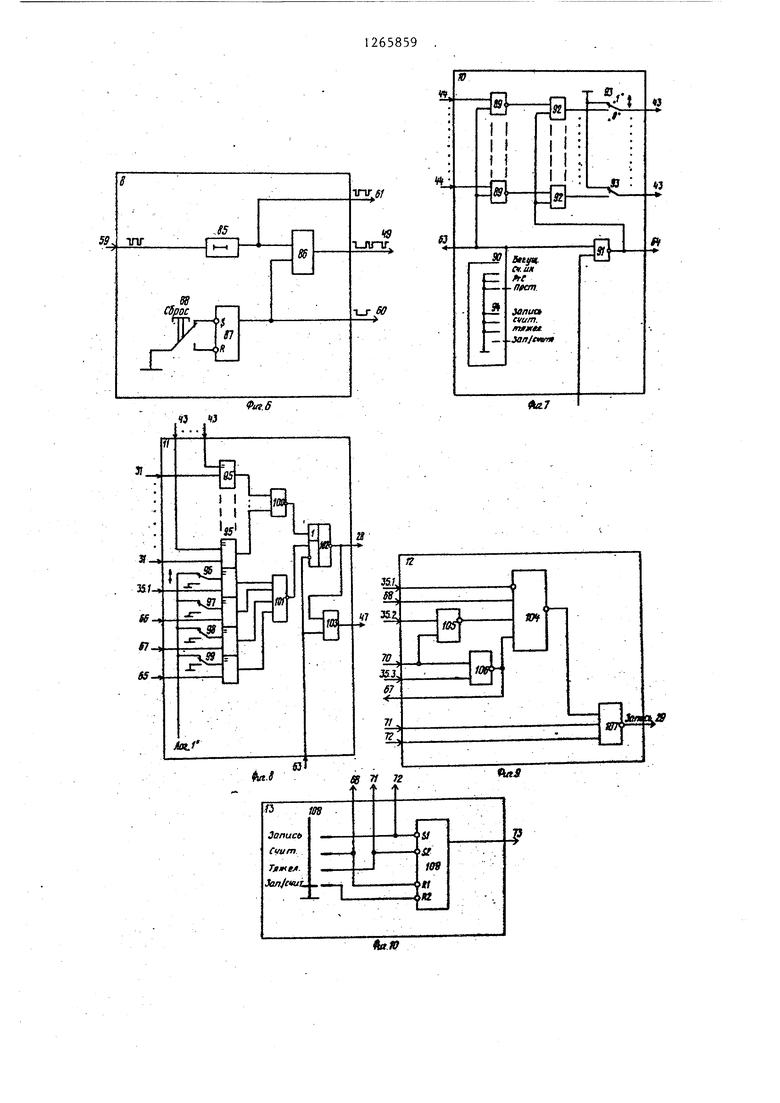

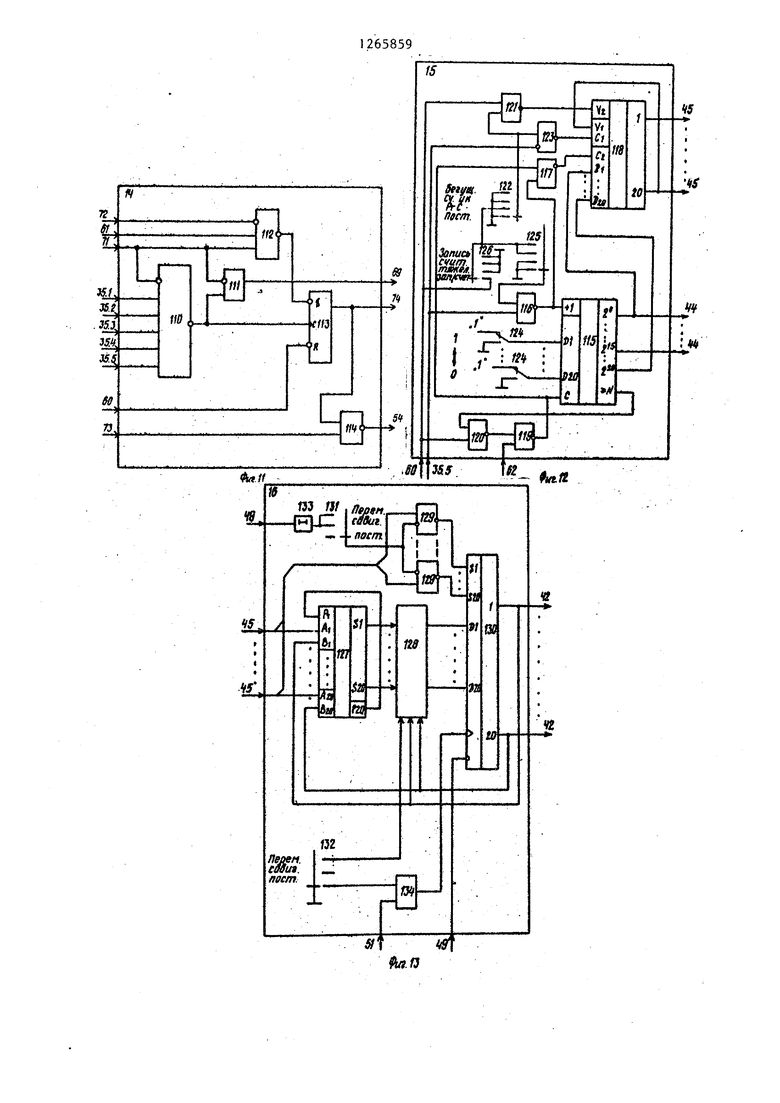

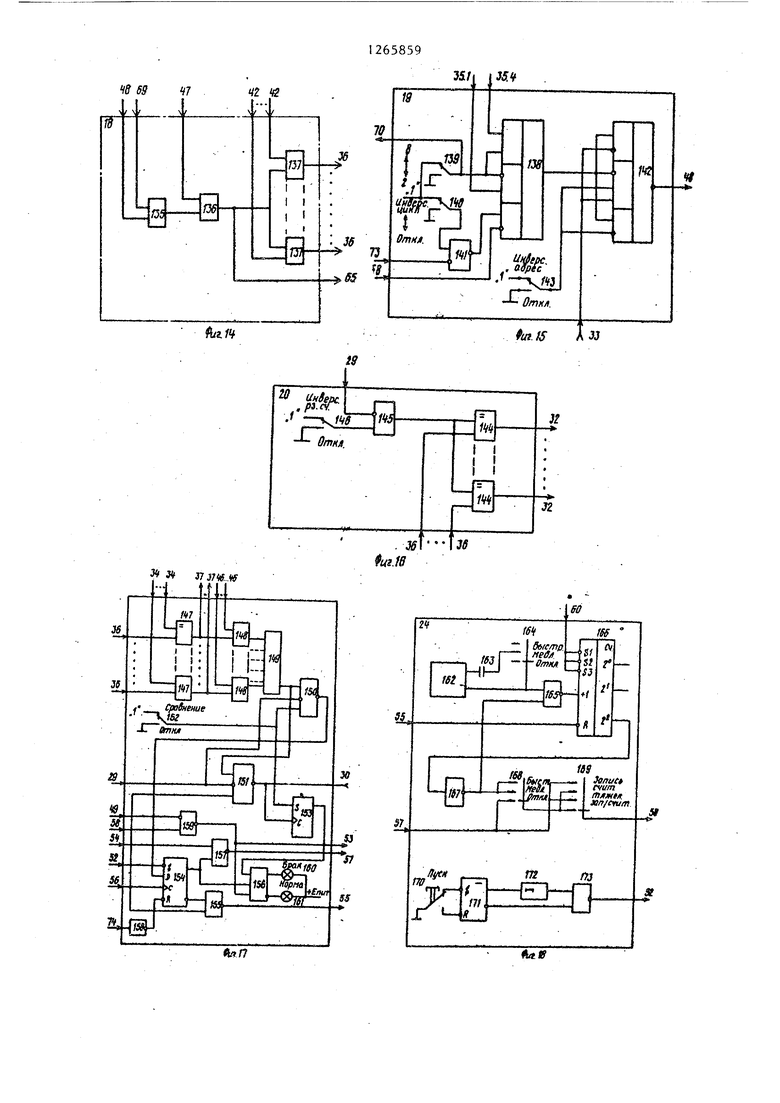

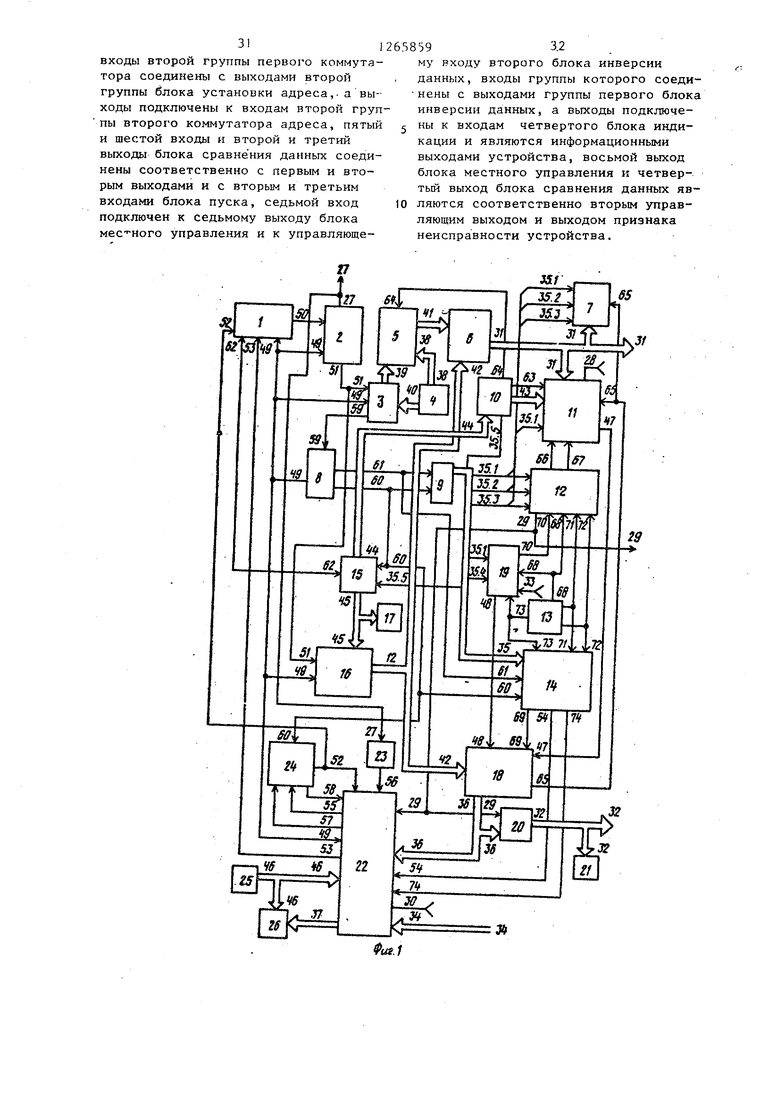

На фиг. 1 приведена схема устройства для контроля блоков оперативной памяти; на фиг. 2 - схема формирователя управляющих сигналов; на фиг.3 схема счетчика адреса; на фиг. 4 схема блока установки адреса;,на фиг. 5 - схема первого коммутатора; на фиг. 6 - схема блока сброса; на фиг. 7 - схема блока выбора адре.са синхронизации; на фиг. 8 - схема блока сравнения адресов и циклов; на фиг. 9 - схема блока формирования признака операции; на фиг. 10 - схема блока управления режимами; на фиг.11- схема блока формирования признака режима; на фиг. 12 - схема блока задания начального кода; на фиг. 13 - схема генератора псевдослучайного кода; на фиг. 14 - схема первого блока инверсии данных; на фиг, 15 - схема формирователя призна ка инверсии данных; на фиг. 16 - схема второго блока инверсии данных; на фиг, 17 - схема блока сравнения данных;на фиг, 18 - схема блока пуска, I

Устройство для контроля блоков оперативной памяти (фиг. 1) содержит генератор 1, формирователь 2 управляющих сигналов, счетчик 3 адреса, блок 4 установки адреса, первьм 5 и второй 6 коммутаторы, второй блок 7 индикации, блок В сброса,счетчик 9 циклов, блок 10 выбора адреса синхронизации, блок 11 сравнения адресов и циклов, блок 12 формирования признака операции, блок 13 управления режимами, блок 14 формирования признака режима, блок 15 задания начального кода, генератор 16 псевдослучайного кода, третий блок 17 индикации, первый блок 18 инверсии данных, формирователь 19 признака инверсии данных, второй блок 20 инверсии данных, четвертый блок 21 индикации, блок 22 сравнения данных, формирователь 23 сигнала опроса, блок 24 пуска, блок 25 коммутации, первьй блок 26 индикации, первый управляющий выход 27 -устройства (выход импульса обращения), выход 28 синхронизации, второй

658592

управляющий выход 29 (признак операции), выход 30 признака неисправное-, ти.

Блоки 12, 13, 14 и 19 со связями 5 образуют блок местного управления. На фиг. 1 показаны также связи 31-74.

Формирователь 2 управляющих сигналов фиг. 2) содержит элемент НЕ 75, элемент И-НЕ 76, элемент И 77, D триггер 78, элемент 79 задержки.

Счетчик 3 адреса (фиг, 3) содержит счетчик 80 дешифратор 81,

Блок установки адреса (фиг. 4) содержит коммутирующие элементы 82. 5 Первый коммутатор (фиг. 5) содержит первую 83 и вторую 84 группы - элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

Блок сброса (фиг. 6.) содержит элемент 85 задержки, элемент И 86, триггер 87, коммутирующий элемент 88, Блок 10 выбора адреса синхронизации (фиг, 7) содержит группу элементов И-НЕ 89, переключатель 90j элемент И-НЕ 91, группу элементов ИСКЛЮ 5 ЧАЮЩЕЕ ИЛИ 92, переключатели 93 и 94, Блок 1I сравнения адресов и циклов (фиг, 8) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 95, переключатели 96-99, элементы И-НЕ 100 и 101, эле30 мент И-ИЛИ-НЕ 102, элемент И 103.

Блок 12 формирования .признака операции (фиг, 9) содержит элементу,И-НЕ 104-107.

Блок 13 управления режимами 35 (фиг. 10) содержит коммутирующий элемент 108, триггер 109,

Блок 14 формирования признака режима (фиг, 11) содержит элементы И-НЕ 110-112, триггер 113, элемент 40 И-НЕ 114,

Блок 15 задания начального кода (фиг, 12) содержит счетчик 115, элементы И-НЕ 116 и 117, сдвигающий регистр 1 18, элементы И-НЕ 119-121, коммутирующий элемент 122, элемент И-НЕ 123, коммутирующие элементы 124-126.

Генератор 16 псевдослучайного кода (фиг, 13) содержит сумматор 127, коммутатор 1.28, группу элементов И-НЕ 129, регистр-130 числа, коммутирующие элементы 131 и 132, элемент 133 задержки, элемент И 134,

Первый блок 18 инверсии данных (фиг, 14) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 135-137,

Формирователь 19 признака инверсии данных (фиг, 15) содержит элемент И-ИЛИ 138, коммутирующие элементы 139 и 140, элемент И-НЕ 141, элемент И-ИЛИ-НЕ 142, коммутирующий элемент 143. Второй блок 20 инверсии данных (фиг. 16) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 144, элемент И 145, коммутирующий элемент 146. Блок 22 сравнения данных (фиг. 17 содержит группу элементов ИСКЛЮЧАЩЕ ИЛИ 147, группу элементов И 148, эле мент И 149,.элементы И-НЕ 150 и 151 коммутирующий элемент 152, триггеры 153 и 154, элементы И-НЕ 155-158, элемент ИЛИ-НЕ 159, элементы 160 и 161 индикации. Блок 24 пуска (фиг. 18) содержит мультивибратор 162, конденсатор 163, коммутирующий элемент 164, элемент И-НЕ 165, счетчик 166, инвертор ,167, коммутирующие элементы 168 и 169, кнопку )70 пуска, триггер 171, элемент 172 задержки, элемент И-НЕ 173 Устройство работает следующим образом. Режим проверки контролируемого блока памяти задается коммутирующими элементами 94 (в блоке 10 выбора адреса синхронизации), 108 (в блоке 13 управления режимами), 126 (в блоке 15 задания начального кода) и 169 (в блоке 24 пуска). Однократная запись с остановом. Для работы в этом режиме указанны .коммутирующие элементы устанавливают ся в положение Запись, При этом начальный код теста на выходах 45 блока 15 будет постоянным, равным коду, набранному оператором на комму тирующих элементах 124 в блоке 15 за Дания начального кода. Блок 13 форми рует сигналы управления на выходах 68, 71 и 73 - Лог. Г, а на вь1х6де .72 - Лог.О./. Нулевой потенциал с выхода 72 . поступает на вход 72 блока 12 управления режимами, где по этому сигналу формируется признак записи единич ного потенциала, который с выхода 29 блока 12 направляется на выход 29 устройства и далее в блок памяти. Кроме того, сигнал с выхода 29 блока 12 поступает на вход 29 второго бло ка 20 инверсии данных, не вызывая какой-либо реакции в его работе, а также на вход 29 блока 22 сравнения данных, где при этом запрещается формирование признака ошибки. В блоке 24 пуска в режиме Запись отключается схема автоматического пуска, так как после окончания записи по всем адресам блока памяти должен произойти останов без повторных пусков устройства. Затем оператор устанавливает в исходное состояние следующие узлы (блоки) устройства; в генераторе 16 псевдослучайных кодов выбирает нужный тест проверки (постоянный, сдвиговый или переменный); в генераторе 1 тактовых импульсов устанавличвает требуемый период обращения; в блоке 4 установки адреса устанавливает требуемую разрядность адреса; в блоке 15 заДания начального кода набирает нужный исходный код; при необходимости проверки тестом Инверсия по адресам включает коммутирующий элемент 143 в формирователе 19 признака инверсии числа, при этом необходимо врешней перемычкой соеди(нить вход- 33 с тем разрядом адреса на выходе 31 устройства, от которого должна производиться инверсия чисел. Затем оператор нажимает кнопку 88 Сброс в блоке 8 сброса. При этом на выходе 49 блока 8 сброса появляется обнуляющий потенциал, которьй устанавливает в исходное -состояние генератор I тактовых импульсов, формиг рователь 2 управляющих сигналов, счетчик 3 адреса, генератор 16 псевдослучайного кода и блок 22 сравнения данных.С выхода 60 обнулящий сигнал поступает в счетчик 9 циклов, в блок 5 задания начального кода и в блок 24 пуска. Сигналы, снимаемые с выходов-43 и 60 блока 8 сброса, устанавливают в исходное состояние перечисленные блоки и узлы устройства. Сигналы обнуления на блоки устройства поступают по разным 1шинам (49 и 60) так как по шине 60 посылается сигнал. только от нажатия кнопки 88, а по шине 49 - как от кнопки 88, так и по импульсу конца цикла, поступающему в блок 8 сброса по входу 59 с выхода переполнения счетчика 3 адреса. После установки в исходное состояние блоков и узлов устройства оператор нажимает кнопку 170 в блоке 24 пуска, на выходе 52 которого при этом формируется короткий импульс отрицательной полярности, который с выхода 52 направляется в блок 22 сравнения чи сел, где при этом на выходе 57 снимается сигнал запрета и появляется сигнал разрешения нулевой полярности поступающий далее через блок 24 пуска на вход 58 блока 22 сравнения дан ных, на выходе 53 которого при этом формируется единичный потенциал разрешения, поступающий на вход 53 гене ратора 1тактовых импульсов. При то генератор 1 начинает вырабатывать тактовую последовательность, которая с выхода 50 направляется на вход 50 формирователя 2 управляющих .сигналов на выходе 27 которого вырабатываются импульсы обращения к блоку памяти, а на выходе 51 - тактовые импульсы переключения счетчика 3 адреса. Таким образом, при каждом переключении счетчика 3 адреса формируется новьй код адреса, который.транслируется через первьш и второй коммутаторы 5 и 6 адреса на адресные выходы 31 уст ройства. Одновременно с появлением внеочередного адреса на выходе 27 формируется импульс обращения, посылаемый в блок памяти. Кроме того, в блоке 16 псевдослучайного кода формируется испытательный код, который транслируется через первый блок 18 инверсий числа, где при наличии признака инверсии на входе 48 код числа будет проходить на выход 36 в инверсной форме, а при отсутствии признака инверсии - в прямом коде. Затем код числа транслируется через второй блок 20 инверсии данных (в режиме Запись коды в блоке 20 не изменяются) на выходы 32 устройства, и далее испытательный код nocTynai T на ифнормационные входы блока памяти. При этом происходит запись .этого ко -, да по адресу, поступившему в блок па мяти с выходов 31 устройства. Код числа на выходе 32 устройства может изменять свое значение при каждом новом обращении в зависимости от выбранного оператором режима рабо ты генератора 16 псевдослучайного кода или от признака инверсии, посту пающего по входу 48 с формирователя 19 признака инверсии данных, что обеспечивает динамику смены кодов в отличие от режима статического изменения испытательного кода в известном устройстве. При достижении макси мального значения счетчиком 3 адреса на его выходе 59 появляется импульс конца цикла, который поступает в блок 8 сброса, на выходе 61 которого при этом формируется импульс,, которьй направляется на вход 61 блока 14 формирования признака режима., в результате чего на выходе 74 блока 14 появляется единичный потенциал окончания цикла записи, который поступает на вход 74 блока 22 сравнения чисел, где триггер 154 переключается в положение останова, на выходе 57 появляется потенциал, которьй транслируется через блок 24 пуска на вход 58 блока 22 сравнения. При этом на выходе 53 блока 22 появится нулевой потенциал, который поступает на вход 53 генератора I тактовых импульсов и останавливает его работу. В блоке 22 сравнения чисел гаснет элемент индикации НОРМА и зажигается - БРАК, что свидетельствует об окончании цикла записи испытательных кодов в блок памяти. Далее, в случае необходимости, блок памяти может вьщерживаться без каких-либо воздействий со стороны устройства контроля для проверки устойчивости хранения информации при отсутствии обращения к блоку памяти. После окончания цикла записи оператор может перевести устройство контроля в режим циклического считыва.ния. Для этого необходимо установить нужную разрядность блока 25 в соответствии с разрядностью блока памяти, переключить коммутирующие элементы 94 (в блоке 10), 108 (в блоке 13), 126 (в блоке 15) и 169 (в блоке 24) в положение СЧИТ (циклическое считывание). При этом с выхода 68 блока 13 управления режимами поступает нулевой потенциал на вход 68 блока 12 формирования признака операции, обуславливающий нулевой потенциал (признак считывания) на выходе 29, Затем оператор нажимает кнопку 88 в блоке 8 сброса. При этом, аналогично режиму записи, устанавливаются в исходное состояние блоки и узлы устройства. Затем оператор нажимает кнопку 170 в блоке 24 пуска, после чего, как и в режиме записи, генератор 1 начинает вьфабатывать тактовые импульсы, формирователь 2 формирует сигналы обращения на выходе 27 к блоку памяти. Одновременно импульс обращения поступает на вход 27 блока 23. Счетчик 3 адреса вырабатывает первый код адреса, направленньй через комму- таторы 5 и 6 на адресные выходы 31 устройства и далее на входные адресные шины контролируемого блока памя71ти. С выхода 29 блока 12 формирования признака операции ка вход блока памяти поступает нулевой потенциал, означающий признак считывания. По импульсу обращения из блока памяти считывается информация, которая была записана в цикуте записи по адресу, код которого в данный момент действует на выходах 31 устройства. При этом считанный из блока памяти код числа поступает по входам 34 устройства контроля на первую группу входов блока 22 сравнения данных, на вторую группу входов 36 которого в это время с генератора 16 псевдослучайного кода через первый блок I8 инверсий числа поступает код эталонного (ожидаемого) числа. На входе 29 блока 22 действует нулевой потенциал признака считывания, разрешающий прохождения.результата сравнения чисел (поступивших в блок 22 на схему 147 сравнения с входов 34 и 36) на D-вход D-триггера 154 (фиг. 17). С выхода 56 блока 23 в это время поступает сигнал опроса схемы сравнения Он задержан в блоке 23 относительно импульса обращения, поступившего в блок 23 по входу 27, на величину, соответствующую времени задержки информации, считанной из блока памяти, относительно импульса обращения. Сигнал опроса схемы сравнения по входу 56 поступает в блок 22 сравнения чисел на синхровход триггера 154 который записывает (и запоминает) результат сравнения, поступивший на его D-вход. Если сравнение произошло (коды чисел на входах 34 и 36 равны), то в триггер 154 запишется 1. В этом случае признака неравенства (импульс нулевой пoляpнocти на выходе 30 блока 22 не будет. Единичное состояние триггера J54 обусловит на выходе 57 нулевой потенциал равенства, который транслируется через блок 24 пуска на вход 58 блока 22, что обусловит единичный потенциал на выходе 53, который разрешает продолжить работу генератору 1 тактовых импульсов. Если же в триггере 154 запишется О, что свндетехшствует о неравенстве кодов на входах 34 и 36, то на выходе 30 появится признак ошибки, а на выходе 57 - единичный потенциал неравенства

который транслируется через блок 24 пуска на вход 58 блока 22 и далее через элемент ШШ-НЕ J59 на выход 53

информации в какой-то определенный и постоянный момент времени, но и вести измерение минимального времени 59 в виде нулевого потенциала, которьи направляется на вход 53 генератора 1 тактовых импульсов, прерывая его работу. При этом в блоке 7 индикации кода адреса высвечивается код адреса и признак инверсии, при которых зафиксирована ошибка. В блоке 21 индицируется эталонный код, в блоке 17 - начальный код тестовой программы, а в блоке 26 - те разряды числа, в которых произошло несравнение ожидаемой и считанной информации. При необходимости оператор может в блоке 25 отключить от сравнения те разряды, которые высветились в блоке 26 индикации неисправных разрядов при останове и нажатием кнопки 170 в блоке 24 пуска продолжить проверку блока памяти. Это позволяет определить количество неисправных разрядов в контролируемом блоке памяти, не приступая к диагностике ошибок с целью определения объема регулировки и оптимального пути локализации и нахождения ошибки. При отключении неисправных разрядов признак ошибки на выходе 30 блока 22 .сравнения чисел исчезает, что бывает не всегда удобно при диагностике ошибок с помощью о.сциллографа, когда признак ошибки на выходе 30 нужен для ориентирования на экране осциллографа. В этом случае необходимо подключить неисправный разряд в блоке 25 к схеме сравнения, но так как в этом случае будет происходить останов генератора 1 тактовых импуль сов, то это не позволит наблюдать на осциллографе в периодическом режиме развертки характер неисправности. В этом случае оператор отключает коммутирующий элемент 152 (фиг. 17) в блоке 22. При этом останов отключается, но на выходе 30 .будет появляться признак ошибки в момент ее обнаружения при непрерывном считывании информации из блока памяти. Рассмотренный режим работы, в отличии от известного устройства, позволяет проводить быструю диагностику обнаруженных ошибок. Кроме того, наличие ступенчатой задержки сигнала опроса схемы сравнения в блоке 23 по отношению к импульсу обращения с проградуиров нной шкалой задержки позволяет проверять не только наличие считанной выборки чиселиз блока памяти, так . как этот параметр предусматривается в технических характеристиках на блоки памяти. Режим тяжелой записи с многократной инверсной предысторией. Этот режим необходим для проверки магнитных оперативных запоминающих устройств, для которых характерна остаточная магнитная предыстория., связанная с накоплением намагниченности в ферритовых накопителях. Смысл режима с тяжелой записью заключается в том, чтобы многократно воздействовать на каждую ячейку памяти сигнала- js нию ми определенного знака, а затем произвести однократную запись кода противоположного значения . Это позволяет выявить неоптимальные соотношения сигналов временной диаграммы и токов в цепях записи и считьша.ние в блоках с магнитными накопителями информации В устройстве приведенный режим реализуется установкой коммутирующих элементов 94 (в блоке 10), 108 (в блоке 13), 126 (в блоке 15) и 169 (в блоке 24) в положение ТЯЖЕЛ. В этом режиме работы сброс в исходное состояние блоков и узлов и пуск устройства, а также формирование импульса обращения на выходе 27 и кодов адреса аналогичен рассмотренньм режимами работы. Режим тяжелой записи отличается от режима однократной записи тем, что в первые 31 циклов записи (цикл - время полного перебора значений счетчика 3 адреса в соответствии с .количеством счетных разрядов с вы хода 69 блока 14 формирования признака режима действует приэнак инвер сии, поступающий на вход 69 первого блока 18 инверсии числа. В результат этого в первые 31 циклов записываетс информация в обратном коде. Затем признак инверсии на выходе 69 блока 14 выключается и ведется ,один цикл (32-й записи прямого кода в испытуемый блок памяти. После этог триггер 119 (фиг. II) в блоке 14 переключается по положительному фронту импульса с выхода дешифратора 110 в единичное состояние, вызывая появление единичного потенциала на выходе 74 и нулевого - на выходе 54, которы направляются в блок 22 сравнения чисел, а затем, как и в режиме однократной записи, через блок 24 пуска обуславливают появление признака 1 5910 останова (.нулевого потенциала) на выходе 53, который направляется на вход 53 генератора 1 тактовых импульсов и останавливает его работу. В блоке 22 (фиг. 17) при этом гаснет элемент 161 индикации НОРМА, зажигается элемент 160 - БРАК, что означает окончание режима тяжелой записи, при котором бьш произведен 31 цикл записи в испытуемый блок памяти информации обратного кода и один цикл прямого кода. Это означает, что каждая ячейка магнитного накопителя была подвергнута 31 раз намагничиваодного знака, а затем один раз намагничиванию противоположного знака. После этого устройство контроля может быть переведено в режим считывания (см. описанный режим считывания). Если при этом ошибок в считанной информации нет, то это свидетельствует об оптимальном сочетании временной диаграммы сигналов управления и токов записи и считывания в магнитном блоке памяти. Введение режима контроля тяжелой записью расширяет область использования предлагаемого устройства по сравнению с известным. I Режим контроля с чередованием циклов записи и считьгаания. Для работы в этом режиме коммутирующие элементы 94 (в блоке 10), 108 (в блоке 13), 126 (в блоке 15) и 169 (в блоке 24) устанавливаются в положение ЗАП./СЧИТ. Цикличность работы определяется положением коммутирующего/элемента 139 в формирователе 19 признака инверсии данных. При установке элемента 139 в положение 2 устройство работает на 2 цикла - в первом осуществляется запись проверочных Кодов по всем адресам, а во втором - считывание со сравнением и фиксацией ошибок, и дгшее процесс контроля повторяется. При .установке коммутирующего элемента 139 в положение 8 устройство работает на 8 циклов - в первом производится запись проверочных кодов в блок памяти, а в следующих 7 циклах - считывание со сравнением и фиксацией ошибок, и затем процесс повторяется. При этом реализуется проверка работоспособности блока памяти тестом Разрушение считыванием, так как далее следуют еще 6 циклов считывания с проверкой сохранности информации после предыдущего считывания. Особенно это важно для блоков памяти с регенерацией информации, разрушающейся в магнитном накопителе при считывании. В исходное состояние устройство приводит ся нажатием кнопки 88 в блоке 8 сбро са. При этом блоки и узлы устройства устанавливаются в начальное состояни как и в рассмотренных режимах контро ля. На входы 68, 71 и 72 блока 12 . формирования признака операции посту пают с соответствующих выходов блока 13 управления режимами разрешающие единичные потенциалы. Режим формирования признака опера ции в блоке 12 зависит от цикличност работы, определяемой, как указывалос коммутирующим элементом 139 в формирователе 19. Допустим, элемент 139 установлен в положение 2, в этом случае на вход 70 из блока 19 поступает нулевой потенциал, запрещающий прохождение сигналов через элементы И-НЕ 105 и 106 в блоке 12. При этом на дешифратор 104 признака операции поступают сигналы только с первого разряда счетчика 9 циклов (по входу 35.1). В первом цикле со счетчика 9 циклов по входу 35.1 приходит нуле вой потенциал, который обуславливает на выходе 29 блока 12 единичный потенциал, т.е. признак записи, направ ляющийся с выхода 29 устройства на вход блока памяти и в блок 22 сравнения данных.В блоке 22 в цикле Запись запрещается сравнение информации. После перебора всех значений счетчиком 3 адреса (т.е. окончания записи по всем адресам) импульс пере полнения со счетчика 3 адреса поступает, на вход 59 блока 8 сброса. При этом на выходе 61 .блока 8 сброса появится импульс, который поступает в счетчик 9 циклов и переключает его в состояние I, т.е. первый разряд будет находиться в положении 1, а остальные 2-5 разряды - в положении О, В этом случае на вход 35.1 блока 12 поступит единичный потенциал, который обусловит появление нулевого потенциала (признак считывания ) на выходе 29 блока 12, который посылает на выход 29 устройства и. перекл}очает блок памяти в режим считывания, одновременно разрешая бдоку 22 производить сравнение считанной и эталонной информации с фиксацией ошибок. После завершения цикла считы вания (если ошибки в блоке 22 сравнение данных не зафиксированы) снова начинается цикл записи и работа повторяется. Если при считывании в каком-либо адресе фиксируется ошибка, то блок 22 при взаимодействии с блоком 24 пуска формирует сигнал нулевой полярности на выходе 53, которьй, поступая в генератор 1 тактовых импульсов, останавливает его работу. При этом в блоках индикации 7,17,21 и 26 высвечиваются, соответственно, код адреса, начальный код тестовой программы, код эталонного числа и номера неисправных разрядов. При нажатии кнопки 170 в блоке 24 пуска устройство -продолжит контроль до следующего адреса с неверно считанной из блока памяти информацией. Если в формирователе 19 коммутирующий элемент 139 установлен в положение 8, то на вход 70 блока 12 формирования признака операции поступает единичный потенциал, разрешающий прохождение сигналов второго и третьего разрядов счетчика 9 циклов, поступающих По входам 35.2 и 35.3 через элементы ИНЕ 105 и 106 (фиг. 9) на входы дешиф ратора 104. При этом в первом цикле работы на выходе 29 блока 12 будет единичный потенциал - признак записи, а в циклах с второго по восьмой, в соответствии с кодами счетчика 9 циклов, будет нулевой потенциал, т.е. на выходе 29 будет признак считывания , Рассмотренные режимы циклического чередования операций записи и считывания имеют принципиальное отличие от режима проверки блоков памяти в известном устройстве, выражающееся в том, что коды адреса изменяются с максимальной частотой, предусмотренной техническими характеристиками на данный блок памяти. Кроме того проверочные коды на выходах 32 устройства могут изменяться в каждом новом адресе по программе, выбранной оператором. Это обеспечивает комбинированную проверку блока памяти на максимальное быстродействие при одновременной проверке блока памяти на кодовую устойчивость и на устойчивость к разрушению информации считыванием. Формирование тестовой программы. Проверочные коды данных, посылаемые в испытуемый блок, формируются

при взаимодействии блока 15 задания начального кода, генератора 16 псевдослучайных кодов и первого блока 18 инверсий числа.

Кодовые комбинации могут формироваться как с постоянным, так и с переменным начальным кодом.

Режим формирования проверочных кодов в генераторе 16 псевдослучайных кодов при постоянном начальной коде устанавливается оператором с помощью коммутирующих элементов 90 (в блоке Ю), 122 и 125 (в блоке 15), которые в этом случае должны быть установлены в положение ПОСТ, (постоянный начальный код). Далее оператор набирае нужный код числа на коммутирующих элементах 124 (фиг. 12) блока 15 задания начального кода и при нажатии кнопки 88 (фиг. 6) в блоке 8 сброса вводит этот код в блок 15, с выходов 45 которого этот код поступает в генератор 16 псевдослучайного кода, где в зависимости от теста, установленного оператором с помощью коммути рующих элементов 131 и 132 (фиг. 13) и формируется тестовая программа. Если элементы 131 и 132 установлены в положение ПОСТ., то этот код с приходом сигнала начальной установки, поступающего по входу 49 в генератор 16 псевдослучайного кода, переписывается в регистр числа 130 и появляется на выходах 42 и затем направляется через первый блок , 18 инверсии данных на входы 36 блока 22 сравнени данных и далее через второй блок 20 инверсии чисел - на выходы 32 устройства и затем на информационные входы блока памяти. В этом режиме, работы блока 15 задания начального кода и генератора 16 псевдослучайного кода информация на их выходах 45 и 42.остается постоянной во всех адресах и циклах проверки и может измениться лишь переключением коммутирующих элементов 124 в блоке 15 задания начального кода,

. Лри установке коммутирующих, элементов 131 и 132 в генераторе 16 псевдослучайного кода в положение СДВИГ, (сдвигающий код) на выходах. 42 генератора б формируются проверочные коды, изменяющиеся при каждом новом обращении к блоку памяти, путем сдвига начального кода, поступившего по входам 45, на один разряд в сторону старших разрядов с кольцевым

переносом из старшего в младший разряд. Этот режим позволяет формироват тесты типа Бегущая 1 или О по разрядам информационного слова или тест Шахматньй код (т.е. чередующийся код 1010...10 со смещением.по адресам) или двигающиеся тесты с произвольным начальным кодом, установленным в блоке 15 задания начального кода. Тест Бегущая 1 или О по разрядам повзоляет выявлять кодовую неустойчивость блоков памяти при воздействии на один из информационных разрядов сигналом одной полярности, а на другие - сигналами противоположного знака со смещением 1 (О) при каждом новом обращении. Тест Шахматный код выявляет межразрядные влияния в магнитных накопителях При установке коммутирующих элементо 131 и 132 в положение ПЕРЕМ. (переменньй или псевдослучайньш код) на выходах 42 генератора 16 формируютсяпроверочные коды, изменяющиеся при каждом новом обращении по псевдослучайному закону. Псевдослучайные коды обеспечивают проверку блоков памяти в условиях, аналогичных реальным, существующим в условиях обмена информацией между ЦВМ и блоком памяти. Псевдослучайные коды позволяют выявлять наиболее тяжелые кодовые комбинации для каждого конкретного блока памяти. Недостатком рассмотренного псевдослучайного режима формирования кодов при постоянном начальном коде на входах 45 генератора 16 является то, что по окончании полного этапа проверки блока памяти - под этапом следует понимать 2 цикла (один - записи и один - считывания при цикличности работы 2) или 8 циклов (один цикл записи и семь - считывания при цикличности работы устройства 8) запись информации в блок памяти в следующем цикле записи будет в каждом адресе точно повторять информацию, записываемую в тех же адресах предьщущего этапа проверки, т.е. информация в каждом данном адресе остается неизменной на разных этапах проверки. Для поэтапной смены информации необходимо изменять начальный код тестовой программь на входах 45 генератора 16 псевдослучайного кода. Это осуществляется в блоке 15 задани начального кода.

Режим формирования начального кода путем сдвига исходного кода. 15, Для работы в этом режиме оператор устанавливает коммутирующие элементы 122 и 125 в блоке 15 задания начального кода (фиг. 12) в положение РгС (сдвиговый регистр). Затем оператор набирает нужный исходньш код на коммутирующих элементах 124 и нажатием кнопки 88 в блоке 8 сброса вводит ис ходный код в счетчик 115 исходных ко дов и в сдвигающий регистр 118 в блоке 15 задания начального кода). При этом на выходах 45 будет начальный код первой тестовой программы. После пуска(нажатием кнопки 170 в блоке 24 пуска) начинается формирова :ние проверочных кодов в генераторе 16 псевдослучайных кодов в зависимости, от выбранного-оператором вида теста, установленного в генераторе 16. Проверочные коды, являющиеся производными от начального кода на входах 45 генератора 16,формируются в течение 32 полных циклов проверки блока памяти, после чего по входу 35.5 блока 15 задания начального кода постулит отрицательный фронт перепада потенциалов (так как счетчик 9 циклов 5-разрядньш), который, попадая на синхровход сдвига сдвигающего регистра сдвинет информацию в нем на один разряд в сторону старших разрядов. После этого генератор 16 псевдослучайного кода будет форми ровать новые проверочные коды в тече ние .следующих 32 полных циклов проверки блока памяти, после чего снова произойдет сдвиг начального кода на выходах 45 блока 15 задания начально го кода. Таким образом, обеспечивает ся автоматическая смена информации в каждом адресе в последующих 32 цик лах контроля по отношению к коду числа в том же адресе в предыдущих i32 циклах проверки блоков памяти. Режим формирования начального кода по принципу +1 к исхбдному коду Для работы в этом режиме оператор устанавливает коммутирующие элементы 122 и 125 в блоке 15 задания начального кода в положение СЧ.ИК (счетчик исходных кодов). Затем набирает нужный исходный код на коммутирующих элементах 124 и нажатием кнопки 88 (в блоке 8 сброса) вводит этот код в счетчик 1 15 исходных ijoдов и в сдвигающий регистр 118. При этом на выходах 45 будет начальный код первой тестовой програм1«л, После 5916 . пуска устройства начинается формирование проверочных кодов в генераторе 16 псевдослучайных кодов в зависимости от выбранного оператором вида теста, установленного в генераторе 16. Проверочные коды, являющиеся производными от начального кода на входах 45 генератора 16, формируются в течение 32 полных циклов проверки блока памяти. Причем после 16 циклов на вход 35.5 блока 15 задания начального кода поступит положительный фронт перепада потенциалов, который, пройдя через элемент И-НЕ 1.16, поступит в виде отрицательного фронта на вход +1 счетчика 115 исходных кодов и переключит его в очередное состояние, а на вход С2 сдвигающего регистра 118 в это время поступит положительный Фронт, который не изменяет состояния сдвигающего регистра М 8. После следующих 16 циклов контроля (32-й цикл) по входу 35.5 поступит отрицательный фронт перепада потенциалов, который не изменяет состояния счетчика 115 и исходных кодов, но записывает новую информацию в сдвигающий регистр 118, поступившую на его Dвходы с выходов счетчика 115 исходных кодов. В результате на .выходах 45 появится новый начальный код другой тестовой программы, отличающийся от прежнего начального кода на +1. Таким образом, каждые 32 цикла проверки блока памяти на выходах 45 блока 15 будет изменяться начальный код тестовой программы на +1 по отношению к исходному коду, набранному на коммутирующих элементах 124 блока 15 задания начального кода. Формирование начального кодана входах 45 генератора 16 псевдослучайного кода по принципу перебора всех возможных значений позволяет вырабатывать в автоматическом режиме псевдослучайную последовательность при установке элементов 131 и 132 в генераторе 16 в положение ПЕРЕМ. со всеми возможными кодовыми комбинациями в каждом адресе блока памяти. Это обеспечивает проверку блоков памяти в автоматическом режиме на кодовую ; устойчивость при максимальной частоте смены адресных и проверочных кодов. . Рассмотренный режим формирования начальных кодов позволяет находить наиболее тяжелые кодовые комбинации ля каждого конкретного блока оперативной памяти. При нахождении такого начального кода, который высвечивает ся в блоке 17 при останове по обнару женной в блоке памяти ошибке, необходимо набрать его на коммутирующих элементах 124 блока 15, переключить ко 1мутирующие элементы 122 и 125 в положение ПОСТ. При этом начальный код на входах 45 генератора 16 псевдослучайного кода не будет менять своего значения во всех циклах проверки. Затем оператор выясняет причи ны неустойчивой работы блока памяти при записи кодами данной тестовой последовательности, Проверочные коды, формируемые в блоках 15 и 16 устройства, записываются в блок памяти по адресам, которые формируются с упорядоченным порядком следования или с псевдослучайным в зависимости от режима, выбранного оператором. Формирование упорядоченных кодов адреса. Для работы в этом режиме формирования адресов коммутирующие элементы во втором коммутаторе 6 адреса устанавливаются в положение, обеспечиваю щее трансляцию кодов адреса с выхода 41 первого коммутатора 5 адреса на выходы 31 устройства. Перед пуском устройства оператор устанавливает на коммутирующих элементах 82 блока 4 установки адреса необходимую разрядность счетчика 3 адреса в соответствии с информационной емкостью испытуемого блока памяти. Так, например для проверки блоков памяти емкостью 8К слов необходимо коммутирующие эле менты 82 (фиг. 4) с 1-го по 13-й установить в положение СЧЕТ., а осталь , ные (14-й, 15-й, 16-й) - в положение О. При этом на часть входов (с 1-г по 13-й) группы входов 40 счетчика 3 адреса (фиг. 3) с соответствующих выходов 40 блока 4 установки адреса поступают единичные потенциалы, а на 14-й, 15-й и 16-й входы-группы входов 40 - нулевые. Следовательно, первые i 3 разрядов счетчика 3 адреса будут работать в счетном режиме а остальные установлены в единичное . состояние, С выходов 38 (с 1-го по 13-й) блока 4 установки адреса единичные потенциалы поступят на соответствующие входы 38 первого коммутатора 5 адреса (фиг. 5), а на остальные входы (14-й, 13-й и 6-й) 59« группы входов 38 поступят нулевые потенциалы. В результате на первых 13 выходах группы выходов 41 первого коммутатора 5 адреса будут сигналы, соответствующие сигналам на соответствующих выходах 39 счетчика 3 адреса при работе его в счетном режиме при поступлении тактовых импульсов по входу 51, а на остальных (14-м,15-м и 16-м) выходах будут нулевые потенциалы в соответствии с положением коммутирующих элементов 82 в блоке 4 установки адреса. Если же какие-либо коммутирующие элементы 82 в блоке 4 установки адреса будут установлены в положение 1, то на соответствующих выходах из группы выходов 41 первого коммутатора 5 адреса будут потенциалы 1. Таким образом, положение коммутирующих элементов 82 в блоке 4 установки адреса определяет форму сигналов на выходах 41 первого коммутатора 5 адреса, т.е. установка любого разряда блока 4 установки адреса в положение О обуславливает на соответствующем выходе 41 нулевой потенциал, установка коммутирующих элементов 82 в блоке 4 адреса в - на соответствующих выходах 41 первого коммутатора 5 адреса единичньй потенциал, а на выходах 41 остальных разрядов будут потенциалы переключения счетных разрядов счетчика 3 адреса независимо от количества и места расположения разрядов, зафиксированных в положение 1 или О путем yctaнoвки в указанные положения соответствующих коммутирующих элементов. Так формируются коды адреса в режимах работы с возрастающим порядком выбора адресов. Если,же в устройстве оператором выбран контрольный тест проверки блока памяти Бегущий 0,1 (по адресам), то в определенной части циклов конгроля. Подробнее режим проверки тестом Бегущий 0,1 будет рассмотрен. На вход 4 первого коммутатора 5 адреса поступит признак инверсии в виде единичного потенциала. При этом коды адреса со счетчика 3 адреса будут проходить, через коммутатор 5 адреса в инверсной форме, что будет соответствовать убывающему, но упорядоченному порядку формирования ко ДОН адреса, которые транслируются затем через второй коммутатор 6 адреса на выходы 31 устройства и далее на 19 адресные входы проверяемого блока памяти. Предложенная схема формирования кода адреса в отличие от известного устройства позволяет устанавливать каждый разряд адреса в любое из трех состояний - 1, О или Счет. Это дает возможность проверять блоки памяти различной емкости, отключая лиш ние разряды с помощью коммутирующих элементов 82 в блоке 4 установки адреса. Кроме того, такое построение позволяет осуществлять оперативную диагностику неисправностей путем уменьшения массива проверяемых адресов в блоке памяти, устанавливая определенные коммутирующие элементы 82 в блоке 4 установки адреса в положения, высвечиваемые в блоке 7 индикации адреса при останове по несравнению считанной и эталонной информации. Это позволяет быстро выйти на определенный неисправный адрес или минимальный массив адресов блока памяти, при котором фиксируется ошиб ка. Формирование кодов адреса, изменяющихся по псевдослучайному закону. Для работы в этом режиме коммутирующие элементы во втором коммутаторе 6 остаются в положении, транслирующем коды с выходов 42 генератора 16 псевдослучайных кодов на адресные выходы 31 устройства. В блоке 5 задания начального кода коммутирующие элементы 122 и 125 устанавливаются в положение СЧ.ИК (счетчик исходных кодов), все коммутирующие элементы 124 устанавливаются в положение О, В генераторе 16 псевдослучайного кода коммутирующие элементы 131 и 132 должны быть установлены в положение ПЕРЕМ, Затем устройство пускается в работу. Режим формирования адресов при этом аналогичен предьщущему режиму с той лищь разницей, что послезавершения каждых 32 циклов работы начальный код в блоке 15 изменяется не путем сдвига исходного кода, набранного на коммутирующих элементах 124, а путем изменения исходного кода на +1. При этом порядок формирования начальных кодов имеет упорядоченную структуру. Формирование теста Бегущий 0,1 в прямом и обратном порядке перебора адресов. Для работы в этом режиме оператор устанавливает коммутирующие элементы 90 (в блоке 10), 122 и 125 (в блоке 15) в положение БЕГУЩ., элементы 94 (в блоке 10), 108 (в блоке 13), 126 (в блоке 15) и 169 (в блоке 24) в положение ЗАП/СШГГ., элементы 131 и 132 в генераторе 16 - в положение ПОСТ., элемент 139 (в формирователе 19) - в положение 8, элемент 140 (в формирователе 19) - в положение ИНВЕРС. ЦИКЛ., все элементы 93 (в блоке 10) - в положение О. В блоке 15 задания начального кода коммутирующие элементы 124 устанавливаются в положение 1 или соответстВИИ с информационной емкостью проверяемого блока памяти, например, для блока памяти емкостью 8К слов в блоке 15 необходимо первые 13 коммутирующих элементов установить в положение О, а остальные с 14-го по 20-й - в положение 1. В блоке 4 установки адреса первые 13 коммутирующих элементов 82 при этом должны быть установлены в положение СЧЕТ, а 14-й, 15-й и 16-й элементы 82 в положение 1. Рассмотрим работу устройства при проверке блока оперативной памяти емкостью 8К слов в режиме Бегущий 0,1. В первом такте работы первого цикла проверки блока памяти с выходов 31 второго коммутатора 6 адреса О поступает код с в первых тринадцати разрядах и с 1 в 14-м, 15-м И 16-м разрядах на выходы 31 устройства и на входы 31 блока 11 сравнения адресов и циклов. При этом с выходов 44 и 45 код числа с О в первых 13 разрядах и I в остальных 14-20 разрядах направляется, соответственно , на входы 44 блока 10 выбора адреса синхронизации и на входы 45 генератора 16 псевдослучайного кода. С выходов 42 генератора 16 код числа без изменения поступает ка входы 42 первого блока 18 инверсии числа. С выходов 43 блока iO выбора адреса синхронизации начальный код в инверсном виде поступает в блок 11 сравнения адресов и циклов. При этом на обоих входах 31 и 43 схемы 95 сравнения в блоке I1 будут противоположные значения на всех разрядах, что соответствует равенству кодов на входах 31 и 43. При этом на выходе 28 блока II будет нулевой потенциал, а на выходе 47 - единичный (признак равенства). С выхода 47 признак ра21венства поступает в первый блок 18 инверсии числа на вход 47. По этому признаку код числа в блоке 18 инвертируется и в таком виде поступает на входы 36 блока 22 сравнения чисел, а также через второй блок 20 инверсии числа направляется через выходы 32 и информационные входы блока памяти. Таким образом, при равенстве кодов (прямого и обратного) на входах 31 и 43 блока 11 сравнения информация на информационные вхо ды блока памяти поступит в инв.ерсном .виде и будет записана в блок памяти в нулевой адрес. При следующем обращении с выходов 31 второго коммутатора 6 адреса поступит первьй код адреса, .который направляется на адресные выходы устройства и на входы 31 блок-а 11 сравнения, а на входах 43 будет по-прежнему начальный код, поступающий с выхо дов 44 блока 55. При этом блок 11 зафиксирует неравенство, т.е. на выходе 47 признак инверсии исчезнет и первый блок 18 инверсии чисел пропустит код числа на выходы 36 в прямом виде, который через второй блок 20 инверсии пройдет на информационные входы блока памяти и по импульсу обращения запишется в него. В дальнейшем по мере переключения разрядов счетчика 3 адреса блок 1I будет фиксировать неравенство значений на вхо дах 31 и 43, в результате чего на его выходе 47 признака равенства не будет и все последующие коды будут проходить в блок памяти и записывать ся в прямом коде. Пожгла цикла записи начнется цикл считывания. Снова в нулевом адресе сформируется на выходах 36 блока 18 инверсный код, который поступает на входы 36 блока 22 сравнения чисел. По импульсу обращения из блока памяти выводится число, которое поступает по входам 34 в блок 22, где оно сравнивается с эталонным на входах 36. В случае неравенства происходит останов с индикацией кода неисправно го адреса, цикла признака инверсии, эталонного кода и неисправных разрядов. При равенстве кодов на входах 34 и 36 блока 22 сравнения чисел уст ройство переходит к следующему такту и проверяет правильность считывания числа из блока памяти по первому адресу. При этом все считанные в адре5922сах с 1-го по п-1 (в нашем случае ) числа должны быть в прямом коде по отношению к числу нулевого адреса, где бьша записана инверсная Информация, так осуществляется семь циклов считывания с целью проверки блока памяти на неразрушаемость информации при многократном считывании. При завершении каждого цикла контроля счетчик 9 циклов переключается в очередное состояние. После завершения 8-го цикла контроля (-запись и 7-считывание на четвертом выходе 35.4 из группы выходов 35 счетчика циклов появится единичный потенциал, поступающий на вход 35.4 формирователя 19 признака инверсии числа, на выходе 48 которого при этом появится признак инверсии, который, попадая на вход 48 первого блока 18 инверсии числа, обусловит прохождение кодов через него с входов 42 на выходы 36 в инверсном виде в следующих 8 циклах работы по отношению к предыдущим В циклам. После окончания 16-го цикла на пятом выходе 35.5 группы выходов 35 счетчика 9 циклов появится единичный потенциал, который поступает на вход 35.5 блока 10 выбора адреса синхрог низации, в результате чего коды на выходах 43 будут иметь инверсное значение, а на выходе 64 появляется признак инверсии {единичный потенциал), который поступает в первый коммутатор 5 адреса. При этом коды адреса через первый коммутатор 5 адреса будут проходить в инверсном виде, что обусловит выборку чисел из блока памяти в обратном (убывающем порядке) в течение следующих 16 циклах контроля. После окончания 32-го цикла контроля блок 15 задания начального кода переключит свое состояние на +1. Новый код поступит через блок 10 на входы 43 блока 11 сравнения адресов и циклов. В этом случае при прохождении нулевого адреса, код которого содержит О в первых 13 разрядах (для блока памяти емкостью 8192), схема сравнения в блоке 11 не зафиксирует равенство и в отличие от первых 32 циклов работы при нулевом адресе признака и вepcии на выходе 47 не будет. Следовательно, в нулевом адресе проверочная информация будет записана в блок памяти в прямом коде. Затем счетчик 3 адреса сформирует код первого адреса, который поступит через коммутаторы 5 и 6 на адресные выходы 31 устройства и на вход- 31 . блока II сравнения адресов и циклов. Схема сравнения в блоке 11 при этом зафиксирует равенство и на выходе 47 появится признак инверсии. Следовательно, в следующих 32 циклах будет проверяться устойчивость записи, хра нения и считывания информации в первом адресе блока памяти при воздейст вии на все другие адреса кодами инверсного содержания по отношению к коду первого адреса при прямом -и обратном порядкеследованияадресой7 В третьих 32 циклах работы будет проверяться устойчивость 2-го адреса затем 3-го и т.д. до тех пор, пока все адреса не пройдут проверку на устойчивость работы в режиме Долбление по другим адресам кодами противоположного значения. Следует отметить, что в отличие от известного устройства испытательные кодь1, запи.сываемые в блок памяти в режиме Бегущий 0,1, меняют свое значение каж дые 32 цикла, что обеспечивает проверку не только адресной части блока памяти, но и разрядной. Такая комбинированная проверка позволяет выявлять более сложные дефекты блоков па мяти, котррые обнаруживаются при раздельной проверке адресной части тестом Бегущий 0,1,а разрядной тест-ом с нарастающим значением записываемой информации в два этапа. Формирование проверочных кодов с инверсией по адресам, циклам и признаку операции. В устройстве предусмотрены режимы контроля блоков памяти инверсными кодами (помимо инверсных кодов в режиме тяжелой записи и инверсий в режиме проверки тестом Бегущий 0,1 которые позволяют обнаруживать и локализовать определенный класс ошибок более простым путем, чем-сложньШ и. дпительный тест Бегущий 0,1. Тест проверки с инверсией кодов по адреса заключается в том, что проверочные коды, посылаемые в блок памяти с выходов 32 устройства, инвертируются от адреса к адресу или через 2 адреса, через 4,8 и т.д., т.е. через К адресов, где , ,2.. . 1б .(16.максимальная разрядность счетчика 3 адреса в опытном образце устройства) Для реализации режима инверсии по ад ресам необходимо включить коммутирую ций элемент 143 в формирователе 1 признака инверсий числа (фиг. 15) в положение ИНВЕРС. АДРЕС- и соединитьвнешней перемычкой вход 33 формирователя 19 с тем разрядом адресной шины 31 устройства, от которого.необходимо получить инверсии чисел) Так, например, если соединить вход 33 с первым выходом группы адресных выходов 31, то признак инверсии будет появляться на выходе 48 формирователя 19 через адрес - в нечетных адресах, т.е. в 1,3,5 и Т;Д-. , а в четных адресах 0,2,4,6 и т.д. признака инверсии на выходе 48 формирователя 19 не . Признак инверсии поступает на вход 48 первого блока 18 инверсии чисел и обуславливает прохождение кода через него с входов 42 на выходы 36 в инверсном виде. Следовательно, в нечетньк адресах на выходы 32 уст.ройства будут поступать инверсные коды, а в четных - прямые. Если же вход 33 формирователя 19 соединить с вторым выходом -из группы адресных выходов 31, то признак инверсии на выходе 48 будет появляться через два адреса, т.е. в 2,3,6,7 и т.д..адресах, а в других адресах, т.е. 0,1,4,5 и т.д., признака инверсии не будет, Это обусловит формирование,,, соответственно, инверсных и прямых проверочных кодов в указанных адресах на выходах 32 устройства. Таким образом, соединяя вход 33 формирователя 19 с любым из 16 выходов группы адресш 1Х выходов 31, можно получить 16 различных программ формирования инверсных кодов. Эти коды характерны тем, что позволяют быстро обнаруживать дефекты в микросхемах полупроводниковых накопителей типа двойная (или п-кратная) выборка кpиcтaJйla. Тест проверки блоков памяти кодами с .инверсией по циклам заключается в смене информации на обратную через 2 или 8 циклов в зависимости от положения коммутирующего элемента 139 в формирователе 19 признака инверсии числа. При этом каждые 2 цикла (или 8 циклов) будет формироваться призрак инверсии на выходе 48. При одновременном включении коммутирующих элементов 140 и 143 на выходе 48 будет формироваться признак комбинированной инверсии (по адресам и циклам). Тест проверки блоков памяти кодами с инверсией по признаку операции Тест хар.актеризуется тем,что при операции Считывание с выходов 32 устройства на входные информационные шины блока памяти поступают кодь инверсного содержания по отношению к ожидаемому коду, которьш считывается из блока памяти и направляется по входам 34 в блок 22 сравнения чисел. Тест реализуется включением коммутирующего элемента 146 во втором блоке 20 инверсии числа в положение ИНВЕРС Рз. Сч. (инверсия разрядов записи пр считывании). В этом случае при по- ступлении на вход 29 второго блока 2 инверсии числа нулевого потенциала (лризнак считывания) эталонньш код с входов 36 транслируется на выходы 32 в инверсном виде, а при наличии признака записи (единичный потенциал) на входе 29 код эталонной информации транслируется через блок 20 без изменения . Формирование инверсных кодов по любому выбранному адресу. Этот режим характеризуется тем, что оператор может по своему усмотре нию выбрать любой адрес блока памяти в котором информация будет записываться и считываться из него в инверсном коде по отношению ко всем ос тальным адресам. Этот режим считается диагностическим и используется в случае обнаружения ошибок тестом ,, Бегупщй 0,1. Дпя реализации режима оператор устанавливает коммутирующий элемент 90 в блоке 10 выбора адреса синхронизации в положение СЧ. ИК. или РгС. 1ш1к ПОСТ, (в зависимое ти от режима формирования начальных кодов блока 15), а на коммутирующих . элементах 93 набирает код адреса, в котором требуется записывать инфор мацию в блок памяти в инверсном коде В формирователе 19 коммутирующий эле мент 143 включается в положение ИНВЕРС.АДРЕС. Затем оператор соединяет внешней перемычкой выход 28 бло ка I1 сравнения адресов и циклов и вход 33 формирователя 19 признака ин Bepctm числа, а коммутирующие элемен ты 96-98 устанавливает в положение, соответствующее коду номера г(икла, в котором будет производиться инверсия числа в выбранном адресе. Коммутирующий элемент 99 при этом должен быть установлен в положение 1 (т.е 59 26 в этом разряде схемы 95 сравнения фиксируется наличие признака инверсии, поступившего по входу 65). В этом случае при контроле блока памяти во время прохождения выбранного адреса, код которого попадает по входам 43 на схему 95 сравнения блока 11, на выходе 28 сформируется признак инверсии (единичный потенциал), который, попадая на вход 33 формирователя 19, обусловит на его выходе 48 признак инверсии, которьй направляется на вход 48 первого блока 18 инверсии числа. В результате этого код эталонного числа в выбранном адресе транслируется через блок 18 с входов 42 на выходы 36 в инверсном виде. При прохождении любых других адресов или в других циклах, не выбранных оператором, блок II сравнения.адресов и циклов выдает на выходе 28 нулевой потенциал (т.е..признака сравнения нет), который, попадая на вход 33 ,. формирователя 19, обуславливает на выходе 48 нулевой потенциал, свидетельствующий об отсутствии признака инверсии, который поступает на вход 48 первого блока 18 инверсий нисла, в результате этого числа с входов 42 транслируются через блок 18 на входы 36 в прямом коде. Рассмотренный тест позволяет исследовать устойчивость работы любого из адресов в определенном цикле при воздействии на него информацией инверсного содержания по отношению к информации записываемой по всем другим адресам, или в другом цикле проверки. Причем выбранный адрес и цикл может быть сменен только путем переключения коммутирующих элементов 93 в блоке 10 выбора адреса синхронизации и элементов 96-98 в блоке П сравнения адресов и циклов. Формирование инверсных кодов с псевдослучайным распределением информации . Пров.ерка блоков памяти в тяжелых режимах контроля с инверсией по адресам, циклам и признаку операции в сочетании с псевдослучайным распределением информации обеспечивается в двух вариантах: 1. При комбинации ранее рассмотренных режимов тяжелой записи с включением теста Псевдослучайный код в генераторе 16 псевдослучайного кода и одновременном включенин режима илверсии по адресам, а при послелующем переводе в режим считывания и свк.таочением инверсии по признаку операции. 2. При комбинации ранее рассмотренных режимов контроля с чередованием циклов записи-считывания с режимом формирования кодов адреса с циклическим сдвигом младшего разряда адреса или с режимом формирования кодов адреса, изменяющихся по псевдо случайному закону с одновременной ин версией информации по адресам, цикла и признаку операции (или без инверсий ). Такие комбинации режимов создают тяжелые условия работы блоков памяти позволяющие вьювлять дефекты более высокого порядка, которые не обнаруживаются при проверке блоков памяти каждым из приведенных режимов в отдельности. Диагностические режимы работы устройства. , . i .„, При останове устройства в резуль тате обнаружения неисправности при контроле блока памяти в блоке 7 инди кации адреса высвечиваются код адреса и код цикла, при котором произоше останов. Кроме того, индицируется признак инверсии, указывающий, при прямом или инверсном проверочном код произошел останов.. Для локализации неисправности оператор сужает област oпJpaшивaeмыx адресов памяти путем ус тановки коммутирующих элементов 82 в блоке 4 установки адреса в положения соответствующие коду адреса, высвечи ваемому в блоке 7 индикации адреса. По мере сужения области адресов провернется обнаруживаемость ошибок. Ес ли при каком-либо минимальном массиве адресов ошибка перестает выявлять ся, то устанавливают минимальный мас сив адресов, при котором ошибка фик сируется, и далее с помощью осциллографа исследуется причина неисправно работы. Для этого коммутирующий элемент 152 в блоке 22 сравнения чисел отключают, в результате.чего после пуска устройства останова по неисправности не будет. Осциллограф целесообразно синхронизовать от выхода 29 признака опе рации. Конкретное место неисправности определяется с помощью признака неравенства на выходе 30 блока 22 сравнения данных. Для этого .сигнал подают с выхода 30 на вход осцилло85928графа, и запоминают местоположение признака ошибки (импульс отрицательной полярности). Затем исследуют характерные точки блока памяти, наблюдая сигналы в данном участке развертки луча осциллографа. Это позволяет быстро находить, причину неисправности. Синхронизация осциллографа может осуществляться и от любого разряда адреса на выходах 31 устройства, а также от любого выбранного оператором адреса на выходе 28 блока 11 сравнения адресов и циклов. Такая синхронизации необходима, когда не удается локализовать ошибку путем сокращения массива опрашиваемых адpecdrB блока памяти, т.е. ошибка в каком-либо адресе проявляется только при переборе большого количества адресов, а при попытке сузить массив адресов ошибка исчезает. В этом случае оператор набирает на коммутирующих элементах 93 блока 10 выбора адреса синхронизации код адреса, при котором происходит останов при минимально возможном массиве адресок, установленном с помощью блока 4 установки адреса. Затем на коммутирующих . элементах 96-98 в блоке I1 сравнения адресов и циклов набирается код цикла, в котором произошел останов, и в случае свечения элемента индикации, сигнализующего о наличии признака инверсии в блоке 7 индикации адреса, включается коммутирующий элемент 99 в блоке 11. Осциллограф в этом случае синхронизуется сигналом с выхода 28 блока 1 сравнения адресов и циклов. Затем оператор выключает коммутирующий элемент 152 в блоке 22 сравнения чисел и исследует работу блока памяти при прохождении выбранного им адреса. Ориентиром местоположения ; ошибки при этом слуямт сигнал нера- . венства иа выходе 30 блока 22 сравнения чисел. При проверке блока памяти тестом Бегущий 0,1 с выхода 28 блока 11 снимается признак инверсии, который определяет инверсию числа в какомлибо определенном адресе. Этот признак инверсии и может использоваться для синхронизации осциллографа, так как именно адрес, на который воздействуют инверсным кодом, находится в более тяжелых условиях и его требуется исследовать.

По желанию оператора осциллограф можно синхронизировать непосредственно от признака ошибки, т,е. сигналом с выхода 30 блока 22 сравнения данных, это позволяет наб.пюдать характер неисправности при запуске развертки луча в момент появления признака ошибки.

Формула изобретения

Устройство для контроля блоков оперативной памяти, содержащее генератор, первый вход которого соединен с первым выходом блока пуска, а первый выход подключен к первому входу формирователя управляющих сигналов , первый выход которого соединен с входом формирователя сигнала опроса и является первым управляющим выходом устройства, а второй выход подключен к синхровходу счетчика адреса, вход сброса которого соединен с первым выходом, блока сброса, а входы начальной установки и выходы подключены соответственно к выходам блока установки адреса и входам первой группы первого коммутатора, блок сравнения данных, первый вход которого соединен с выходом формирователя сигнала опроса, входы первой группы являются информационными входами устройства, входы второй группы подключены к выходам группы блока инверсии данных, входы третьей группы соединены с выходами блока коммутации и с входами первой группы первого блока индикации, выходы группы подключены к входам второй группы первого блока индикации, а первый вы ход соединен с вторым входом генератора, счетчик циклов и второй блок индикации, отличающееся тем, что, с целью повышения достоверности контроля в устройство введены блок местного управления, второй коммутатор, блок выбора адреса синхронизации,блой сравнения адресов и циклов, блок задания начального кода, генератор псевдослучайного кода, второй блок инверсии данных, третий и четвертый блоки индикации-, причем входы группы блока местного упг равления соединены с выходами счетчика циклов, первый и второй выходьг блока местного управления подключены к первому и второму входам блока сравнения адресов и циклов, третий

и четвертый выходы соединены с первым и входами первого блока инверсии данных, пятый и шестой выходы подключены к второму и третьему

входам блока сравнения данных, первый вход соединен с первым выходом блока сброса и с первым управляющим входом счетчика циклов, а второй вход блока местного управления подключен к второму выходу блока сброса, второму управляющему входу счетчика циклов, к первым входам блока пуска и блока задания начального кода, второй вход которого соединен с входом блока выбора адреса синхронизации и с одним из выходов счетчика циклов, соответствующие выходы которого подключены к первому, второму и третьему управляющим входам второго блока индикации, четвертый управляющий вход которого соединен с третьим входом блока сравнения адресов и циклов и с выходом первого блока инверсии данных, а информационные входы подключены к выходам второго коммутатора, входом первой группы блока сравнения адресов и циклов и являются адреснь1ми выходами устройства, первый вход генератора псевдослучайного кода соединен с вторым выходом формирователя управляющих сигналов, второй вход подключен к третьему выходу блока сброса, третьему входу генератора второму входу формирователя управляющих сигналов и к четвертому входу блока сравнения данных, входы группы генератора псевдослучайного кода соединены с выходами первой группы блока задания начального кода и с входами третьего блока индикации, а выходы подключены к входам первой группы второго коммутатора и группы первого блока инверсии данных, третий вход которого соединен с первым выходом блока сравнения адресов и циклов, второй вход которого подключен к соответствующему выходу счетчика циклов, второй выход является выходом синхронизации устройства, а первый вход и входы группы подключены к первому выходу и к выходам группы блока выбора адреса синхронизации,, второй выход которого соединен с управляющим входом первого коммутатора, а входы группы подключены к выз одам второй группы блока задания- начального кода, третий вход которого .соединен с вторьм выходом генератора.

входы второй группы первого коммутатора соединены с выходами второй группы блока установки адреса,-а выходы подключены к входам второй груп пы второго коммутатора адреса, пятый и шестой входы н второй и третий выходы блока сравнения данных соединены соответственно с первым и вторым выходами и с вторым и третьим входами блока пуска, седьмой вход подключен к седьмому выходу блока управления и к управляюще658593.2

му входу второго блока инверсии данных, входы группы которого соединены с выходами группы первого блока инверсии данных, а выходы подключе5 ны к входам четвертого блока индикации и являются информационными выходами устройства, восьмой выход блока местного управления и четвертый выход блока сравнения данных яв10 ляются соответственно вторым управляющим выходом и выходом признака неисправности устройства.

SS

J5

Sff

тпг

.е

49 .

5

5r

Я7

t5

iia e

iin-l m L.«

V

т

Я

Й-3

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для задания тестов | 1982 |

|

SU1096612A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков оперативной памяти | 1989 |

|

SU1689994A2 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1317486A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для формирования тестов | 1984 |

|

SU1226472A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля магнитных и полупроводниковых блоков оперативной памяти. Целые изобретения является повьшение достоверности контроля. Устройство содержит генератор, формирователь управляющих сигналов, счетчик адреса, блок установки адреса, первый и второй, коммутаторы, первый, второй, третий и четвертый блоки индикации, блок сброса, счетчик циклов, блок выбора адреса синхронизации, блок сравнения адресов и циклов, блок формирования признака операции, блок управления режимами, блок формирования признака режима, блок задания начального кода, генератор псевдослучайного кода, первый и второй блоки инверсии данных, формирова-тель признака инверсии данных, блок сравнения данных, формирователь сигнала опроса, блок пуска, блок коммутации. Б устройстве обеспечиваются следующие режимы контроля: однократная запись с остановом, тяжелая запись с многократной инверсной предысторией контроль с чередованием циклов записи и считывания; формирование тестовой программы; формирование начального кода путем сдвига исходного кода; формирование начального ко.1 fS; да по принципу 1 к исходному коду; Ш ||ет формирование упорядоченных кодов .;гяга реса; формирование кодов адреса, изменяк)щихся по псевдослучайному закону; формирование теста Бегущий 0,1 в прямом и обратном порядке перебора адресов; формирование проверочного Ю кода с инверсией по адресам, циклам а и признаку операции; формирование инверсных кодов по любому выбранному ел адресу; формирование инверсных кодов 00 Ol с псевдослучайным распределением информации, а также диагностические режимы. 18 ил.

Пеоен. ciaut. пост.

1

W 59 47

чг 42

I I I I

ш и I I

73

| Измерение параметров цифровых интегральных микросхем ./Под ред | |||

| Д.Ю | |||

| Эйдукаса и Б.В | |||

| Орлова | |||

| М.: | |||

| Радио и связь, 1982, с | |||

| Металлические подъемные леса | 1921 |

|

SU242A1 |

| Разработка полупроводниковых оперативных запоминающих устройств и пульта для их контроля и наладки | |||

| Отчет МЭИ, Инв | |||

| Способ обработки боковых поверхностей шпал различного радиуса кривизны | 1947 |

|

SU87254A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-10-23—Публикация

1984-05-30—Подача