.коммутатор 20, триггер 21, триггер 22, ждущий мультивибратор 23 и ключ 24. Повьшение достоверности контроля достигается введением оперативного накопителя 7, блока 19 сравнеИзобретение относится к автоматике и вычислительной технике и может . быть использовано для контроля блоков памяти.

Цель изобретения - повышение достоверности контроля блоков памяти.

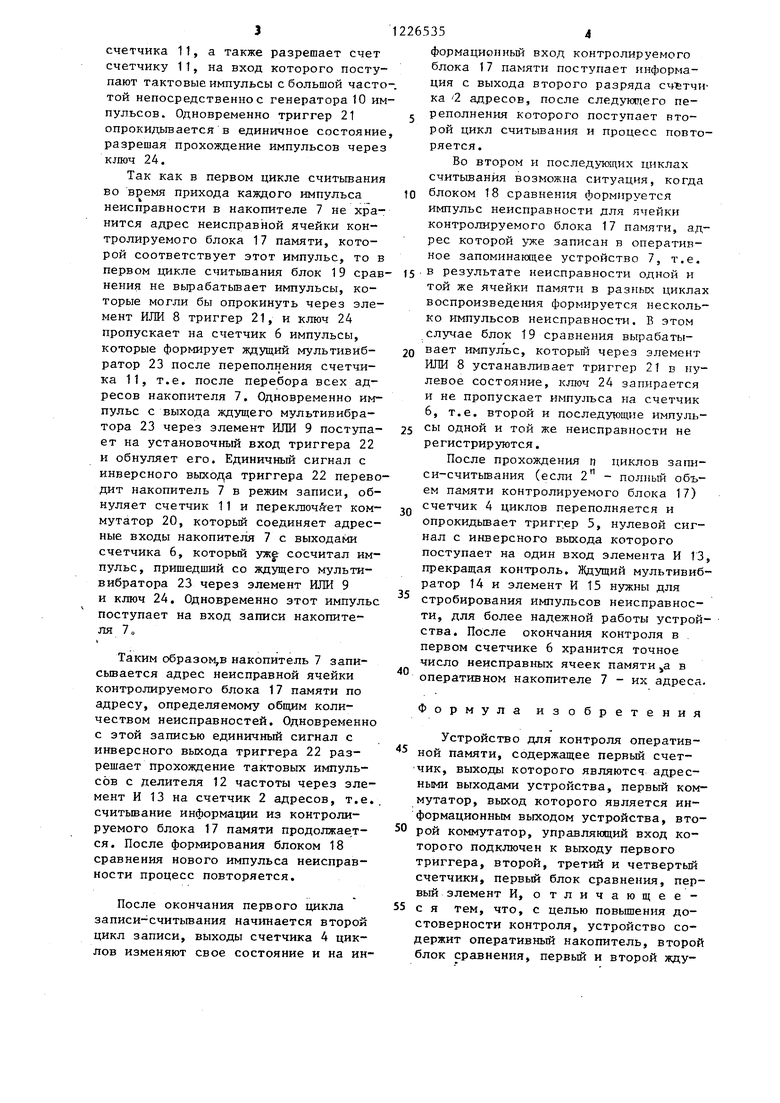

На чертеже представлена блок-схема устройства для контроля блоков памяти,

Устройство содержит блок 1 начальной установки, счетчик 2 адресов, триггер 3, С-четчик 4 импульсов циклов, триггер 5, счетчик 6 импульсов, оперативный накопитель 7, элементы ИЛИ 8 и 9, генератор 10 импульсов, счетчик 11, делитель 12 частоты, элемент И 13, ждутдий .мультивибратор 14, элемент И 15, коммутатор 16, контролируемый блок 17 памяти, блок 18 сравнения, блок 19 сравнения, коммутатор 20, триггер 21, триггер 22, ждущий мультивибратор 23 и ключ 24.

Устройство работает следующим образом. I

В исходном состоянии сигналом

Лог.1, поступающим из блока 1 начальной установки, обнулены счетчики адресов 2 и циклов 4, триггеры 3 и 5, оперативньй накопитель 7. Этим же сигналом, проходящим через элементы ИЛИ 8 и 9 обнулены соответственно триггеры 21 и 22. Единичными сигналами, поступающими с инверсных выходов триггеров 5 к 22 на один и другой входы элемента И 13 разрешается прохождение тактовых импульсов с генератора 10 импульсов через делитель 12 частоты на вход счетчика 2 адресов. Контролируемый блок 17 памяти нулевым сигналом с выхода триггера 3 включен в режим записи. Адресные входы оперативного накопителя 7, которьй единичным сигналом с инверсного выхода триггера 22 включен в режим записи, подключены через коммутатор 20 к выходам счетчика 6, После прихода сигнала начала контроля из блока 1 (Лог.О) счетчик 2 адресов начинает формировать адреса для записи инфор5 мации в контролируемый блок 17 памя- - ти. В первый цикл записи .в контролн- руемьй блок 17 памяти записывается информация,.поступающая через коммутатор 16 с выхода первого разряда

10 счетчика 2 адресов. После записи ин- ;формации в полный объем контролируемого блока 17 памяти счетчик 2 адресов переполняется и опрокидьшает триггер 3, единичный сигнал с выхода

15 которого переводит контролируемый блок 17 памяти в режим воспроизведения. Так как во время цикла записи- считывания счетчик 4 циклон- не изменяет своего состояния, то сигнал,

20 поступающий с коммутатора 16 на один вход первого блока 18 сравнения во :время цикла считьгоания, идентичен сигналу, который был записан в кон- тролируемьй блок 17 памяти во время

25 цикла записи. Таким образом, информация, которая была записана в контролируемый блок 17 памяти,сравнивается с воспроизведенной из него блоком 18 сравнения , который в случае несовпа30 дения выдает импульс неисправности

Предположим, что произошло несовпадение и импульс неисправности через элемент И 15 поступает на входы триггеров 21 и 22. Нулевой сигнал с

35 инверсного выхода триггера 22 не по- зво.пяет тактовым импульсам поступать с выхода элемента И 13 на вход счетчика 2 адресов, на выходах которого теперь хранится адрес неисправной

40 ячейки памяти. Этот же нулевой сигнал с инверсного выхода триггера 22 переводит оперативный накопитель 7 в реж1-1м воспроизведения, перек.пючает коммутатор 20, так что адресные вхо45 Ды накопителя 7 подключены к выходам

ния, мультивибраторов 14 и 23, триггеров 5j, 21 и 22, элементов ИЛИ 8 и 9, эле мента И-15, ключа 24 и делителя 12 частоты, а также введением новых функциональных связей. 1 ил..

J

счетчика 11, a также разрешает счет счетчику 11, на вход которого поступают тактовые импульсы с большой частотой непосредственное генератора 10 импульсов. Одновременно триггер 21 опрокидывается в единичное состояние разрешая прохождение импульсов через ключ 24.

Так как в первом цикле считывания во время прихода каждого импульса неисправности в накопителе 7 не хранится адрес неисправной ячейки контролируемого блока 17 памяти, которой соответствует этот импульс, то в первом цикле считьшания блок 19 сравнения не вырабатьюает импульсы, которые могли бы опрокинуть через элемент ИЛИ 8 триггер 21, и ключ 24 пропускает на счетчик 6 импульсы, которые формирует ждущий мультивибратор 23 после переполнения счетчика 11, т.е. после перебора всех адресов накопителя 7. Одновременно импульс с выхода ждущего мультивибратора 23 через элемент ИЛИ 9 поступает на установочный вход триггера 22 и обнуляет его. Единичный сигнал с инверсного выхода триггера 22 переводит накопитель 7 в режим записи, обнуляет счетчик 11 и переключает коммутатор 20, которьй соединяет адресные входы накопителя 7 с выходами счетчика 6, который уж сосчитал импульс, пришедший со ждущего мультивибратора 23 через элемент ИЛИ 9 и ключ 24. Одновременно этот импульс поступает на вход записи накопителя 7„

Таким образом,в накопитель 7 запи- сьгоается адрес неисправной ячейки контролируемого блока 17 памяти по адресу, определяемому общим количеством неисправностей. Одновременно с этой записью единичный сигнал с инверсного выхода триггера 22 разрешает прохождение тактовых импульсов с делителя 12 частоты через элемент И 13 на счетчик 2 адресов, т.е. считьшание информации из контролируемого блока 17 памяти продолжае т- ся. После формирования блоком 18 сравнения нового импульса неисправности процесс повторяется.

После окончания первого цикла записи-считьгеания нач1шается второй цикл записи, выходы счетчика 4 циклов изменяют свое состояние и на ин265354

формационный вход контролируемого блока 17 памяти поступает информация с выхода второго разряда сч Етчи- ка 2 адресов, после следуюо1его пе- с реполнения которого поступает второй цикл считывания и процесс повторяется.

Во втором и последующих циклах считьшания возможна ситуация, когда

10 блоком 18 сравнения формируется импульс неисправности для ячейки контролируемого блока 17 памяти, адрес которой уже записан в оперативное запоминающее устройство 7, т.е.

5 в результате неисправности одной и той же ячейки памяти в разных циклах воспроизведения формируется несколько импульсов неисправности. В этом случае блок 19 сравнения вырабаты2Q вает импульс, которьй через элемент ИЛИ 8 устанавливает триггер 21 в нулевое состояние, ключ 24 запирается и не пропускает импyJп ca на счетчик 6, т.е. второй и последутощие импуль25 сы одной и той же неисправности не регистрируются.

После прохождения п циклов запи- си-считьшания (если 2 - полный объем памяти контролируемого блока 17) счетчик 4 циклов переполняется и опрокидывает триггер 5, нулевой сигнал с инверсного выхода которого поступает на один вход элемента И 13, прекращая контроль. Ждущий мультивибратор 14 и элемент И 15 нзшны для

стробирования импульсов неисправности, для более надежной работы устройства. После окончания контроля в первом счетчике 6 хранится точное число неисправных ячеек памяти а в оперативном накопителе 7 - их адреса.

Формула изобретения

Устройство для контроля оператив- ной памяти, содержащее первьй счет- чик, выходы которого являются адресными выходами устройства, первый коммутатор, выход которого является информационным выходом устройства, вто- 0 рой коммутатор, управляющий вход которого подключен к выходу первого триггера, второй, третий и четвертьй счетчики, первьй блок сравнения, первьй элемент И, отличающее- 5 с я тем, что, с целью повьшзения достоверности контроля, устройство содержит оперативньй накопитель, второй блок сравнения, первьй и второй жду30

512

ие мультивибраторы, второй, третий четвертый триггеры, первый и втоой элементы ИЛИ, второй элемент И, ключ и делитель частоты,, вход которого является тактовым входом устройства и подключен к первому входу четвертого счетчика, выход дели:теля час- тоты подключен к первому входу первого элемен 1;а И, второй вход которого подключен к первому управлякяцему вхо ду оперативного накопителя, к второму входу четвертого счетчика импульсов и к выходу первого триггера, выход первого элемента И подключен к входу первого ждущего мультивибратора и к входу первого счетчика, один из выходов которого подключен к входу второго триггера, выход второго триггера подключен к входу второго счетчика, выходы которого подключены к управляюпдам входам второго коммута- тора, третий.вход, первого элемента И подключен к выходу третьего триггера вход которого подключен к одному из выходов второго счетчика, информационные входы первого коммутатора подключены к соответствующим входам оперативного накопителя, к входам первой группы второго блока сравнения и к выходам первого счетчика, выход первого коммутатора подключен к первому входу первого блока сравнения и является информационным выходом устройства, второй вход первого блока сравнения является информаРедактор Н.Ядола

Составитель С.Шустенко Техред И. Попович

Заказ 2140/52 Тираж 543

ВНИИПИ. Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раугаская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

65356

ционным входом устройства, выход первого блока сравнения подключен к первому входу второго элемента И, второй вход которого подключен к выJ ходу второго триггера и является уп- равляю;щим выходом устройства, выход первого мультивибратора под- клочеи к третьему входу второго элемента И, выход которого подключен к

0 первоку входу первого триггера и к первому входу четвертого триггера, выход четвертого триггера подключен к управляющему входу ключа, выход которого подключен к входу третьего

5 с гетчика и к второму управляющему

входу оперативного накопителя, адресные входы которого подключены к выходам второго коммутатора, выходы третьего счетчика подключены к вхо0 дам первой группы первого коммутато- рг, входы второй группы которого под- кгдочены к выходам четвертого счетчика, второй вход четвертого триггера подключен ,к выходу первого элемента

5 ИЛИ, вход которого подключен к выхо- ду второго блока сравнения, входы второй группы которого подключены к выходам оперативного накопителя, второй вход первого триггера подклю0 чек к выходу второго элемента ИЛИ, вход которого подключен к.выходу вто- .рого ведущего мультивибратора, вход которого подключен к одному из выходов четвертого счетчика, вход ключа подключен к выходу второго элемента ИЛИ.

Корректор СоШекмар Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1425753A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1383449A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля аппарата магнитной записи | 1984 |

|

SU1247942A2 |

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля блоков оперативной памяти. Цель изобретения - повьшение достоверности контроля блоков памяти. Устройство содержит блок 1 начальной установки, счетчик 2 адресов, триггер 3, счетчик 4 импульсов циклов, триггер 5, счетчик 6 импульсов, оперативньй накопитель 7, элементы ИЛИ 8 и 9, генератор 10 импульсов, счетчик 11, делитель 12 частоты, элемент И 13, ждущий мультивибратор 14, элемент И 15, коммутатор 16, контролируемый блок 17 памяти, блок 18 сравнения, блок, 19 сравнения, СЛ

| Устройство для контроля блоков памяти | 1980 |

|

SU862239A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001181A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-08—Подача