Изобретение относится к вычислительной технике, в частности к устройствам обмена информацией между магистралью ЭВМ типа M-BUS и группой интеллектуальных периферийных устройств, работающих в стандарте интерфейса SCSI

Известно устройство для обмена информацией, содержащее два блока сопряжения, дешифратор адреса, мультиплексор данных, регистр адреса вектора, выходной буферный регистр, два дешифратора управляющих сигналов, регистр состояний, входной буферный регистр, регистр прерываний, дешифратор направления ввода и регистр команды ввода Недостатком этого

устройства является узкая область применения.

Известно устройство для сопряжения источников и приемгИков с магистралью, содержащее регистр данных источников, регистр прерываний регистр данных приемника, регистр адреса, блок связи с магистралью, дешифратор адреса, мультиплексор, блок дешифрации управляющих сигналов, две группы элементов И и элемент ИЛИ, а блок дешифрации управляющих сигналов содержит и-есть триггеров, дешифратор сигналов приема байта, дешифратор сигналов состояния, дешифратор сигналов сброса регистра прерывания, дешифратор сигналов

44 СЛ

NJ

Я

передачи байтов, формирователь импульса включения питания, элемент ИЛИ, элемент задержки, четыре элемента И, элемент ИЛИ-НЕ и инвертор. Недостатком этого устройства является узкая область применения.

Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство для сопряжения магистрали ЭВМ с внешними устройствами, содержащее два блока приемопередатчиков (шинных формирователей), блок приемников (шинный формирователь), блок прерываний, первый и второй блоки дешифрации адреса, блок передатчиков (шинный формирователь), два блока формирования сигналов, два коммутатора, счетчик адреса, блок памяти, шифратор, три элемента И-ИЛИ, шесть элементов И, первый блок формирования сигналов содержит элемент НЕ (инвертор), регистр, три элемента И и пять элементов развязки, второй блок формирования сигналов содержит три эле- .мента НЕ (три инвертора), три элемента И, триггер и элемент развязки, причем первая группа информационных входов первого блока дешифрации адреса и группа строби- рующих входов соединены соответственно с первой и второй группами выходов блока приемников, группа входов которого является группой входов устройства для подключения к группе шин идентификации режима магистрали ЭВМ и первой группе информационных шин магистрали ЭВМ, первый и второй выходы блока приемников соединены соответственно с установочным входом и входом разрешения блока прерывания, группа выходов которого является группой выходов устройства для подключения к шинам прерывания и синхронизации магистрали ЭВМ, группа входов-выходов первого блока приемопередатчиков является группой входов-выходов устройства для подключения к второй группе информационных шин магистрали ЭВМ, группа выходов первого блока приемопередатчиков соединена с второй группой информационных входов первого блока дешифрации адреса и с группой информационных входов второго блока приемопередатчиков, группа входов-выходов которого является группой входов-выходов устройства для подключения к группе информационных шин внешних устройств, вход разрешения блока прерывания соединен с выходом соответствующего разряда группы выходов первого блока приемопередатчиков, разрядные выходы счетчика адреса соединены с первыми группами информационных входов первого и второго

коммутаторов, группа выхода первого блока дешифрации адреса соединена с второй группой информационных входов первого коммутатора, выходы которого соединены с

информационными входами второго блока дешифрации адреса, блока передатчиков и адресными входами блока памяти, выходы блока передатчиков являются выходами устройства для подключения к адресным ши0 нам внешних устройств, группа выходов второго блока приемопередатчиков соединена с второй группой информационных входов второй группы информационных входов второго коммутатора, третья группа

5 информационных входов которого соединена с группой выходов шифратора, гер- вый и второй стробирующие входы которого соединены соответственно с первым и вторым выходами первого блока де0 шифрации адреса, первый выход блока прерывания соединен с третьим стробирую- щим входом шифратора и с первым входом первого элемента И, выход которого соединен с разрешающим входом первого блока

5 приемопередатчиков, выход второго блока дешифрации адреса соединен с первыми входами первого и второго элементов И- ИЛИ и с четвертым стробирующим входом шифратора, первый выход которого соеди0 нен с первым входом второго элемента Й- ИЛИ, и с вторым входом первого элемента И-ИЛИ, второй выход шифратора соединен с первым входом второго элемента И, выход которого соединен с входом разрешения

5 блока прерывания, второй выход которого соединен с третьим входом первого элемента И-ИЛИ, выход первого элемента И-ИЛИ соединен с управляющим входом второго коммутатора, выход второго элемента И0 ИЛИ соединен с входом разрешения второго коммутатора, тактовые входы первого и второго блоков формирования сигналов являются входом устройства для подсоединения к тактовой шине магистрали ЭВМ,

5 первый выход блока приемников соединен с установленными входами первого и второго блоков формирования сигналов, третий выход блока приемников соединен с первым входом третьего элемента И-ИЛИ, пер0 вым входом третьего элемента И и с первым информационным входом первого блока формирования сигналов, первый и второй выходы которого являются выходами устройства для подключения соответственно к

5 шинам записи и считывания внешних устройств, третий выход первого блока формирования сигналов соединен с входом режима блока прерывания, вход готовности которого соединен с третьим входом второго элемента И-ИЛИ и с первым выходом

второго блока формирования сигналов, второй выход которого соединен с четвертым входом второго элемента И-ИЛИ. четвертый и пятый выходы первого блока формирования сигналов соединены соответственно с первым входом четвертого элемента И и с первым режимным входом второго блока формирования сигналов, второй режимный вход которого является входом устройства для подключения к шине готовности внешних устройств, четвертый выход блока приемников соединен с вторым информационным входом первого блока формирования сигналов, первыми входами пятого и шестого элементов И, вторым входом второго элемента И и вторым входом тоетьего элемента И-ИЛИ, выход которого соединен с третьим информационным входом первого блока формирования сигналов, третьим режимным входом второго блока формирования сигналов и вторым входом четвертого элемента И, выход которого соединен с управляющим входом первого коммутатора, шестой выход первого блока формирования сигналов соединен с третьим входом второго элемента И, и вторым входом шестого элемента И, выход которого соединен с входом записи блока памяти, информационный вход которого соединен с выходом соответствующего разряда группы выходов первого блока приемопередатчиков, первый и второй выходы блока памяти соединены с четвертым входом первого элемента И-ИЛИ и с четвертым режимным входом второго блока формирования сигналов, третий выход которого соединен со счетным входом счетчика адреса, группа выходов второго коммутатора соединена с группой информационных входов первого блока приемопередатчиков, выход третьего элемента И соединен с вторым входом первого элемента И, третий выход первого блока дешифрации адреса соединен с третьим и четвертым входами третьего элемента И-ИЛИ, вторыми входами третьего и пятого элементов И, выход пятого элемента И соединен с управляющим входом второго блока приемопередатчиков, тактовый и третий информационный входы блока формирования сигналов соединены соответственно с первым синхровхо- дом и первым управляющим входом регистра, установочный вход блока формирования сигналов соединен с вторым синх- ровходом и вторым управляющим входом регистра, первый и второй информационные входы блока соединены соответственно с первым входами первого и второго элементов И, информационные входы регистра блока объединены и подсоединены к первому выводу первого элемента развязки, второй вывод которого подсоединен к нулевой шине, йыход первого элемента И подсоединен к первым выводам второго и третьего

элементов развязки и является первым выходом блока формирования сигналов, выход второго элемента И подсоединен к первым выводам четвертого и пятого элементов развязки и является вторым выходом блока,

0 вторые выводы второго и четвертого элементов развязки подсоединены к нулевой шине, а вторые выводы третьего и пятого элементов развязки подсоединены к положительной шине источника питания, пер5 вый выход регистра соединен с входом элемента НЕ и является четвертым выходом блока, второй выход регистра является пятым выходом блока, третий выход регистра соединен с первым входом третьего эле0 мента И и является третьим выходом блока выход элемента НЕ соединен с вторым входом первого элемента И и вторым входом третьего элемента И, выход которого соединен с вторым входом второго элемента И и

5 является шестым выходом устройства, тактовый вход блока соединен с входом первого элемента НЕ, и первым входом первого элемента И, выход которого соединен с входом второго элемента НЕ, выход которого

0 соединен с синхровходом триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого является вторым выходом блока, установочный вход которого соединен с прямым входом

5 триггера, информационный вход которого соединен с выходом третьего элемента И, первый вход которого является четвертым режимным входом блока, инверсный выход триггера является третьим выходом блока,

0 третий режимный вход которого подсоединен к второму входу первого элемента И, третий вход которого гзляется первым режимным входом блока, выход первого элемента НЕ соединен с вторым входом

5 второго элемента И, второй режимный вход блока подсоединен к первому выводу развязки и к входу третьего элемента НЕ, выход которого соединен с вторым входом третьего элемента И и является первым выходом

0 блока, второй выход элемента развязки подсоединен к положительной шине источника питания.

Недостатком этого устройства является узкая область применения - оно не может

5 обеспечить подключение к системной магистрали ЭВМ наиболее перспективных а настоящее время периферийных устройств, работающих в стандарте интерфейса SCSI, так как не может преобразовывать сигналы управления и идентификации интерфейса

SCSI в соответствующие сигналы интерфейса M-BUS и наоборот и, следовательно, системный модуль не может управлять данным типом ПФУ, а ПФУ не могут еести обмен данными с системным модулем,

Целью изобретения является расширение области применения путем обеспечения работы периферийных устройств в стандарте интерфейса SCSI.

Поставленная цель достигается тем, что в устройство для сопряжения магистрали ЭВМ с периферийными устройствами, включающее первый, второй и третий шинные формирователи, первый регистр, первый триггер, два дешифратора, счетчик, элемент И-ИЛИ, шесть элементов И, два инвертора, причем, первая входная-выходная информационная шина устройства под- ключена к первым информационным входам-выходам первого шинного формирователя, вторые информационные входы-выходы которого подключены к информационным выходам второго шинного формирователя, информационные входы второго шинного формирователя подключены к второй входной-выходной информационной шине устройства, информационные выходы первого дешифратора подключены к входам третьего шинного формирователя первый выход первого регистра соединен с первым входом первого элемента И, дополнительно введены второй и третий регистры, второй-шестой триггеры, седьмой- пятнадцатый элементы И, четыре элемента И-НЕ, восемь элементов ИЛЙ-НЕ, семь элементов ИЛИ и шесть элементов задержки, причем вторые информационные входы- выходы первого шинного формирователя подключены к информационным входам первого, второго, третьего регистров, к информационным выходам третьего шинного формирователя и к входам первого элемента ИЛЙ-НЕ, выход которого подсоединен к информационному входу второго триггера, выход которого подключен к первым входам вторых элементов И и ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ является выходом общего сброса устройства, второй вход второго элемента ИЛИ-НЕ подключен к входу общего сброса устройства, а второй вход второго элемента И подключен к входусин- хроггоследовательности CLK устройства, выход второго элемента И подключен к своему входу сброса и к входу сброса второго триггера, входная адресная шина подключена к информационным входам второго дешифратора, к входам третьих элементов И и ИЛИ-НЕ, выходы которых подключены соответственно к первому и второму входам четвертого элемента И, выход четвертого

элемента И подключен к управляющему входу второго дешифратора, первый выход которого к первым входам пятого и шестого элементов И, второй выход второго дешифратора подсоединен к первым входам седьмого элемента И и второго элемента И-НЕ, третий выход второго дешифратора подключен к первому входу восьмого элемента И, четвертый выход второго дешифратора под0 ключей к первому входу девятого элемента И, выходы пятого-девятого элементов И, второго элемента И-НЕ подключены к первым шести входам четвертого элемента ИЛИ-НЕ, выход которого подключен к пер5 вому управляющему входу первого шинного формирователя, второй управляющий вход которого подключен к входу сигнала вывода устройства, вход запрета обращения к портам ввода-вывода устройства подключен к

0 первым входам пятого и шестого элементов ИЛИ-НЕ, вторые входы которых подключены соответственно к входам сигнала вывода и сигнала ввода устройства, выход пятого элемента ИЛИ-НЕ подключен к вто5 рым входам шестого элемента И и второго элемента И-НЕ, выход шестого элемента ИЛИ-НЕ подключен к вторым входам пятого, седьмого, восьмого и девятого элементов И, выход седьмого элемента И через первый

0 элемент задержи подключен к синхровходу второго триггера, выход девятого элемента И через второй элемент задержки подключен к синхровходу первого регистра, выход восьмого элемента И через третий элемент

5 задержки подключен куправляющему входу записи второго регистра, к синхровходу третьего триггера и к первому входу первого элемента ИЛИ, выход пятого элемента И через четвертый элемент задержки подклю0 чен к первому входу второго элемента ИЛИ, выход которого подсоединен к управляющему входу записи третьего регистра, к синх- роеходу четвертого триггера, к первым входам третьего и четвертого элементов

5 ИЛИ, выход четвертого триггера подключен к второму входу четвертого элемента ИЛИ, выход которого подсоединен к управляющему входу считывания третьего регистра, информационные выходы второго и третьего

0 регистров подключены к второй входной- выходной информационной шине устройства, первый выход первого регистра подключен к пербым входам обоих элементов И элемента И-ИЛИ, выход которого под5 ключей к первому входу первого элемента И-НЕ, выход которого подключен к синхровходу первого триггера, второй инверсный выход первого регистра подключен к первому входу седьмого элемента ИЛИ-НЕ, второй вход которого подключен к управляющему входу устройства подтверждения захвата системной шины каналом контроллера ДМА, а выход подключен к седьмому входу четвертого элемента ИЛИ-НЕ, к первому входу третьего элемента И-НЕ и к прямым входам десятого и одиннадцатого элементов И. инверсные входы которых подключены соответственно к управляющим входам ввода и вывода устройства, выход десятого элемента И через пятый элемент задержки подключен к второму входу второго элемента ИЛИ, выход одиннадцатого элемента И подключен к первому входу пятого элемента ИЛИ, выход которого подсоединен к второму входу третьего элемента ИЛИ и к первому управляющему входу второго шинного формирователя, второй вход пятого элемента ИЛИ подключен к второму входу четвертого элемента ИЛИ-НЕ, выход третьего элемента ИЛИ подключен к инверсному входу двенадцатого элемента И и к синхровходу пятого триггера, инверсный выход которого является выходом подтверждения устройства, выход двенадцатого элемента И подключен к инверсному входу сброса шестого триггера, третий выход первого регистра подключен к первому входу тринадцатого элемента И, выход которого подключен к первому входу шестого элемента ИЛИ, выход шестого триггера подключен к вторым входам первого и тринадцатого элементов И. выходы первого элемента И и шестого элемента ИЛИ являются соответственно выходами устройства запроса на обслуживание каналом контроллера ДМА и запроса прерывания к контроллеру прерывания системного модуля, выход первого триггера подключен к второму входу шестого элемента ИЛИ вход устройства занятия системной магистрали подключен к первому входу четырнадцатого элемента И, а через первый инвертор подключен к первому входу восьмого элемента ИЛИ-НЕ, к второму входу первого элемента И-НЕ и к шестому информационному входу третьего шинного формирователя, выход восьмого элемента ИЛИ-НЕ подключен к пятому информационному входу третьего шинного формирователя, второй вход третьего элемента И-НЕ подсоединен к входу устройства конца передачи данных в режиме ПДП, а выход - к третьему входу первого элемента И-НЕ, выход второго элемента подключен к первому управляющему входу третьего шинного формирователя и к первому входу пятнадцатого элемента И. выход которого подключен к инверсному входу сброса первого триггера, выход третьего триггера подключен к второму входу первого элемента ИЛИ к первому входу и через

шестой элемент задержки к второму входу четвертого элемента И-НЕ, выход которого является выходом выбора ПФУ устройства, выход первого элемента ИЛИ подключен

к входу разрешения чтения второго регистра, выход третьего триггера подключен к второму входу восьмого элемента И, вход запроса устройства подключен к прямому входу седьмого элемента ИЛИ, а через вто0 рой инвертор к синхровходу шестого триггера и седьмому информационному входу третьего шинного формирователя, выход второго элемента ИЛИ-НЕ подключен к инверсному входу сброса первого регистра, к

5 инверсному входу седьмого элемента ИЛИ, к прямому входу двенадцатого элемента И, к вторым входам четырнадцатого и пятнадцатого элементов И, выходы четырнадцатого элемента И и седьмого элемента ИЛИ

0 подключены к входам сброса соответственно третьего, четвертого и пятого триггеров, три входа устройства индентификации состояния активного периферийного устройства подключены соответственно к

5 первому, второму и третьему входам первого дешифратора, первый и второй выходы которого подключены соответственно к вторым входам первого и второго элементов И элемента И-ИЛИ, вторые управляющие вхо0 ды второго и третьего шинных формирователей подключены к шине логического нуля, информационные входы первого, третьего- шестого триггера подключены к шине логической единицы.

5 Введение новых связей третьего шинного формирователя обеспечивает формирование и передачу в информационную шину системной магистрали байта состояния устройства, описывающего режим и фа0 зу работы устройства, по команде главного процессора Читать байт состояния.

Введение новых связей первого регистра обеспечивает возможность программно устанавливать режим обмена данными

5 между ПФУ и системным модулем: режим обмена с использованием прерываний главного процессора, режим обмена с использованием канала прямого доступа к памяти.

0 Введение второго регистра и его связей обеспечивает программную запись в устройство и передачу ч групповой контроллер ПФУ номера активного ПФУ.

Введение третьего регистра и его свя5 зей обеспечивает буферизацию в устройстве данных, подлежащих передаче от системного модуля к ПФУ.

Введение новых связей первого триггера обеспечивает формирование сигнала запроса программного прерывания к сиетемному модулю по завершению выполнения его команды ввода-вывода.

Введение второго триггера и его связей обеспечивает программное формирование сигнала общего сброса устройства сопряже- ния и подключенных к нему ПФУ в стандарте интерфейса SCSI.

Введение третьего триггера и его связей обеспечивает формирование управляющего сигнала выбора активного ПФУ в стандарте интерфейса SCSI.

Введение четвертого триггера и его связей обеспечивает удержание информационных выходов третьего регистра открытыми для считывания до завершения приема за- писанной в нем информации периферийным устройством.

Вв еДе ие пятого триггера и его связей обеспечивает формирование сигнала интерфейса SCSI подтверждения того, что при передаче данных от системного модуля к ПФУ Очередной байт данных выставлен на выход системной магистрали.

Введение шестого триггера и его связей обеспечивает формирование запроса к сие- темному модулю на обслуживание ПФУ для обмена очередным байтом данных.

Введение новых связей первого дешифратора обеспечивает формирование из оповещающих сигналов ПФУ, работаю- щего в стандарте SCSI значений пяти разрядов байта состояния устройства о режиме и фазе совместной работы устройства и ПФУ.

Введение новых связей второго де- шифратора обеспечивает дешифрацию младших разрядов адресного кода, поступающего по адресной шине системной магистрали, для организации доступа к портам ввода-вывода, входящих в состав данного устройства.

Введение новых связей счетчика обеспечивает формирование временного интервала действия сигнала программного сброса устройства и ПФУ в стандарте ин- терфейса SCSI,

Введение новых связей элемента ДОИЛИ обеспечивает формирование сигналов о том, что устройство занято обслуживанием ЛФУ в режиме прямого доступа к памяти при вЁОде или выводе информации.

Введение новых связей первого элемента И обеспечивает формирование на входе линии системной магистрали сигнала запроса на передачу байта данных в режиме прямого доступа к памяти,

Введение новых связей второго элемента И обеспечивает работу счетчика по формированию временного интервала действия сигнала программного общего сброса

в том случае, если фаза сброса программно задана.

Введение новых связей третьего и четвертого элементов И и их связей обеспечивает дешифрацию старших разрядов адресов портов ввода-вывода, входящих в устройство.

Введение пятого элемента И и его связей обеспечивает формирование сигнала обращения к порту ввода-вывода данных в режиме записи,

Введение шестого элемента И и его связей обеспечивает формирование сигнала обращения к порту ввода-вывода данных в режиме считывания.

Введение седьмого элемента И и эго связей обеспечивает формирование сигнала обращения к порту программного сброса в режиме записи.

Введение восьмого элемента И и его связей обеспечивает формирование сигнала обращения к порту ввода-вывода кода номера активного ПФУ в режиме записи.

Введение девятого элемента И и его связей обеспечивает формирование сигнала обращения к порту ввода-вывода маски режима обмена данными в режиме записи.

Введение девятого и одиннадцатого элементов И и их связей обеспечивает передачу в устройство управляющих сигналов системной магистрали ввода или вывода информации в режиме прямого доступа к памяти

Введение двенадцатого элемента И и его связей обеспечивает снятие сигнала запроса на обслуживание ПФУ по обмену очередным байтом данных либо в случае его удовлетворения, либо в случае общего сброса,

Введение тринадцатого элемента И и его связей обеспечивает передачу на вход линии системной магистрали сигнала запроса на передачу байта данных в режиме обмена с использованием прерываний главного процессора.

Введение четырнадцатого элемента и его связей обеспечивает формирование сигнала сброса третьего триггера либо при общем сбросе, либо по завершении выбора активного ПФУ, о чем свидетельствует сигнал занятости шины данных

Введение пятнадцатого элемента И и его связей обеспечивает формирование сигнала сброса первого триггера либо при общем сбросе, либо при считывании из устройства байта его состояния после полного завершения операции ввода-вывода данных.

Введение новых связей первого элемента И-НЕ обеспечивает формирование

сигнала установки первого триггера запроса программного прерывания по завершении выполнения команды ввода-вывода в трех случаях; во-первых, при извещении от ПФУ о завершении ввода или вывода информации в режиме ПДП, во-вторых, при поступлении от контроллера прямого доступа к памяти системного модуля сигнала о передаче последнего байта данных в режиме ПДП, в-третьих, при извещении от ПФУ о своем переходе в режим свободной шины, а также передачи синхросигнала на С-вход седьмого триггера

Введение второго элемента И-НЕ и его связей обеспечивает формирование сигнала обращения к порту байта состояния устройства я режиме чтения из устройства и формирование сигнала R321 STATUS.

Введение третьего элемента И-НЕ и его связей обеспечивает дешифрацию старших нулевых разрядов адресов портов ввода- вывода, принадлежащих устройству и передачу данных в режиме ПФП с входной линии 68.

Введение четвертого элемента И-НЕ и его связей обеспечивает формирование задержанного инверсного управляющего сигнала выбора активного ПФУ и выбор контроллера, номер которого от 0 до 7 указывается унитарным кодом на выходе шины данных

Введение первого элемента ИЛИ-НЕ и его связей обеспечивает формирование на информационном входе второго триггера единичного сигнала в том случае, если на первой информационной входной-выходной шине устройства установлен нулевой код. что разрешает программный сброс устройства и ПФУ

Введение второго элемента ИЛИ-НЕ и его связей позволяет передавать на выход общего сброса устройства и инвентировать входной сигнал сброса и выработанный устройством сигнал программного сброса.

Введение пятого и шестого элементов ИЛИ-НЕ и их связей обеспечивает инвертирование и передачу в устройство входных сигналов записи или чтения только в том случае, если на входе устройства нет сигнала системной магистрали об адресном контроллере ПДП оперативной памяти ЭВМ.

Введение седьмого элемента ИЛИ-НЕ и его связей обеспечивает инверсную передачу в устройство сигнала захвата устройством одной из линий контроллера ПДП только в том случае, если режим прямого доступа установлен в устройстве маской режима.

Введение восьмого элемента ИЛИ-НЕ и его связей обеспечивает формирование

четвертого разряда байта состояния устройства о режиме свободной шины в том случае, когда ПФУ сняло сигнал занятости информационной шины и в устройстве не

производится выбор активного ПФУ.

Введение первого элемента ИЛИ и его связей обеспечивает поддержание информационных выходов второго регистра в режиме чтения информации сначала при

0 поступлении сигнала обращения к порту номера активного ПФУ, а затем при наличии на выходе устройства сигнала выбора активного ПФУ.

Введение второго элемента ИЛИ и его

5 связей обеспечивает формирование обобщенного сигнала записи данных в ПФУ как в режиме ПДП, так и в режиме прерываний

Введение третьего элемента ИЛИ и его

0 связей обеспечивает формирование обобщенного сигнала обмена данными между системным модулем и ПФУ как в режиме ПДП, так и в режиме прерываний главного процессора

5 Введение четвертого элемента ИЛИ и его связей обеспечивает поддержание информационных выходов третьего регистра в режиме чтения информации сначала при поступлении сигнала обращения к порту дан0 ных при записи информации в ПФУ, а затем до завершения приема байта данных ПФУ, после чего ПФУ снимает сигнал запроса со входа устройства

Введение пятого элемента ИЛИ и его

5 связей обеспечивает формирование обобщенного сигнала чтения данных из ПФУ как в режиме ПДП, так и в режиме прерывания главного процессора.

Введение шестого элемента ИЛИ и его

0 связей обеспечивает передачу на линию запроса прерывания главного процессора сигналов запросов прерывания как при обмене очередным байтом данных в режиме прерывания процессора, тёк и при завершении

5 выполнения команды ввода-вывода.

Введение седьмого элемента ИЛИ и его связей обеспечивает сброс четвертого и пятого триггеров в случае общего сброса или при завершении записи очередного байта

0 информации в ПФУ, о чем свидетельствует снятие сигнала запроса от ПФУ.

Введение перьогоГэлемента задержки и его связей обеспечивает задержку сигнала обращения к порту общего программного

5 сброса на время, достаточное для установки сигнала на информационном входе второго триггера.

Введение второго элемента задержки и его связей обеспечивает задержку сигнала обращения к порту маски режима устройства на время, необходимое для установки кода маски на информационных входах первого регистра.

Введение третьего элемента задержки и его связей обеспечивает задержку сигнала обращения к порту номера активного ПФУ на время, необходимое для установки кода номера активного ПФУ на информационных входах второго регистра.

Введение четвертого элемента задержки и его связей обеспечивает задержку сигнала обращения к порту данных при их записи в ПФУ на время, необходимое для установки очередного байта данных на информационных входах третьего регистра.

Введение пятого элемента задержки и его связей обеспечивает задержку сигнала записи данных в третий регистр в режиме ПДП на время, необходимое для установки байта данных на информационных входах третьего регистра.

Введение шестого элемента задержки и его связей обеспечивает задержку сигнала выбора активного ПФУ на время, необходимое для установки номера активного ПФУ на вторых информационных входах-выходах устройства.

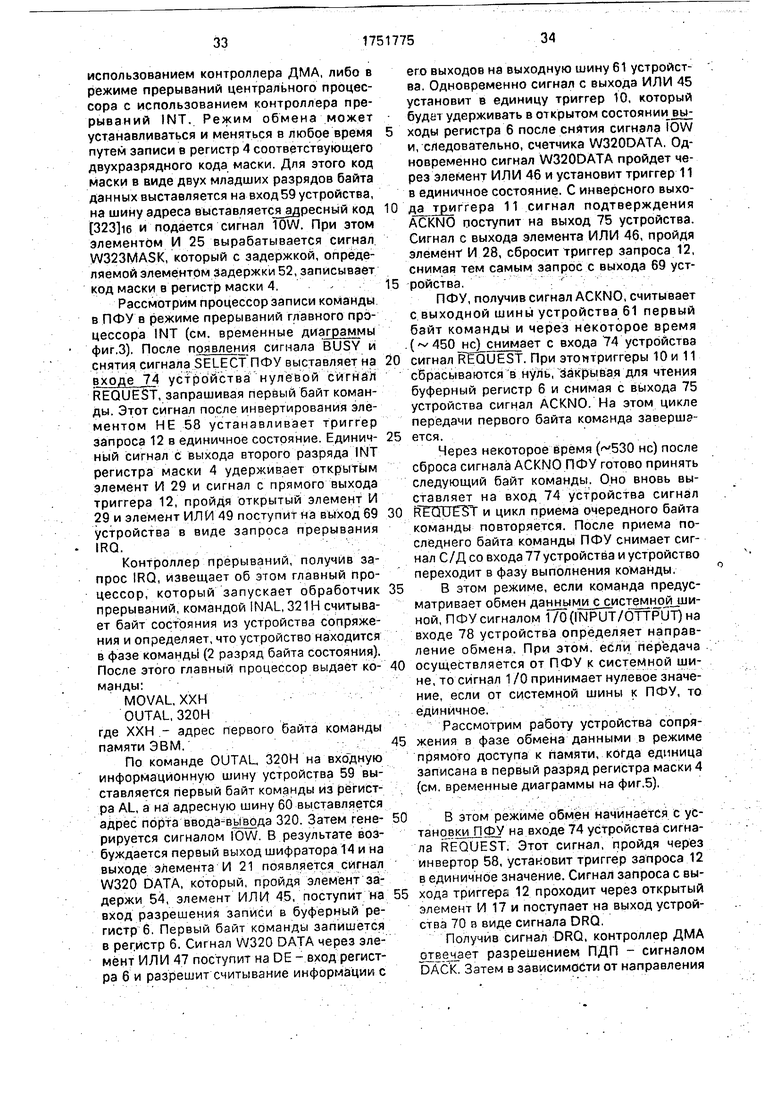

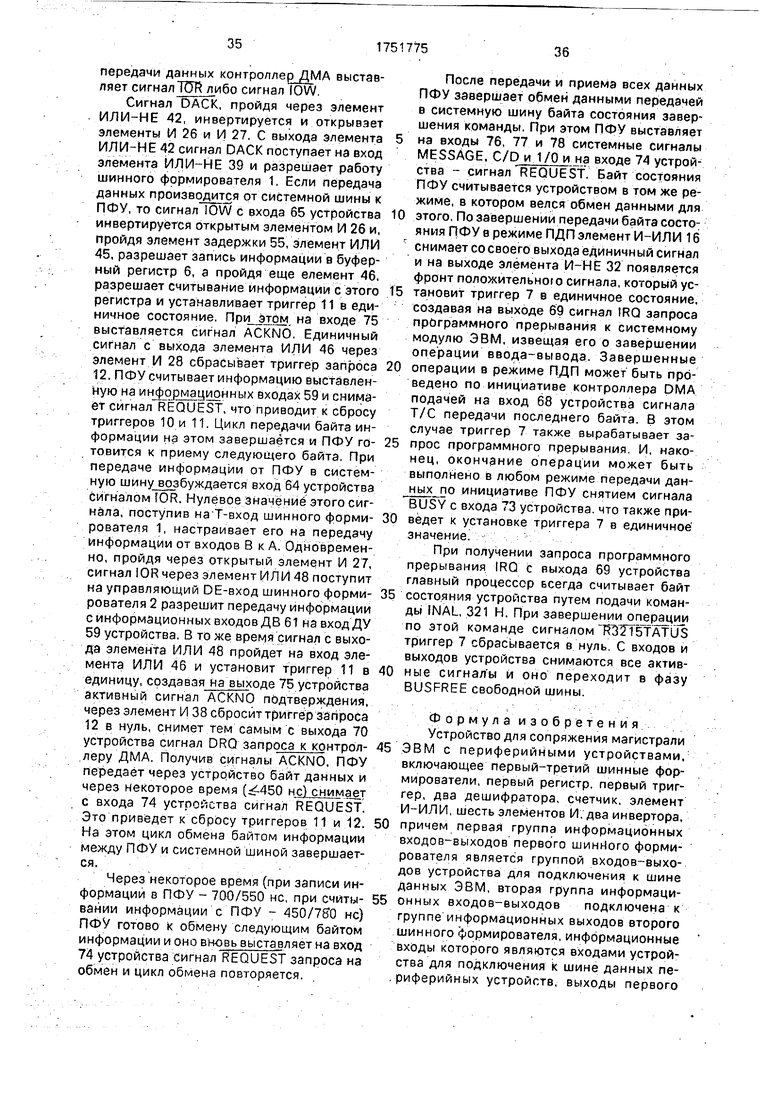

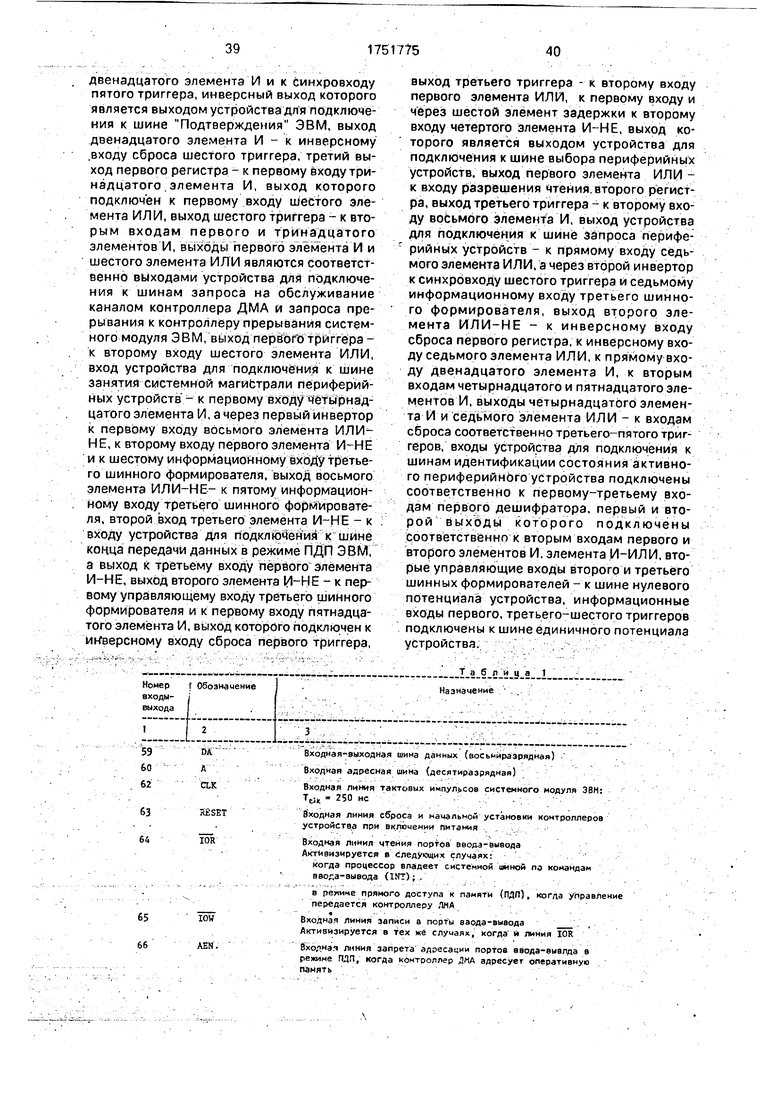

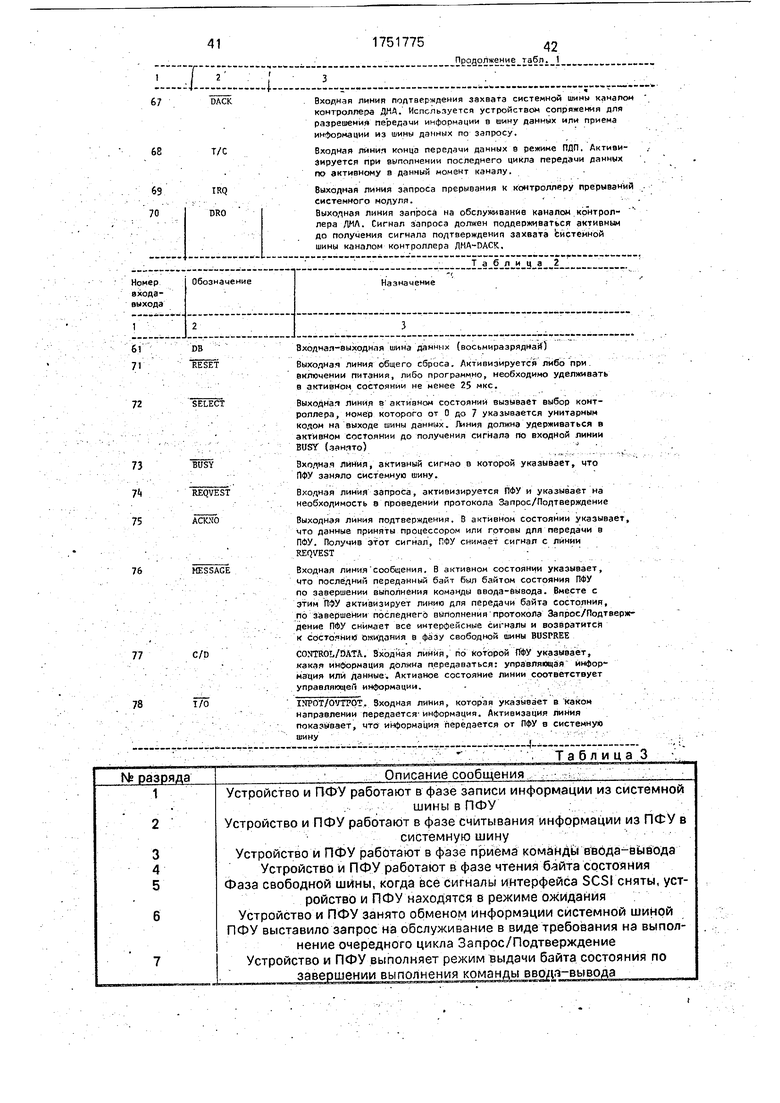

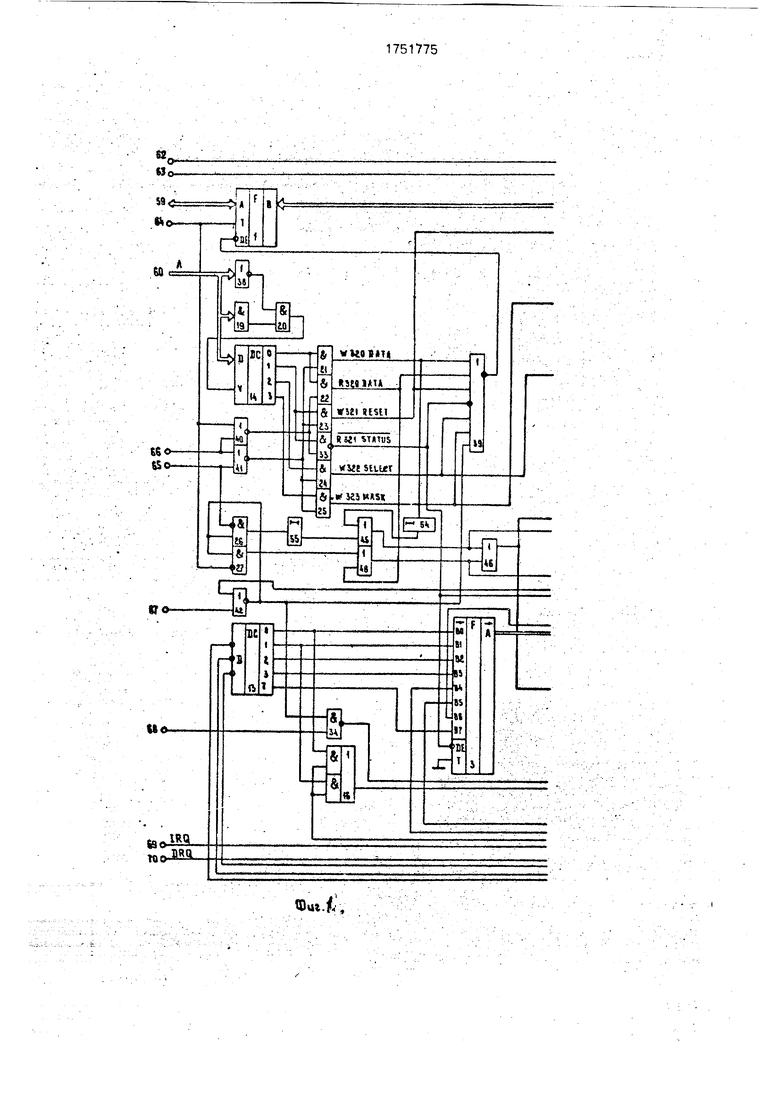

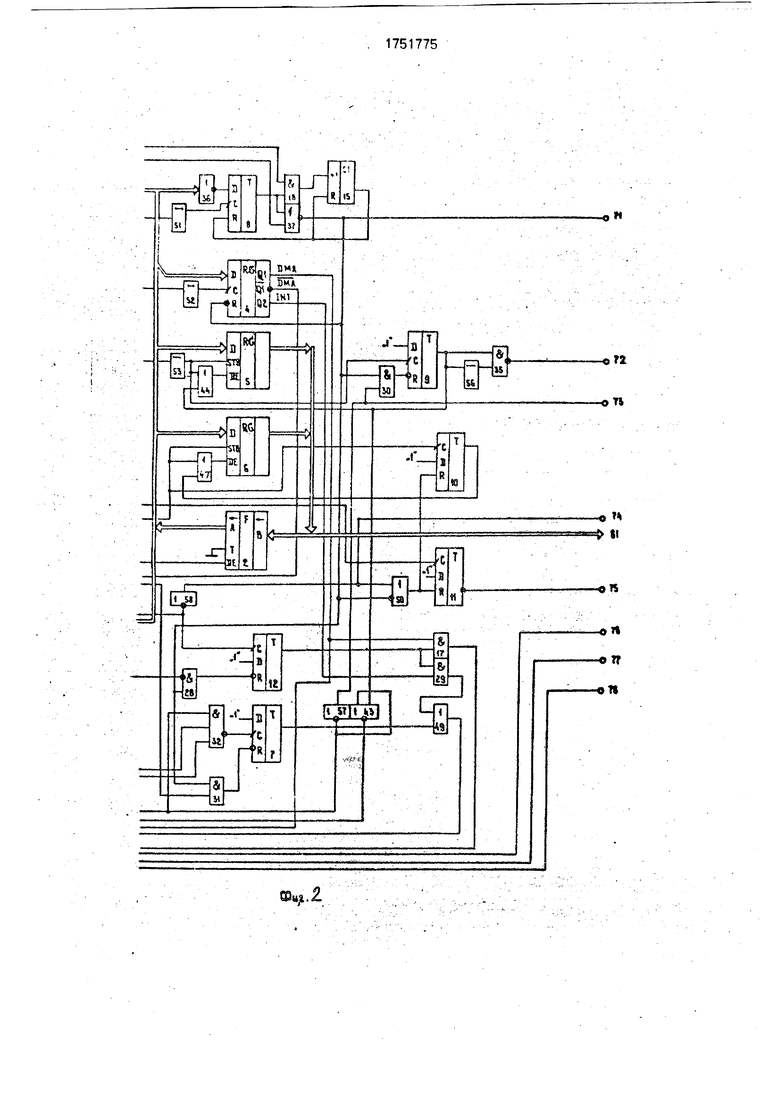

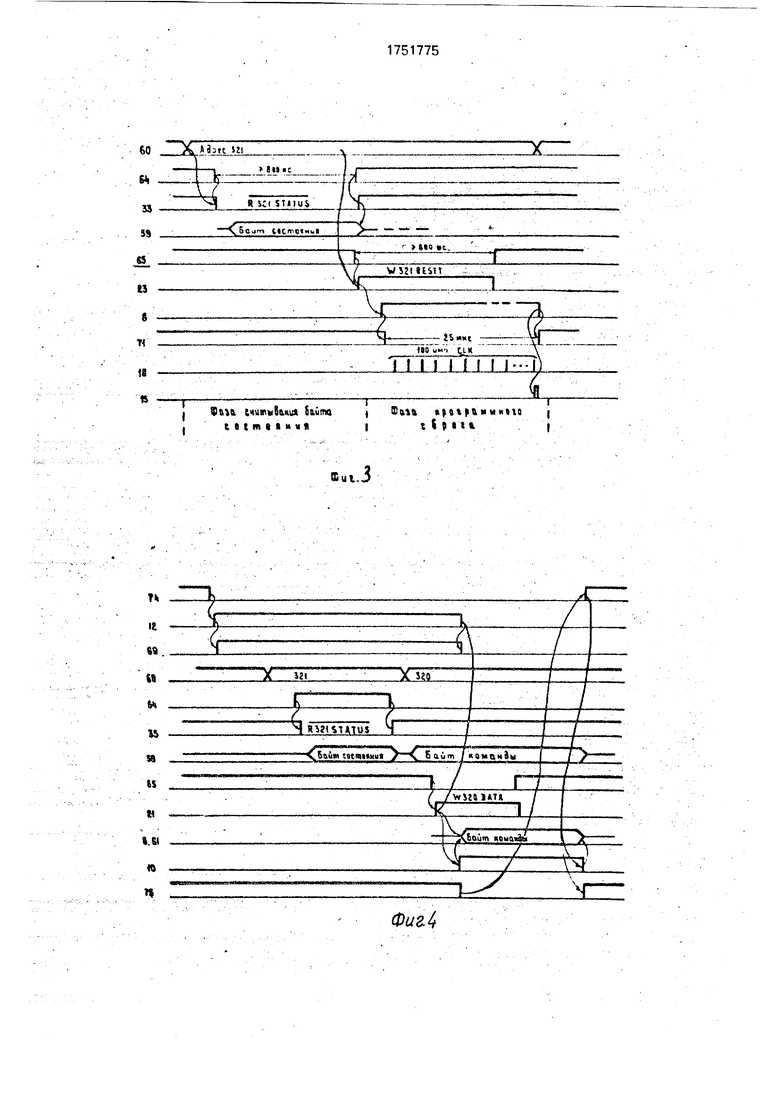

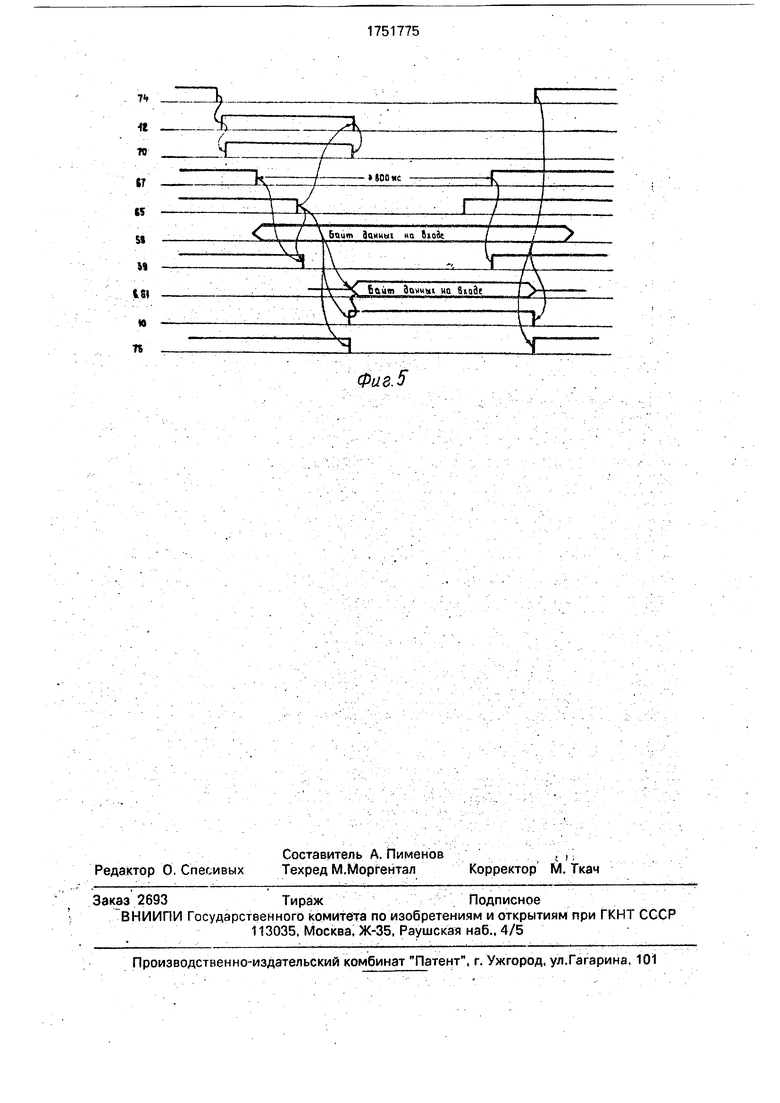

На фиг.1, 2 приведена функциональная схема устройства для сопряжения магистрали ЭВМ с периферийными устройствами; на фиг.З-временные диаграммы работы устройства в фазах считывания байта состояния устройства и программного сброса; на фиг.4 - то же, в фазе записи в П ФУ команды в режиме прерываний главного процессора; на фиг.5 - то же, в фазе записи в ПФУ данных в режиме прямого доступа к памяти.

Устройство для сопряжения магистрали ЭВМ с периферийными устройствами содержит первый-третий шинные формирователи 1-3, первый-третий регистры 4-6, первый-шестой триггеры 7-12, первый 13 и второй 14 дешифраторы , счетчик 15, элемент И-ИЛИ 16, первый-пятнадцатый эле- менты И 17-31, лервый-четвертый элементы И-НЕ 32-35, первый-восьмой элементы ИЛ И-НЕ 36-43, первый-седьмой элементы ИЛИ 44-50, первый-шестой элементы 51-56 задержки, первый 57 и второй 58 инверторы, а также две группы входов и выходов. Первая группа включает шины и линии системной магистрали в стандарте интерфейса M-BUS. Обозначение, назначение и номера входов-выходов этих шин и линий приведены в табл.1, Вторая группа включает шины и линии интерфейса SCSI. Обозначения, назначение и номера этих шин и линий приведены в табл.2.

В устройстве первая входная-выходная информационная шина DA 59 устройства

подключена к первым информационным входам-выходам А первого шинного формирователя 1, вторые информационные входы-выходы В которого подключены к 5 информационным выходам А второго шинного формирователя 2. Информационные входы В второю шинного формирователя 2 подключены к второй входной-выходной информационной шине ДВ устройства. Пять

0 выходов первого дешифратора 13 подключены к первому ВО, второму В1, третьему В2, четвертому ВЗ и восьмому В7 информационным входам третьего шинного формирователя 3. Первый выход ДМА первого

5 регистра 4 подключен к первому входу первого элемента И17, выход первого элемента И-НЕ 32 подключен к синхровходу первого триггера 7. Вторые информационные входы-выходы В первого шинного

0 формирователя 1 подключены к информационным входам 4, второго 5, третьего 6 регистров, к информационным выходам А третьего шинного формирователя 3 и к входам первого элемента ИЛИ-НЕ 36, выход

5 которого подключен к информационному входу второго триггера 8 Выход второго триггера 8 подключен к первым входам второго элемента И 18 и второго элемента ИЛИ-НЕ 37, выход которого является выхо0 дом общего сброса RESET 71 устройства. Второй вход второго элемента ИЛИ-НЕ 37 подключен к входу общего сброса RESET 63 устройства, а второй вход второго элемента И 18 подключен к входу 62 синхропоследо5 вательности CLK устройства. Выход второго элемента И 18 подключен к счетному входу счетчика 15, выход переполнения которого подключен к своему входу сброса и к входу сброса второго триггера 8. Входная адрес0 ная шина АбО подключена к информационным входам второго дешифратора 14, к входам третьего элемента И 19 и третьего элемента ИЛИ-НЕ 38, выходы которых подключены соответственно к первому и второ5 му входам четвертого элемента И 20. Выход четвертого элемента И 20 подключен к управляющему входу второго дешифратора 14, первый выход которого подключен к первым входам пятого 21 и шестого 22

0 элементов И Второй вход второго дешифратора 14 подсоединен к первым входам седьмого элемента И 23 и второго элемента И-НЕ 33. Третий выход второго дешифратора 14 подключен к первому входу

5 восьмого элемента И 24. Четвертый выход второго дешифратора 14 подключен к первому входу девятого 25 элемента И. Выходы пятого 21, шестого 22, седьмого 23, восьмого 24 и девятого 25 элементов И, второго элемента И-НЕ 33 подключены к первым

шести входам четвертого элемента ИЛИ- НЕ 39, выход которого подключен к первому управляющему входу DE первого шинного формирователя 1, второй управляющий вход Т которого к входу 64 в вода TOR устройства. Вход 66 запрета обращения к портам ввода-вывода AEN устройства подключен к первым входам пятого 40 и шестого 41 элементов ИЛИ-НЕ, вторые входы которых подключены соответственно к входам вывода IOR 64 и ввода ТЩ7 65 устройства. Выход пятого элемента ИЛИ-НЕ 40 подключен к вторым входам шестого элемента И 22 и второго элемента И-НЕ 33 Выход шестого элемента ИЛИ-НЕ 41 подключен к вторым входам пятого 21, седьмого 23, восьмого 24 и девятого 25 элементов И. Выход седьмого элемента И 23 через первый элемент задержки 52 подключен к синхровходу второго триггера 8, выход девятого элемента И 25 через второй элемент задержки 53 подключен к синхровходу первого регистоа 4. Выход восьмого элемента И 24 через третий элемент задержки 53 подключен к управляющему входу записи STB второго регистра 5, к синхровходу третьего триггера 9 и к первому входу первого элемента ИЛИ 44. Выход пятого элемента И 21 через четвертый элемент задержки 54 подключен к первому входу второго элемента ИЛИ 45, выход которого подсоединен к управляющему входу записи STB третьего регистра 6, к синхровходу четвертого триггера 10, к первым входам третьего 46 и четвертого 47 элементов ИЛИ. Выход четвертого триггера 10 подключен к второму входу четвертого элемента ИЛИ 47. выход которого подсоединен к управляющему входу считывания ДЕ третьего регистра 6, информационные выходы второго 5 и третьего 6 регистров подключены к выходной информационной шине ДВ61 устройства. Первый выход ДМА первого регистра 4 подключен к входам обоих элементов И элемента И-ИЛИ 16, выход которого подключен к первому входу первого элемента И-НЕ 32. Второй инверсный выход ДМА первого регистра 4 подключен к первому входу седьмого элемента ИЛИ-НЕ 42, второй вход которого подключен к управляющему входу 67 устройства подтверждения режима ПДП DACK а выход подключен к седьмому входу четвертого элемента ИЛИ- НЕ 39, к первому входу третьего элемента И-НЕ 34 и к прямым входам десятого 26 и одиннадцатого Т1 элемента И, инверсные входы которых подключены соответственно к управляющим входам ввода IOW 65 и вывода 40R 64 устройства. В ыход десятого элемента И 26 через пятый элемент задержки 55 подключен к второму входу второго элемента ИЛИ 45. Выход одиннадцатого элемента И 27 подключен к первому входу пятого элемента ИЛИ 48, выход которого подсоединен к второму входу третьего элемента ИЛИ 46 и к первому управляющему входу ДЕ второго шинного формирователя 2. Второй вход пятого элемента ИЛИ 48 подключен к второму входу четвертого элемента ИЛИ-НЕ 39. Выход третьего элемента ИЛИ

0 46 подключен к инверсному входу двенадцатого элемента И 28 и к синхровходу пятого триггера 11, инверсный выход которого является выходом подтверждения АСККГб 75 устройства. Выход двенадцатого элемента

5 И 28 подключен к инверсному входу сброса шестого триггера 12. Третий выход INT первого регистра 4 подключен к первому входу тринадцатого элемента И 29, выход которо- ro-к первому входу шестого элемента ИЛИ

0 49, Выход шестого 12 триггера подключен к вторым входам первого 17 и тринадцатого 29 элементов И. Выходы первого элемента И 17 и шестого элемента ИЛИ 49 являются соответственно выходами запроса на обслу5 живание каналом контроллера ДМА 70 и запроса прерывания к контроллеру прерывания системного модуля 69, выход первого триггера 7 подключен к второму входу шестого элемента ИЛИ 49.

0 Управляющий вход 73 занятия информационной шины BUSY подсоединен к первому входу четырнадцатого элемента И 30. а через первый инвертор 57 подключен к первому входу восьмого элемента ИЛИ-НЕ

5 43, к второму входу первого элемента И-НЕ

32и к шестому информационному входу В5 третьего шинного формирователя 3.

Выход восьмого элемента ИЛИ-НЕ 43 подключен к пятому информационному входу

0 В4 третьего шинного формирователя 3. Второй вход третьего элемента И-НЕ 34 подсоединен к входу 68 извещения о завершении обмена данными в режиме ПДП Т/С устройства, а выход - к третьему входу первого эле5 мента И-НЕ 32. Выход второго элемента И-НЕ

33подключен к первому управляющему входу ДЕ третьего шинного формирователя 3 и к первому входу пятнадцатого элемента И 31, выход которого подключен к инверсному

0 входу сброса первого триггера 7

Выход третьего триггера 9 подключен к второму входу первого элемента ИЛИ 44, к первому входу и через шестой элемент задержки 56 к второму входу четвертого элемента

5 И-НЕ 35, выход которого является выходом 72 выбора ПФУ SELECT устройства. Выход первого элемента ИЛИ 44 подключен к входу разрешения чтения ДЕ второго регистра 5. В ыход третьего триггера 9 подключен к второму входу восьмого элемента И 43 Вход

74 запроса устройства REQVCST подключен к прямому входу седьмого элемента ИЛИ 50, а через второй инвертор 58 к синхровходу шестого триггера 12 и седьмому информационному входу В6 третьего шинного формиро- вателя 3, выход второго элемента ИЛИ-НЕ 37 подключен к инверсному входу сброса первого регистра 4, к инверсному входу седьмого элемента ИЛИ 50, к прямому входу двенадцатого 28 элемента И, к вторым входам четыр- иадцатого 30 и пятнадцатого 31, элементов И, Выход четырнадцатого элемента И 30 и седьмого элемента ИЛИ 50 подключены к входам сброса соответственно третьего 9 и четвертого 10, пятого 11 триггеров. Выходы вы- вод/ввод (1 /0) 78, команда/данные (С/Д) 77 I передачи байта состояния ПФУ (MESSAGE) 76 подключены соответственно к первому, второму и третьему входам первого дешифратора 13, первый и второй выходы которого подключены к вторым входам соответственно первого и второго элементов И элемента И- ИЛИ 16, Вторые управляющие Т-входы второго 2 и третьего 3 шинных формирователей подключены к шине логического нуля. Инфор- мационные входы первого 7, третьего 9, четвертого 10, пятого 11, шестого 12 триггеров подключены к шине логической единицы.

Рассмотрим назначение элементов схемы устройства сопряжения,

Двунаправленный шинный формирователь 1 обеспечивает обмен данными внутренней шинной устройства и системной шиной ДА в двух направлениях Обмен в обоих направлениях производится восьми- разрядными словами. Направление передачи данных определяется сигналом системной шины IOR, поступающим с входа устройства 64 на Т-вход формирователя 1. При нулеТЗбм значении этого сигнала пере- дача производится в направлении от В к А, при единичном значении сигнала от А к В. Передача информации через формирователь 1 разрешается только при нулевом сигнале на его входе ДЕ, поступающем с выхода элемента ИЛИ-НЕ 39.

Шинный формирователь 3 обеспечивает передачу байта состояния устройства и некоторых сигналов интерфейса SCSI. Передача информации производится только в одном направлении от В к А, для чего на управляющий Т-вход поступает сигнал логического нуля. Передача байта состояния во внутреннюю шину устройства осуществляется при нулевом сигнале на ДЕ-входе фор- мирователя 3, который поступает с выхода элемента И-НЕ 33 и является сигналом D321 STATUS элемента И-НЕ 33 и является сигналом также адресации фиктивного порта с номером 321, принимающим активное

значение в режиме считывания Значение разрядов байта и их описание приведено в табл.3.

Регистр 4 является двухразрядным регистром маски (порт 323) и предназначен для установки режима передачи данных. При единичном значении первого разряда обмен данными между ЭВМ и ПФУ производится в режиме прямого доступа к памяти (ПДП), при единичном значении второго разряда обмен информацией производится в режиме передачи прерываний к процессору. Запись кода маски производится в регистр 4 из внутренней шины устройства по переднему фронту сигнала W323MASK, который является сигналом адресации 323 порта в режиме записи и поступает на син- хровход регистра 4 с выхода элемента И 25 через элемент задержки 52. Сброс регистра 4 BjHVflb осуществляется нулевым сигналом RESET сброса, поступающего с выхода элемента ИЛИ-НЕ 37 на R-вход регистра 4, .

Регистр 5 является регистром номера ПФУ (порт 322) и служит для выбора одного из ПФУ, имеющих общую схему управления (контроллер). Запись унитарного кода номера ПФУ в регистр 5 осуществляется из внутренней шины устройства сигналом W322SELECT, который является сигналом адресации порта с номером 322 и поступает на управляющий вход STB регистра 5 с выхода элемента И 24 через элемент задержки 53. Этот же сигнал, пройдя через элемент ИЛИ 44 по второму управляющему входу ДЕ регистра 5, разрешает считывание информации с информационных выходов в выходную шину устройства ДВ 61 Режим считывания с выходов регистра 5 затем удерживается в течение времени, достаточного для выбора ПФУ сигналом с прямого выхода триггера 9, который поступает на управляющий входДЕ регистра 5 через второй вход элемента ИЛИ 44

Регистр 6 является буфером данных (порт 320), подлежащих передаче от системной шины к входной шине ДВ для последующей записи в ПФУ Запись в регистр 6 осуществляется сигналом W320DATA, который является сигналом адресации порта с номером 320 в режиме записи и поступает на управляющий вход STB регистра 6 с выхода элемента И 21 через элементы ИЛИ 45 и 46 и элемент задержки 54, Этот же сигнал, пройдя через элемент ИЛИ 47 обеспечивает подключение информационных выходов регистра 6 к выходной информационной шине ДВ устройства 61 Затем подключение информационных выходов регистра и выходной информационной шины 61 устройства сохраняет на необходимое время единичный сигнал с выхода триггера 10, который поступает на управляющий вход ДЕ регистра через второй вход элемента ИЛИ 47.

Триггер 8 обеспечивает формирование управляющего сигнала RESET сброса устройства и ПФУ заданной длительности, составляющей в стандёрте интерфейса SCSI не менее 25 мкс, при программном сбросе. Установка триггера 8 в единичное состоя- ние осуществляется передним фронтом сигнала W321RESET, который адресует фиктивный порт сброса с номером 321 в режиме записи и вырабатывается элементом И 23. Установка триггера 8 в единичное состояние осуществляется только при нулевой инфоомации во входной шине данных ДА 59, о чем свидетельствует единичный сигнал на выходе элемента ИЛИ-НЕ 36, поступающий на Д-вход триггера 8. Сброс триггера в нуль по асинхронному R-входу по истечении 25 мкс осуществляется сигналом переполнения счетчика 15.

Триггер 9 обеспечивает формирование сигнала SELECT на выходе устройства. Ин- формационный вход триггера подключен к шине логической единицы Запись в триггер 9 единицы осуществляется по переднему фронту сигнала W322SELECT, который является сигналом адресации порта номера активного ПФУ, и формируется элементом И 24. Сброс триггера 9 осуществляется по инверсному асинхронному R-входу нулевым сигналом с выхода элемента И 30, который вырабатывается либо в случае подтвержде- ния выбора ПФУ сигналом BUSY с входа 73 устройства либо в случае общего сброса сигналом RESET, Сигнал с прямого выхода триггера 9 поступает на выход SELECT 72 устройства через элемент задержки 56 и элемент И-НЕ 35 Сигнал с выхода триггера 9 поступает также на вход элемента ИЛИ- НЕ 43 для формирования четвертого разряда байта состояния.

Триггер 10 обеспечивает формирование сигнала для удержания в режиме считывания по управляющему ДЕ-входу буферного регистра данных 6 Устанавливается триггер 10 в единичное состояние сигналом W320 DATA, который является адресом пор- та с адресом 320 в режиме записи данных и формируется элементом И 21. Сброс цэигге- ра 10 осуществляется либо сигналом RESET в случае общего сброса,либр единичным значением сигнала REQUEST, поступаю- щим с входа устройства 74 и подтверждающего факт записи байта данных в ПФУ с выходной информационной шины ДВ устройства 61. Единичный сигнал с выхода триггера 10, поступая через элемент ИЛ И 47

на второй управляющий вход ДЕ регистра 6. поддерживает его информационные выхо ды в открытом состоянии.

Триггер 11 предназначен для формиро- вания управляющего сигнала ACKNO в стандарте интерфейса SCSI на выходе 75 устройства. Установка триггера 11 в единичное состояние производится сигналом с выхода элемента ИЛИ 46 при адресации порта 320 в режимах записи или считывания сигналами W320DATA или R320DATA, когда производится обмен данными между системной шиной и ПФУ, Сброс триггера 11 осуществляется либо сигналом элемента ИЛИ 50 в случае общего сброса, либсмэ случае снятия ПФУ сигналом TTEQUEST при подтверждении получения информации от устройства.

Триггер 12 обеспечивает формирование сигнала готовности ПФУ к обмену информацией с системной шиной ЭВМ в режиме прерываний, когда сигнал с выхода триггера 12 через элемент И 29 передается на выход 69 устройства в качестве сигнала системной шины IRQ (запрос прерывания), либо в режиме прямого доступа к памяти, когда сигнал с выхода триггера 12 через элемент И 17 передается на выход 70 (запрос на обслуживание каналом контроллера ДМА). Установка триггера 12 в единичное значение производится передним фронтом проинг вертированного сигнала REQUEST, поступающего с выхода инвертора 58 на синхровход триггера 12. Сброс триггера 12 осуществляется нулевым сигналом с выхода элемента И 28 либо в случае общего сброса (сигнал RESET), либо в случае инициализации ЭВМ процедуры обмена информации (сигналы W320DATA. R320DATA).

Триггер 7 прерывания обеспечивает формирование сигнала готовности ПФУ и устройства сопряжения к приему очередной команды ввода-вывода процессора по причине завершения предыдущей. Он устанавливается в единичное состояние передним фронтом сигнала с выхода элемента И-НЕ 32, который формируется в трех случаях; если рсврбождается шина данных, т.е. сигнал BUSY на входе 73 устройства принимает единичное значение; при окончании фазы выполнения команды в режиме прямого доступа; если текущий цикл передачи информации в режиме прямого доступа к памяти является последним.

Сброс триггера 7 в нуль осуществляется нулевым сигналом элемента И 31, который вырабатывается либо в случае общего сброса по команде RESET, либо при обращении к порту 321 по сигналу Н 32 1 STATUS для считывания байта состояния устройства.

Дешифратор 13 предназначен для формирования 0-3 и 7 разрядов байта состояния устройства, которые вырабатываются из входных сигналов 1/0(вход 78), С/Д(вход 77) и MESSAGE (вход 76) устройства,

Дешифратор 14 служит для дешифрации двух младших разрядив адресного кода, поступающего из системной магистрали на адресный вход 60 устройства, для адресации портов ввода-вывода устройства со- пряжения, На управляющий V-вход дешифратора 14 поступает сигнал с выхода элемента И 20, который принимает единичное значение в том случае, когда старшие восемь разрядов адресного кода на вхо- де 60 устройства имеют значение А 1100ЮООХХ Н32 , где X - неопределенные разряды, т.е, адресации подлежат порты, начиная с 320, которые принадлежат рассматриваемому устройству, Выходные Сигналы дешифратора 14 используются для управления адресуемыми элементами устройства.

Счетчик 15 обеспечивает формирование временного интервала, равного 25 мкс, в течение которого на выход 71 устройства должен удерживаться сигнал RESET общего сброса при программном сбросе устройства и ПФУ. Счетные импульсы на счетный вход счетчика 15 поступают с входа 62 устройст- ва через элемент И 18, который их пропускает в случае программного сброса. Импульсная последовательность на входе 62 устройства является синхропоследова- тельностью CLK системной магистрали, пе- риод следования импульсов которой равен 25 не. Выход счетчика 15 является выходом переполнения, единичный сигнал на котором появляется после прихода сотого счетного импульса. Единичный сигнал с выхода счетчика поступает на свой вход сброса, а также на вход обнуления триггера 8.

Элемент И-ИЛИ 16 служит для формирования сигнала в режиме прямого доступа к памяти, о чем говорит единичный сигнал, поступающий на обе схемы И элемента с первого выхода ДМА регистра маски и, о том, что устройство выполняет ввод или вывод данных, о чем говорят единичные сигналы либо с первого, либо с второго выхода дешифратора 13. Выходной сигнал элемента И-ИЛИ 16 поступает на вход элемента И 32 и используется для формирования сигнала запроса прерывания устройства по окончании выполнения команды.

Элемент И 17 служит для формирования сигнала запроса DRQ на обслуживание контроллером ДМА (прямого доступа к памяти) на выходе 70 устройства. Этот сигнал принимает единичное действующее значение в том случае, если режим ПДП задан маской режима, о чем говорит единичный сигнал, поступающий на вход элемента И 17 с выхода первого разряда регистра маски 4, и при наличии запроса от ПФУ на обслуживание, о чем говорит единичный сигнал, поступающий с выхода триггера 12 на второй вход элемента И 17.

Элемент И 18 обеспечивает передачу синхроимпульсов последовательности CLK с входа 62 устройства на счетный выход счетчика 15 при программно заданном сбросе устройства и ПФУ, о чем свидетельствует единичное состояние триггера 8.

Элемент И 19 является элементом дешифратора адреса порта ввода-вывода устройства и формирует единичный сигнал в том случае, если десятый девятый и шестой разряды адресного кода на входе 60 устройства принимают значение единицы.

Элемент И 20 является элементом дешифратора адреса порта ввода-вывода устройства и формирует единичный сигнал разрешения работы дешифратора 14 в том случае, если в восьми старших разрядах адресного кода записано число А 11001000k.

Элемент И 21 формирует сигнал W320DATA адресации порта с номером 320 в режиме записи данных из системной шины в устройство, о чем свидетельствуют еди- ничные сигналы на входах элемента, поступающие с первого выхода дешифратора 14 и с выхода элемента ИЛИ-НЕ 41.

Элемент И 22 формирует сигнал R320DATA адресации порта с номером 320 в режиме чтения данных в системную шину, о чем свидетельствуют единичные сигналы на входах элемента, поступающие с первого выхода дешифратора 14 и с выхода элемента ИЛИ-НЕ 40.

Элемент И 23 формирует сигнал W321 RESET адресации фиктивного порта с номером 321 в режиме записи из системной шины и служит для программного сброса устройства и ПФУ Единичное значение принимает при возбуждении второго выхода дешифратора 14 и единичном значении сигнала ha выходе элемента ИЛИ-НЕ 40.

Элемент И 24 формирует сигнал W322SELECT адресации порта номера активного ПФУ с адресом 322 в режиме записи из системной шины в устройстве Этот сигнал принимает единичное значение при возбуждении третьего выхода дешифратора 14 и при единичном значении сигнала на выходе элемента ИЛИ-НЕ 41.

Элемент И 25 формирует сигнал W323MASK адресации порта маски режима работы устройства с адресом 323 в режиме

записи из системной шины в устройство. Сигнал принимает единичное значение при возбуждении четвертого выхода дешифратора 15 и при единичном значении сигнала на выходе элемента ИЛИ-НЕ 41.

Элемент И 26 формирует сигнал о работе устройства в режиме записи информации из системной шины при прямом доступе к памяти. Единичный сигнал на выходе этого элемента будет присутствовать в том слу- чае, если на выходе 65 устройства присутст- вует нулевой действующий сигнал IOW системной магистрали и в то же время с выхода элемента ИЛИ-НЕ 42 поступает единичный сигнал, свидетельствующий о работе устройства в режиме ПДП.

Элемент И 27 формирует сигнал о работе устройства в режиме считывания информации из ПФУ в системную шину при доступе к памяти. Нулевой сигнал ЮК ввода информации в ЭВМ поступает на инверсный вход элемента И 27 с входа 64 устройства.

Элемент И 28 формирует нулевой сигнал сброса триггера 12 запроса ПДП. во- первых, при общем сбросе сигналом RESET, поступающим с выхода элемента ИЛИ-НЕ 37 на прямой вход элемента И 28, во-вторых, при удовлетворении запроса на обслуживание контроллером ДМА, о чем свидетельст- вует нулевой сигнал, поступающий с выхода элемента ИЛИ 46 на инверсный вход элемента И 28.

Элемент И 29 формирует сигнал IRQ запроса прерывания к процессору ЭВМ, ко- торый поступает на выход 69 устройства через элемент ИЛИ 49 в том случае, если в устройстве установлен режим обмена данными по запросам прерывания, о чем свидетельствует единичный сигнал с выхода второго разряда регистра 4 маски и триггер 6 запроса находится в единичном состоянии.

Элемент И 30 формирует нулевой сигнал сброса триггера 9 либо при общем сбро- се по сигналу RESET, поступающему на первый вход элемента И 30, либо при подтверждении выбора, адресуемого ПФУ. о чем свидетельствует нулевой сигнал BUSY, поступающий с входа 73 устройства на вто- рой вход элемента И 30.

Элемент И 31 формирует нулевой сигнал сброса триггера 7 запроса прерывания, во-первых, при общем сбросе по сигналу RESET, поступающего на первый вход эле- мента И 31, во-вторых, при поступлении на второй ход элемента И 31 сигнала R321 STATUS с выхода элемента И-НЕ 33, что говорит о начале обработки запроса прерывания микропроцессором ЭВМ.

Элемент И-НЕ 32 формирует сигнал установки в единицу триггера 7 запроса прерывания.

Единичный фронт на его инверсном выходе появляется, во-первых, при окончании выполнения процедуры обмена данными в режиме ПДП, о чем свидетельствует снятие единичного сигнала с выхода элемента И- ИЛИ 16, во-вторых, при освобождении шины данных, о чем свидетельствует снятие единичного сигнала BUSY с выхода инвертора 57, и, в-третьих, когда текущий цикл передачи информации в режиме ПДП является прследним, о чем свидетельствует появление нулевого сигнала на выходе элемента И-НЕ 34.

Элемент И-НЕ 33 формирует сигнал R321 STATUS адресации порта с номером 321 в режиме чтения в общую магистраль байта состояния устройства. Этот сигнал принимает нулевое действующее значение при возбуждении второго выхода дешифратора 14 и при появлении единичного сигнала на выходе ИЛИ--НЕ 40.

Элемент И-НЕ 34 формирует нулевой сигнал завершения процедуры обмена информации в режиме ПДП. Для этого на первый выход элемента И-НЕ 34 поступает единичный сигнал с выхода элемента ИЛИ- НЕ 42 о том, что устройство работает в режиме ПДП, а на второй вход с входа 68 устройства поступает сигнал Т/С о том, что текущий цикл обмена информацией в режиме ПДП является последним.

Элемент И-НЕ 35 передает на выход устройства 72 сигнал SELECT выбора адресуемого ПФУ с некоторой задержкой, определяемой элементом задержки 56.

Элемент ИЛИ-НЕ 36 формирует единичный сигнал на информационном входе триггера 8 программного общего сброса при отсутствии информации во внутренней шине устройства.

Элемент ИЛИ-НЕ 37 формирует обобщенный сигнал c6poca R ESET на выходе 71 устройства, во-первых, при сбросе после включения питания, о чем свидетельствует сигнал RESET на входе 63 устройства, и, во-вторых, при программном сбросе, когда триггер 8 устанавливается в единичное состояние

Элемент ИЛИ-НЕ 38 является частью дешифратора адреса порта ввода-вывода устройства, на его входы поступают 8, 7, 5, 4 и 4-й разряды адресного кода А с входа 60 устройства. При адресации 32 порта ввода- вывода на выходе элемента ИЛИ-НЕ 38 появляется единичный сигнал,

Элемент ИЛИ-НЕ 39 формирует нулевой разрешающий сигнал, поступающий на

управляющий вход ДЕ первого шинного формирователя 1 и разрешающий передачу через него информации в том случае, если адресуется один из портов ввода-вывода устройства. Для этого на его входы поступа- ют все сигналы адресации портов ввода-вывода и сигнал захвата системной шины ДАСК контроллером ДМА при исполнении режима ПДП.

Элемент Ш1И-НЕ 40 передает инверс- мое значение сигнала IOR чтения информации из ЛФУ дли формирования сигналов обращения к портам ввода-вывода устройства в режиме считывания элементами И 22 и И-НЕ 33 при условии, если контроллер ДМА не адресует оперативную память, о чем свидетельствует нулевой с.игнал AEN на входе 66 устройства

Элемент ИЛИ-НЕ 41 передает инверсное значение сигнала IOW - записи инфор- мации в ПФУ для формирования сигналом обращения к портам ввода-вывода устройства в режиме записи элементами И 21, И 23 и И 24, И 25 при условии, если контроллер ДМА не адресует оперативную память в это время.

Элемент ИЛИ-НЕ 42 формирует сигнал, единичное значение которого свидетельствует о работе устройства в режиме ПДП, о чем свидетельствует нулевое значение сиг- налое, поступающих на его входы, во-пер- вых, с входа 67 устройства сигнала DACK о захвате системной шины контроллером ДМА и, во-вторых, с инверсного выхода первого разряда регистра маски режима 4 сиг- нала ДМА об установке в устройстве режима ПДП.

Элемент ИЛ И-НЕ 43 формирует сигнал BUSFREE, единичное значение которого свидетельствует о том, что устройство не использует системную шину. Этот сигнал используется в четвертом разряде байта состояния. Сигнал на выходе элемента ИЛИ-НЕ 43 имеет значение, если ПФУ выставило на входе 73 сигнал BUSY 1, что говорит о том, что ПФУ не использует системную шину, и с инверсного выхода триггера 9 снимается единичное значение сигнала, что говорит1 о том, что устройство не выбирает какое-либо из подключенных к нему ПФУ,

Элемент ИЛИ 44 формирует сигнал, поступающий на DE-вход регистра 5 адреса активного ПФУ и разрешающий считывание информации с его выходов. Считывание ин- формации разрешается, во-первых, при адресации 322 порта в режиме записи для передачи номера выбираемого ПФУ в выходную шину данных 61 и, во-вторых, при сохранении на выходе треггера 9 единичного сигнала до тех пор, пока выбор и подключение адресуемого ПФУ не произойдет, о чем будет свидетельствовать нулевое значение сигнала BUSY на входе 73 устройства,

Элемент ИЛИ 45 формирует сигнал записи байта данных в буферный регистр 6 из системной шины на его разрешающем STB- входе в том случае, если адресуется порт с номером 320 в режиме записи в ПФУ, либо в устройстве осуществляется запись информации в ПФУ в режиме прямого доступа к памяти, о чем свидетельствует единичный сигнал с выхода элемента И 26

Элемент И 46 формирует обобщенный сигнал о том, что устройство ведет обмен данными между системной шиной и ПФУ либо в режиме записи (единичный сигнал с выхода элемента ИЛИ 45), либо в режиме чтения (единичный сигнал с выхода элемента ИЛИ 48). Этот сигнал используется для установки триггера 11 подтверждения захвата системной шины в единичное значение и сброса триггера запроса 12

Элемент ИЛИ 47 формирует сигнал разрешения считывания информации с выходов буферного регистра 6 с момента его адресации единичным сигналом с выхода элемента ИЛИ 45 до момента получения этой информации ПФУ, о чем свидетельствует снятие нулевого сигнала REQUEST с входа устройства 74, что вызовет сброс в нуль триггера 10, прямой выход которого подключен к входу элемента ИЛИ 47.

Элемент ИЛИ 48 формирует сигнал чтения байта данных их ПФУ через шинный формирователь 2, который поступает на его ДЕ-выход Единичный сигнал на выходе элемента ИЛИ 48 вырабатывается либо при адресации порта с номером 320 в режиме чтения из ПФУ, о чем говорит единичный сигнал с выхода элемента И 22, либо при чтении информации в режиме ПДП, о чем говорит единичный сигнал с выхода элемента И 27,

Элемент И 49 передает сигнал IRQ запроса прерывания на выход 69 устройство либо с выхода триггера запроса прерывания 7, когда завершена очередная процедура ввода-вывода, либо с выхода триггера 12, через элемент И 29, когда запрос выставля- ет ПФУ путем подачи сигнала REQUEST и в устройстве установлен режим обмена с использованием прерываний процессора.

Элемент И 50 служит для обнуления триггера 1Q и 11, во-первых, при поступлении сигнала RESET общего сброса, во-вторых, при снятии сигнала REQUEST запроса на обслуживание от ПФУ, поступающего на вход 74 устройства

Элемент задержки 51 обеспечивает задержку сигнала адресации W321 RESET на время, достаточное для установки на информационном входе триггера 8 программного общего сброса устойчивого сигнала едини- цы.

Элемент задержки 51 обеспечивает задержку сигнала адресации W321 RESET на время, достаточное для установки на информационном входе триггера 8 программного общего сброса устойчивого сигнала единицы.

Элемент задержки 52 обеспечивает за- держку сигнала адресации W323MASK на время, достаточное для установки наинфор- мационных входах регистра 4 маски режима устойчивого значения кода маски,

Элемент задержки 53 обеспечивает задержку сигнала адресации W322SELECT на время, достаточное для установки на инфор- мационных входах регистра 5 номера активного ПФУ устойчивого значения унитарного кода номера ПФУ,

Элемент задержки 54 обеспечивает задержку сигнала адресации W320DATA на время, достаточное для установки на информационных входах буферного регистра б ус- тройчивого значения байта записываемых в ПФУ данных.

Элемент задержки 55 обеспечивает за- держку сигнала с выхода элемента И 26 на время, достаточное для установки на информационных входах буферного регистра 6 устойчивого значения байта записываемых данных.

Элемент задер жки 56 задерживает появление сигнала SELECf на выходе 72 устройства на время, необходимое для установки кода номера активного ПФУ на выходной информационной шине 61.

Инвертор 57 предназначен для получения инверсного значения сигнала занятия ПФУ системной шины BUSY.

Инвертор 58 предназначен для получения инвертированного значения сигнала за- проса обслуживания ПФУ REQUEST.

Рассмотрим работу устройства сопряжения. После включения питания системный модуль ЭВМ посылает на вход 63 устройства сигнал RESET положительной полярности. Этот сигнал, пройдя через элемент ИЛИ-НЕ 37, будет выставлен на выхо- е 71 устройства в виде инверсного сигнала RESET, который поступает в ПФУ и устанавливает узлы в исходное состояние. Длитель- ность сигнала должна быть не менее 25 мкс. Одновременно нулевой сигнал с выхода элемента ИЛ 1/1-Н Е 37 сбрасывает в нуль регистр 4 маски рожима, пройдя через элемент И 30, сбрасывает триггер 9 выбора

активного ПФУ, проинвертированный элементом ИЛИ 50, сбрасывает в нуль триггеры 10 и 11, пройдя через элемент И 28 и 31, сбрасывает в нуль триггеры 12 и 7 соответственно. После этого устройство готово к выполнению команд процессора ввода-вывода информации.

Процедура обращения к ПФУ начинается с чтения из устройства байта состояния. Эта фаза работы устройства состоит в следующем (см. временные диаграммы на фиг.З). Главный процессор выставляет на адресный вход 60 устройства десятирэзряд- ный адрес порта ввода-вывода с номером 321ie. Через определенное время (50 не) главный процессор выставляет на устройства низкий уровень сигнала IOR, который настраивает шинный формирователь 1 на передачу информации от входов В к А, т.е. на считывание информации от входов В к А, т.е. на считывание информации из устройства в системную шину через вход-выход 59 устройства. Адресный код А 11.001000001 }i распределяется между элементами неполного адресного дешифратора следующим образом: разряды 10, 9 и 6 поступают на входы элемента И 19, разряды 8, 7, 5, 4 и 3 поступают на входы элемента ИЛИ-НЕ 38, разряды 2 и 1 на информационный входы дешифратора 14. В результате на выходах элементов И 19 и ИЛИ-НЕ 38 появляются единичные сигналы, которые создают на выходе элемента И 20 единичный сигнал, чем откроют дешифратор 14 по управляющему V-входу. В результате дешифрации двух младших разрядов адресного кода возбужденным окажется первый выход дешифратора 14. Единичный сигнал с этого выхода поступит на первый вход элемента И-НЕ 33. На второй вход элемента И-НЕ 33 поступит с выхода элемента ИЛИ-НЕ 40 при условии единичного сигнала AEN на выходе 66 устройства проинвертированный сигнал IOR. В результате элемент И-НЕ 33 выработает, нулевой действующий сигнал R321 STATUS считывания байта состояния из 321 порта ввода-вывода. Этот сигнал пройдет через элемент ИЛИ-НЕ 39 и по входу ДЕ разрешит работу шинного формирователя 1. В то же время этот сигнал разрешит передачу информации через шинный формирователь 3 и байт состояния считывается через шинные формирователи 3 и 1 в системную шину.

Главный процессор анализирует содержимое четвертого разряда BUSFREE байта состояния. Если этот разряд имеет единичное значение, то устройство и ПФУ находятся в фазе свободной шины и можно

продолжать с ними процедуру инициализации ввода-вывода, В противном случае главный процессор, выяснив причину занятости устройства и ПФУ, может либо ожидать их освобождения, либо произвести их программный сброс.

Фаза программного сброса осуществляется следующим образом (см. временные диаграммы на фиг.З). Центральный процессор выставляет на адресный вход 60 устрой- ства адресный код порта ввода-вывода с номером 321 (он может и не сниматься после считывания байта состояния и выставляться через некоторое время на входе 65 устройства сигнал IOW). При этом на входе 64 присутствует единичный сигнал IOR, В результате шинный формирователь 1 настраивается на передачу информации от входов А и В. Единичные сигналы, поступающие с первого входа дешифратора 14 и с выхода элемента ИЛИ-НЕ 27, формируют единичный сигнал W321RESET записи информации в 321 порт ввода-вывода на выходе элемента И 23. Этот сигнал, задержанный на элементе задержки 51 на время, необходимое для переключения шинных формирователей 1 и 3, поступает на синхровход триггера 8. Так как на входной информационной шине 59 присутствует нулевая информация, то на выходе элемента ИЛИ-НЕ 36 будет присутствовать единичный сигнал, который по переднему фронту сигнала на синхровходе триггера 8 установит триггер 8 в единичное состояние Единичный выходной сигнал триггера 8, проинвертированный элементом ИЛИ-НЕ 37, поступит на выход 71 устройства в качестве сигнала RESET v вызовет такиеже действия, как при сбросе устройства и ПФУ при выключении питания, Единичный сигнал с выхода триггера 8 откроет элемент И 18 и синхроимпульсы CLK главного процессора с периодом следования Т 250 не с входа 62 устройства будет поступать на счетный вход счетчика 15 через элемент И 18 По проше- ствии 100 импульсов CLK счетчик 15 выдаст импульс переполнения, который обнулит .счетчик 15 и триггер 8. При этом сигнал RESET с выхода 71 устройства будет снят. Время действия сигнала RESET будет со- ставлять не менее 25 мкс

Для инициализации операции ввода- вывода при нахождении устройства и ПФУ в фазе свободной шины главный пооцес- сор проводит следующую процедуру.- выбор активного ПФУ. В этой фазе главный процессор посылает в системную шину команду: OUTAL, 322H (где AL - унитарный код номера ПФУ) Работа устройства в этой фазе иллюстрируется временными диаграмма ми на фиг.4.

На адресные входы 60 устройства вы ставляется адрес порта с номером При этом возбуждается второй вход дешифратора 14. На информационную шину 59 выставляется унитарный код номера активного ПФУ. Через некоторое время (50 не) на входе 65 выставляется сигнал fOW, который в условии нулевого сигнала AEN инвертируется элементом ИЛИ-НЕ 41 и приводит к формированию на выходе элемента И 24 единичного сигнала W322SELECT, который, во-первых, создаст нулевой сигнал на выходе элемента ИЛИ-НЕ 39 и разрешит передачу информации через шинный формирователь 1 в направлении от А к В, которое определяется единичным сигналом IOR на Т-входе, во-вторых, с задержкой, определяемой элементом задержки 53 запишет унитарный код номера активного ПФУ в регистр 5 и, пройдя через элемент ИЛИ 44, разрешит считывание информации из регистра 5 через входную информационную шину 61. Задержанный сигнал W322SELECT своим передним фронтом установит триггер 9 в единичное состояние. Единичный сигнал с выхода триггера 9 поступает на вход элемента ИЛИ-НЕ 43 устанавливает его в нулевое состояние, снимая тем самым в четвертом разряде байта состояния сообщение BUSFREE о Фазе свободной шины, а через некоторое время, определяемое элементом задержки 56, сформирует на выходе элемента И-НЕ 35 нулевой действующий сигнал SELECT на выходе 72 устройства, и поступит на второй вход элемента ИЛИ 44, удерживая регистр 5 в режиме считывания информации по Е вход после снятия сигнала W322SELECT.

Приняв байт номера активного ПФУ, групповой контроллер, осуществив процедуру выбора, выставив на вход 73 устройства сигнал BUSY нулевой уровень которого через элемент И 30 сбросит триггер 9 в нуль, прекратит доступ кода активного ПФУ на входную шину 61 устройства Пройдя через инвертор 57, сигнал BUSY установит одноименный пятый разряд байта состояния в единицу и через элемент ИЛИ-НЕ 43 продолжит удержание четвертого разряда BUSFREE байта состояния в нулевом состоянии Примерно через 30 не после появления сигнала BUSY групповой контроллер выставляет на вход 77 устройства сигнал С/Д (СОММА ND/DATA), указывая на начало фазы команды.

Запись команды, как и обмен данными, может производиться устройством либо в режиме прямого доступа к памяти ПДП с

использованием контроллера ДМА, либо в режиме прерываний центрального процессора с использованием контроллера прерываний INT. Режим обмена может устанавливаться и меняться в любое время путем записи в регистр 4 соответствующего двухразрядного кода маски. Для этого код маски в виде двух младших разрядов байта данных выставляется на вход 59 устройства, на шину адреса выставляется адресный код и подается сигнал 10W. При этом элементом И 25 вырабатывается сигнал W323MASK, который с задержкой, определяемой элементом задержки 52, записывает код маски в регистр маски 4..

Рассмотрим процессор записи команды в ПФУ в режиме прерываний главного процессора INT (см. временные диаграммы фиг.З). После появления сигнала BUSY и снятия сигнала SELECT ПФУ выставляет на входе 74 устройства нулевой сигнал REQUEST, запрашивая первый байт команды. Этот сигнал после инвертирования элементом НЕ 58 устанавливает триггер запроса 12 в единичное состояние. Единич- ный сигнал с выхода второго разряда INT регистра маски 4 удерживает открытым элемент И 29 и сигнал с прямого выхода триггера 12, пройдя открытый элемент И 29 и элемент ИЛИ 49 поступит на выход 69 устройства в виде запроса прерывания IRQ.

Контроллер прерываний, получив запрос IRQ, извещает об этом главный процессор, который запускает обработчик прерываний, командой INAL, 321H считывает байт состояния из устройства сопряжения и определяет, что устройство находится в фазе команды (2 разряд байта состояния). После этого главный процессор выдает ко- манды:

MOVAL, ХХН

OUTAL, 320H

где ХХН - адрес первого байта команды памяти ЭВМ.

По команде OUTAL, 320H на входную информационную шину устройства 59 выставляется первый байт команды из регистра AL, а на адресную шину 60 выставляется адрес порта ввода-вшюда 320. Затем гене- рируется сигналом IOW В результате возбуждается первый выход шифратора 14 и на выходе элемента И 21 появляется сигнал W320 DATA, который, пройдя элемент задержи 54, элемент ИЛИ 45, поступит на вход разрешений записи в буферный регистр 6. Первый байт команды запишется в регистр 6. Сигнал W320 DATA через элемент ИЛИ 47 поступит на DE - вход регистра 6 и разрешит считывание информации с

его выходов на выходную шину 61 устройства, Одновременно сигнал с выхода ИЛИ 45 установит в единицу триггер 10, который буды удерживать в открытом состоянии ходы регистра 6 после снятия сигнала fOW и, следовательно, счетчика W320DATA. Одновременно сигнал W320DATA пройдет через элемент ИЛИ 46 и установит триггер 11 в единичное состояние. С инверсного выхо- да гр иггера 11 сигнал подтверждения ACKNO поступит на выход 75 устройства. Сигнал с выхода элемента ИЛИ 46, пройдя элемент И 28, сбросит триггер запроса 12, снимая тем самым запрос с выхода 69 устройства.

ПФУ, получив сигнал ACKNO, считывает с выходной шины устройства 61 первый байт команды и через некоторое время (v 450 не) снимает с входа 74 устройства сигнал REQUEST. При этомтриггеры 10 и 11 сбрасываются в нуль, закрывая для чтения буферный регистр 6 и снимая с выхода 75 устройства сигнал ACKNO. На этом цикле передачи первого байта команда завершается.

Через некоторое время (530 не) после сброса сигнала ACKNO ПФУ готово принять следующий байт команды. Оно вновь выставляет на вход 74 устройства сигнал RETJUE T и цикл приема очередного байта команды повторяется. После приема последнего байта команды ПФУ снимает сигнал С/Д со входа 77 устройства и устройство переходит в фазу выполнения команды.

В этом режиме, если команда предусматривает обмен flaHj MH cjwcTjWHjpju iuM- ной, ПФУ сигналом 1/0(INPUT/OTTPUT)Ha входе 78 устройства определяет направление обмена. При этом, если передача осуществляется от ПФУ к системной шине, то сигнал 1 /0 принимает нулевое значение, если от системной шины к ПФУ, то единичное.

Рассмотрим работу устройства сопряжения в фазе обмена данными в режиме прямого доступа к памяти, когда единица записана в первый разряд регистра маски 4 (см. временные диаграммы на фиг.5).

В этом режиме обмен начинается с ус- тановкиЛФУ на входе 74 устройства сигнала REQUEST. Этот сигнал, пройдя через инвертор 58, установит триггер запроса 12 в единичное значение. Сигнал запроса с выхода триггера 12 проходит через открытый элемент И 17 и поступает на выход устройства 70 а виде сигнала DRQ.

Получив сигнал DRQ, контроллер ДМА отвечает разрешением ПДП - сигналом ЬДСК. Затем в зависимости от направления

передачи данных контроллер ДМД выставляет сигнал ЮРГлибо сигнал IOW

Сигнал DACK, пройдя через элемент ИЛИ-НЕ 42, инвертируется и открывает элементы И 26 и 1/1 27. С выхода элемента ИЛИ-НЕ 42 сигнал DACK поступает на вход элемента ИЛИ-НЕ 39 и разрешает работу шинного формирователя 1. Если передача данных производится от системной шины к ПФУ, то сигнал IOW с входа 65 устройства инвертируется открытым элементом И 26 и, пройдя элемент задержки 55, элемент ИЛИ 45, разрешает запись информации в буферный регистр 6, а пройдя еще елемент 46, разрешает считывание информации с этого регистра и устанавливает триггер 11 в единичное состояние, на входе 75 выставляется сигнал ACKNO. Единичный сигнал с выхода элемента ИЛИ 46 через элемент И 28 сбрасывает триггер запроса 12. ПФУ считывает информацию выставленную на инфог;мауионных входах 59 и снимает сигнал REQUEST, что приводит к сбросу триггеров 10 и 11. Цикл передачи байта информации на этом завершается и ПФУ го- товится к приему следующего байта. При передаче информации от ПФУ в системную шину возбуждается вход 64 устройства сигналом fOR. Нулевое значение этого сигнала, поступив на Т-вход шинного форми- рователя 1, настраивает его на передачу информации от входов В к А. Одновременно, пройдя через открытый элемент И 27, сигнал 10R через элемент ИЛИ 48 поступит на управляющий DE-вход шинного форми- рователя 2 разрешит передачу информации с информационных входов ДВ 61 на входДУ 59 устройства. В то же время сигнал с выхода элемента ИЛИ 48 пройдет на вход элемента ИЛИ 46 и установит триггер 11 в единицу, создавая на выходе 75 устройства активный сигнал ACKNO подтверждения, через элемент И 38 сбросит триггер запроса 12 в нуль, снимет тем самым с выхода 70 устройства сигнал DRQ запроса к контрол- леру ДМА. Получив сигналы ACKNO, ПФУ передает через устройство байт данных и через некоторое время (450 не) снимает с входа 74 устройства сигнал REQUEST. Это приведет к сбросу триггеров 11 и 12. На этом цикл обмена байтом информации между ПФУ и системной шиной завершается.

Через некоторое время (при записи информации в ПФУ - 700/550 не, при считы- вании информации с ПФУ - 450/7&0 не) ПФУ готово к обмену следующим байтом информации и оно вновь выставляет на вход 74 устройства сигнал REQUEST запроса на обмен и цикл обмена повторяется.

После передачи и приема всех данных ПФУ завершает обмен данными передачей в системную шину байта состояния завершения команды, При этом ПФУ выставляет на входы 76, 77 и 78 системные сигналы MESSAGE, C/D и 1/0 и на входе 74 устройства - сигнал REQUEST. Байт состояния ПФУ считывается устройством в том же режиме, в котором велся обмен данными для этого. По завершении передачи байта состояния ПФУ в режиме ПДП элемент И-И Л И 16 снимает со своего выхода единичный сигнал и на выходе элемента И-НЕ 32 появляется фронт положительного сигнала, который установит триггер 7 в единичное состояние, создавая на выходе 69 сигнал IRQ запроса программного прерывания к системному модулю ЭВМ, извещая его о завершении операции ввода-вывода. Завершенные операции в режиме ПДП может быть проведено по инициативе контроллера DMA подачей на вход 68 устройства сигнала Т/С передачи последнего байта. В этом случае триггер 7 также вырабатывает запрос программного прерывания И, наконец, окончание операции может быть выполнено в любом режиме передачи данных по инициативе ПФУ снятием сигнала BUSY с входа 73 устройства что также приведет к установке триггера 7 в единичное значение.

При получении запроса программного прерывания IRQ с выхода 69 устройства главный процессор всегда считывает байт состояния устройства путем подачи команды INAL, 321 Н. При завершении операции по этой команде сигналом T&2T5TATUS триггер 7 сбрасывается в нуль С входов и выходов устройства снимаются все активные сигналы и оно переходит в фазу BUSFREE свободной шины.

Формула изобретения Устройство для сопряжения магистрали ЭВМ с периферийными устройствами, включающее первый-третий шинные формирователи, первый регистр, первый триггер, два дешифратора, счетчик, элемент И-ИЛИ, шесть элементов И. два инвертора, причем первая группа информационных входов-выходов первого шинного формирователя является группой входов-выходов устройства для подключения к шине данных ЭВМ, вторая группа информационных входов-выходов подключена к группе информационных выходов второго шинного формирователя, информационные входы которого являются входами устройства для подключения к шине данных периферийных устройств, выходы первого