Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации контроллеров связи в мультимикропро- цессорных системах абонентских пунктов и терминальных комплексов, а также устройств управления рабочими местами пользователей автоматизированных систем управления.

Целью изобретения является .расширение функциональных возможностей устройства за счет увеличения номенклатуры подключаемых внешних устройств,

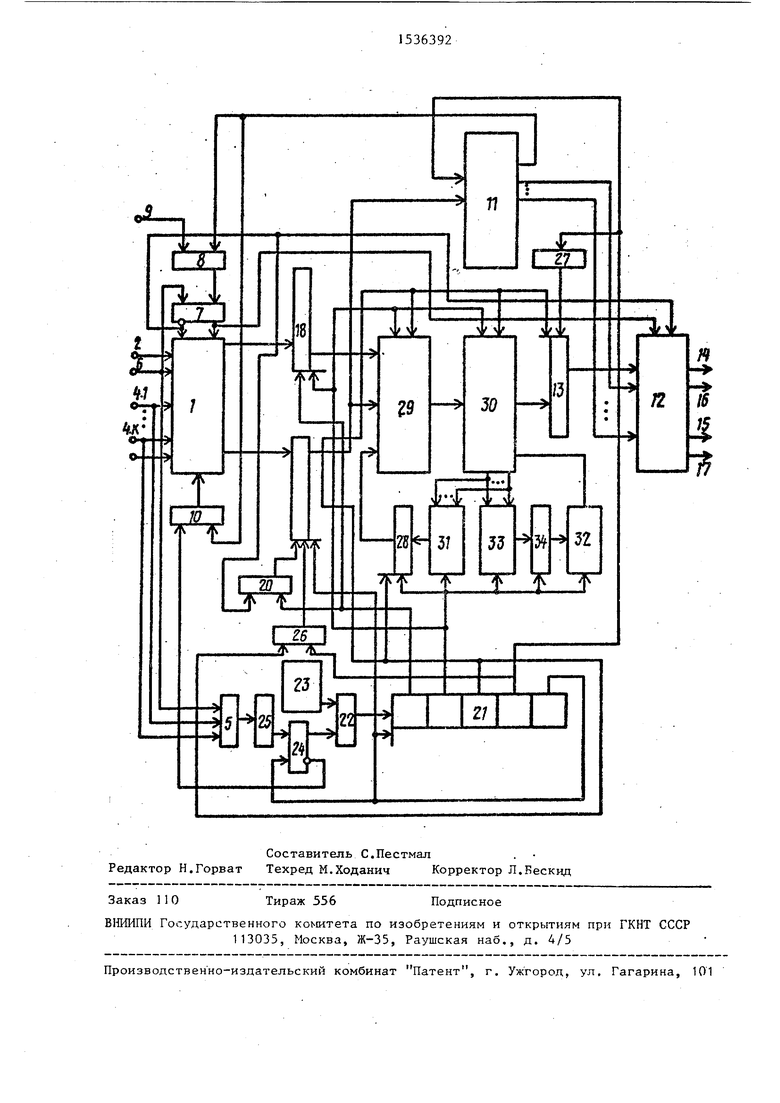

На чертеже представлена структурная схема устройства.

Устройство содержит первый коммутатор 1, группу информационных входов 2, группу информационных входов 3, группу вхрдов обращения 4, первый элемент ИЛИ 5, вход 6 обращения, триггер 7 коммутации, второй. элемент ИЛИ 8, установочный вход 9, второй элемент И 10, блок 11 микропрограммного управления, второй коммутатор 12, втор9й регистр 13, группу выходов 14-17, третий регистр 18, первый регистр 19, первый элемент И 20, сдвиговый регистр 21, третий элемент И 22, -генератор 23 импульсов, триггер 24 управления, второй одно- вибратор 25, третий элемент ИЛИ 26, первый однозибратор 27, четвертый регистр 28, третий коммутатор 29, блок 30 памяти, дешифраторы 31, 32,. шифратор 33, пятый регистр 34, в качестве блока 30 памяти используется ассоциативный накопитель.

сл со

со со

1C

Устройство работает в двух основных режимах, предусматривающих соответственно обслуживание обращения от процессора ЭВМ к внешнему устройству (ВУ) Н-го типа (1 режим) и обращения от ВУ к процессору (II режим), В случае совпадения во времени поступления запросов по I и II режимам устройство обрабатывает запрос по I режиму.

Работа устройства начинается с начальной установки. Сигнал по входу 9 устройства через элемент ИЛИ 8 устанавливает триггер 7 коммутации в единичное состояние, переключая тем самым коммутаторы 1,12 в режим-II (т.е. подключает к коммутатору 1 управляющую шину ВУ по входам 4 устройства и информационную шину ВУ по входам 3 устройства,, а к коммутатору 12 - управляющую шину ЭВМ по выходам 15 устройства и входную информационную шину ЭВМ по выходам 17 устройства).

Рассмотрим режим II работ устройства. По входам 3 поступает и устанавливается на второй группе информационных выходов коммутатора 1 код символа из алфавита Н-го ВУ. По одному из входов 4 Н поступает сигнал обращения Н-го ВУ. Единица на втором управляющем входе коммутатора 1 блокирует установку информации на его первой группе выходов. Сигнал с Н-го входа 4.Н через элемент ИЛИ 5 и одновибратор 25 устанавливает в 1 триггер 24 управления, тем самым подключая к схеме через элемент И 22 генератор 23 импульсов, и на синхровход сдвигового регистра 21 поступает тактовый сигнал. Первый разряд регистра 21 , имевшего в начале работы устройства состояние 000...О, устанавливается в 1. Установка в 1 триггера 24 приводит к сжатию через элемент И 10 разрешающего сигнала на третьем управляющем входе коммутатора 1, тем самым блокируется коммутация на выходы коммутатора 1 какой бы то ни было информации с его входов. На первом входе элемента И 10 сохраняется единичный потенциал с выхода блока 11 микропрограммного управления, который формирует этот сигнал, находясь в неактивном состоянии.

Сигнал с единичного выхода первого разряда регистра 21 поступает на

0

5

0

5

0

5

0

5

0

5

вход записи регистра 18, разрешая1 прием кода со второй группы информационных выходов коммутатора 1. Этот сигнал поступает также на второй вход элемента И 20, однако единичный сигнал на выходе этого элемента, разрешающий прием кода на регистр 19 с первой группой информационных выходов коммутатора 1, не формируется из-за отсутствия в данном режиме работы устройства на первом входе элемента И 20 (триггер 7 установлен в 1).

По окончании описанных действий на синхровход регистра 21 поступает следующий управляющий сигнал с генератора 23, в результате чего происходит сдвиг его содержимого на 1 разряд вправо и в 1 устанавливается второй разряд регистра 21. Содержимое регистра 21 дополняется слева нулями.

Управляющий потенциал с единичного выхода второго разряда регистра 21 поступает на вход чтения регистра 18, в результате чего код с этого регистра 18 подается на первую группу информационных входов коммутатора 29. Одновременно этот потенциал подается как на первый управляющий вход коммутатора 29, разрешая коммутацию кода с регистра 18 на информационные входы блока 30, так и на вход записи блока 30, определяя операцию записи в блок 30 по признаку, В то же время единичный сигнал со второго разряда регистра 21 блокирует работу шифратора 33, регистра 34 и дешифратора 32, являясь при этом разрешающим работу сигналом, поступающим на управляющий вход дешифратора 31 и вход записи регистра 28 (разрешение приема кода). При отсутствии разрешающего сигнала работа дешифратора 31 и регистра 28 блокируется.

Логически ассоциативный накопитель (блок памяти) 30 разбит на К+1 зон равной длины, в ячейках которых, начиная со второй, сгруппированы символы алфавитов ЭВМ и К ВУ. В первой ячейке каждой зоны записан адрес соответствующего ВУ (или ЭВМ в зоне ЭВМ). Между символами в ячейках зон ЭВМ и ВУ имеется однозначное позиционное соответствие, т.е. соответствующие друг другу символы в алфавитах ЭВМ и ВУ записаны в ячейках, занимающих одинаковые позиции относительно границ своих.зон.

При выполнении операции запись в память(управляющий сигнал на входе записи- блока 30) запись может производиться в ячейку блока по совпадению информации в ячейке и признака, поступающего по информацией- ным входам блока 30. При выполнении операции чтение из памяти (управляющий сигнал на входе чтения блока 30) обращение происходит к одной из зон блока, выбор которой опреде- ляется совпадением признака, поступающего по информационным входам блока, и информации в первой ячейке Н-й зоны блока 30. Считываемая из Н-й зоны Н-я. ячейка определяется по-

ложением единичного разряда регистра маски (в данном случае регистра 28), код с выходов которого поступает в случае операции чтения одновременно с кодом признака на информационные входы блока 30. Число разрядов регистра маски .(регистра 28) равно числу ячеек любой из зон блока 30.

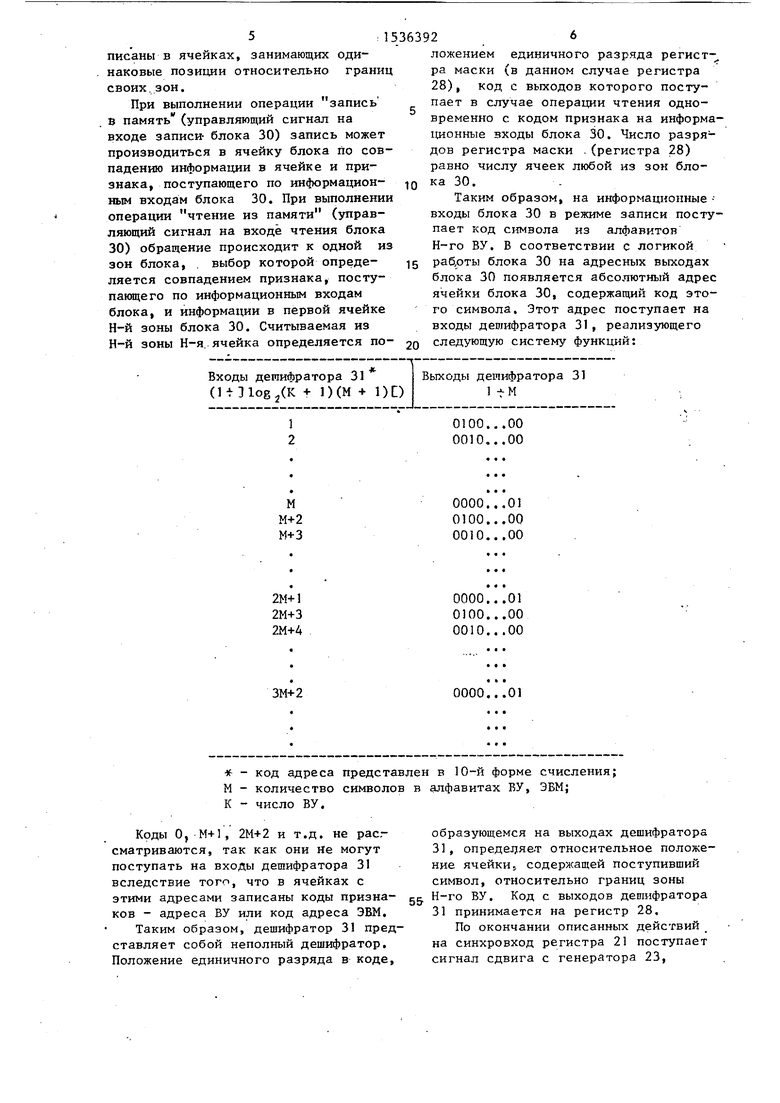

Таким образом, на информационные ; входы блока 30 в режиме записи поступает код символа из алфавитов Н-го ВУ. В соответствии с логикой раб,оты блока 30 на адресных выходах блока 30 появляется абсолютный адрес ячейки блока 30, содержащий код этого символа. Этот адрес поступает на входы девшфратора 31, реализующего следующую систему функций:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1403069A1 |

| Устройство для лексического анализа метамикроассемблера | 1982 |

|

SU1034043A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для лексического анализа метатранслятора | 1983 |

|

SU1153329A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1989 |

|

SU1755286A2 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации контроллеров связи в мультипроцессорных системах, абонентских пунктов и терминальных комплексов, а также устройств управления рабочими местами пользователей автоматизированных систем управления. Целью изобретения является расширение функциональных возможностей за счет увеличения номенклатур подключаемых внешних устройств. Устройство содержит блок микропрограммного управления, блок памяти, три коммутатора, пять регистров, сдвиговый регистр, триггер управления, триггер коммутации, генератор импульсов, два одновибратора, три элемента ИЛИ, три элемента И. 1 ил.

Входы дешифратора 31 (ltDlog2(K + 1)(М + 1)D

1 2

м

М+2 м+3

2М+1 2М+3 2М+4

ЗМ+2

- код адреса представлен в 10-й форме счисления; М - количество символов в алфавитах ВУ, ЭВМ; К - число ВУ.

Коды О, М+1, 2М+2 и т.д. не рассматриваются, так как они Не могут поступать на входы дешифратора 31 вследствие тог, что в ячейках с этими адресами записаны коды признаков - адреса ВУ или код адреса ЭВМ.

Таким образом, дешифратор 31 представляет собой неполный дешифратор. Положение единичного разряда в коде,

Выходы дешифратора 31 1 tM

0000...01 0100...00 0010...00

0000...01 0100...00 0010...00

0000...01

образующемся на выходах дешифратора 31, определяе-т относительное положение ячейки5 содержащей поступивший символ, относительно границ зоны Н-го ВУ. Код с выходов дешифратора 31 принимается на регистр 28.

По окончании описанных действий на синхровход регистра 21 поступает сигнал сдвига с генератора 23,

в результате чего происходит сдвиг его содержимого еще на один разряд .вправо и в 1 устанавливается третий разряд регистра 21.

В результате на второй управляющий вход коммутатора 29 поступает сигнал, определяющий коммутацию на информационные входы блока 30 информционных выходов регистра 19и регистра 28. Управляющий сигнал поступает также на вход чтения блока 30, определяя тем самым выполнение операции чтения по признаку. На вход записи регистра 13 поступает сигнал, разрешающий прием кода на этот регистр Ла вход чтения регистра 28 и на вход чтения регистра 19 (через элемент ИЛИ 26) поступают управляющие сигналы выдать код. В результате коды с регистра 19 и регистра 28 через коммутатор 29 подаются на информационные входы блока 30.

В первой ячейке зоны.ЭВМ в блок 30 записан код 000.. Д)0, являющийс таким образом признаком зоны ЭВМ, Следовательно, под воздействием описанных управляющих сигналов и поступивших на соответствующие входы блока 30 кодов на адресных выходах блока 30 появляется адрес ячейки блока, содержащей тот символ из алфавита,который соответствует поступившему на входы устройства в данном сеансе его работы символу из алфавита Н-го ВУ.

Вследствие отсутствия блокирующего сигнала на управляющих входах шифратора 33, регистра 34 и дешифратора 32 этот адрес по данной де- почке элементов поступает уже в дешифрованном виде на адресные входы блока 30, в результате чего на первые информационные выходы блока 30 поступает код символа из алфавит ЭВМ, соответствующий коду поступившего символа из алфавита Н-го ВУ, и принимается на регистр 13,

Далее на синхровход регистра 21 поступает следующий тактовый сигнал с генератора 23, и в 1 устанавливается четвертый разряд этого регистра, В результате на вход чтения регистра 19 поступает сигнал выдать код, на разрешающий ьход бло ка 11 микропрограммного управлении поступает сигнал, разрепающий работу блока, и на вход одковибратор 27 также поступает единичный сигнао

0

5

0

5

0

5

0

5

0

5

На управляющие входы коммутатора 29 в данном такте никакие сигналы не поступают, т.е. его работа блокируется и код с выходов регистра 19 поступает только на входы блока 11,

Блок 11 представляет собой блок микропрограммного управления. Код, поступающий в данном такте работы устройства на группу входов логического условия блока 11, представляет собой адрес перяой микрокоманды микропрограммы обращения к ЭВМ (в режиме II) или в ВУ 11-го типа (в режиме I). Поступление кода (в том числе и кода 000,4.00) одновременно с разрешающим сигналом на его разрешающем входе инициирует работу блока

11,и он вырабатывает последовательность управляющих кодов, которая через коммутатор 12 поступает на управляющую шину ЭВМ через выходы 15 устройства. Одновременно с первой микрокомандой реализации диалога ВУ-ЭВМ на информационную шину ЭВМ через выходы 17 устройства поступает код символа в алфавите ЭВМ, соответствующий символу, поступившему от Н-го ВУ. Это происходит в результате прохождения управляющего сигнала через одновибратор 27 на вход чтения регистра 13, что определяет выдачу кода с этого регистра на вторую группу входов коммутатора

По выполнении описанных операций на синхровход регистра 21 поступает тактовый сигнал с генератора 23, и пятый разряд регистра 21 устанавливается в 1, Сигнал с выхода этого разряда поступает на установочный вход регистра 21, устанавливая его в состояние 000.,.00, на управляющий вход регистра 19, устанавливая его в состоянии 000...00, и на нулевой вход триггера 24 управления, устанавливая его в О. Сигнал с нулевого выхода триггера 24 поступает на второй вход элемента И 10, на выходе которого, появляется единичный сигнал, разрешающий работу коммутатора 1. Устройство закончило сеанс обмен.: и готово к обслуживанию следующего запроса

Рассмотрим режим 1 работы устройства. В этом случае устройство работает аналогично режиму И с той разницей, что по входу обращения 6 поступает сигнал обращения от ЭВМ. Тем самым триггер 7 устанавливается из состояния 1, в которое он был установлен по окончании последнего сеанса работы устройства, в состояни О, переключая ко:гмутатор 1 и коммутатор 12 в режим 1 т.е. подключае к коммутатору 1 информационную шину ЭВМ по входам 2 устройства, а к коммтатору 12 - шину управления по выходам 14 устройства, информационную тину ВУ по выходам 16 устройства).

Если все запросы по входам 6 и 4 совпадают, то сигнал по входу 6 принудительно устанавливает триггер 7 в О, обеспечивая тем самым приоритетное обслуживание ЭВМ,

По входам 2 поступает и устанавливается на второй группе информационных выходов коммутатора 1 код символа из алфавита ЭВМ, на первой группе выходов коммутатора 1 - адрес ВУ, к которому обращается ЭВМ (так как запрещающий сигнал ла втором управляющем входе коммутатора 1 отсутствует) . В дальнейшем устройство работает аналогично режиму II, однако на регистр 19 принимается код адреса ВУ, так как через элемент И 20, на входы которого подаются единичные сигналы с единичного выхода триггера 7 и выхода первого разряда регистра 21, на входе записи регистра 19 формируется сигнал принять код.

В результате работы устройства в режиме 1 на группе информационных выходов устройства формируется символ в алфавите ВУ, к которому обращается ЭВМ, а на группе управляющих выходов устройства - последовательность микрокоманд, реализующих диалог ЭВМ - ВУ. По окончании диалога устройство аналогично режиму II заканчивает свою работу и готово к обслуживанию следующего запроса.

Формула изобретения

Устройство для сопряжения ЭВМ с внешними устройствами, содержащее блок микропрограммного управления, два коммутатора, два регистра, сдвиговый регистр, генератор импульсов, первый элемент ИЛИ, причем первая

0

5

Q

группа информационных входов первого и первая группа информационных выходов второго коммутаторов образуют группы входов И выходов устройства для подключения соответственно к группам информационных выходов и входов ЭВМ, вторая группа информационных входов первого и вторая группа информационных выходов второго коммутаторов образуют группы входов и выходов устройства для подключения соответственно к информационным выходам и информационным

5 входам внешних устройств, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения номенклатуры подключаемых внешних устройств, в устройство введены три регистра, триггер коммутации, триггер управления, третий коммутатор, блок памяти, два дешифратора, шифратор, два одно- вибратора, три элемента И, два элемента ИЛИ, причем третья группа информационных входов первого коммутатора соединена с группой входов первого элемента ИЛИ и образует группу входов устройства для подключения к выходам обращения внешних устройств( информационный вход первого коммутатора соединен с нулевым входом триггера коммутации, с входом первого элемента ИЛИ и является входом уст5 ройства для подключения к выходу об- ращ,„ния ЭВМ, первый вход второго элемента ИЛИ является входом устройства для подключения к установочному выходу ЭВМ, третья и четвертая группы

0 информационных выходов второго коммутатора образуют группу выходов устройства для подключения соответственно к группам управляющих входов ЭВМ и внешних устройств, при этом нулевой

5 выход триггера коммутации соединен с первыми управляющими входами первого, второго коммутаторов и с первыми входами первого элемента И, выход которого соединен с входом записи первого регистра, группа информационных входов которого соединена с первой группой информационных выходов первого коммутатора, второй управляющий вход которого соединен с вторым управляющим входом второго коммутатора и с единичным выходом триггера коммутации, единичный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого

0

0

5

11

соединен с первым входом второго элемента И и с выходом блока микропрограммного управления, группа выходов которого соединена с первой группой информационных входов второго коммутатора, вторая группа информационных входов которого соединена с группой информационных выходов второго регистра, группа информационных входов которого соединена с первой группой информационных выходов блока памяти, группа информационных входов которого соединена с группой информационных выходов третьего коммутатора, первая группа информационных входов которого соединена с группой информационных выходов третьего регистра, группа информационных входов которого соединена с второй группой информационных выходов первого коммутатора, третий управляющий вход которого соединен с выходом второго элемента И, второй вход которого соединен с нулевым выходом триггера управления, единичный выход которого соединен с первым входом третьего элемента И, выход которого соединен с синхро- входом сдвигового регистра, выход первого разряда которого соединен с вторым входом первого элемента И и с входом записи третьего регистра, вход чтения которого соединен с входом записи блока памяти, с первым |управляющим входом третьего коммутатора, с входом записи четвертого

1

регистра, с разрешающим входом пятого регистра, с управляющими входами шифратора, первого и второго дешифраторов и с выходом второго разряда сдвигового регистра, выход третьего разряда которого соединен с первым входом третьего элемента ИЛИ, с входом чтения четвертого регистра, с вторым управляющим входом третьего коммутатора,с входом чтения бло536392 . 12

ка памяти и с входом записи второго регистра, вход чтения которого соединен с выходом первого одновибра- тора; вход запуска которого соединен с разрешающим входом блока микропрограммного управления, с вторым входом третьего элемента ИЛИ и с выходом четвертого разряда сдвиЮ гового регистра, выход пятого разряда которого соединен с нулевым : входом триггера управления, с установочным входом сдвигового регистра и с установочным входом первого ре15 гистра, группа информационных выходов которого соединена с группой входов логического блока микропрограммного управления и с второй группой информационных. входов тре20 тьего коммутатора, третья группа информационных входов которого соединена с группой информационных выходов четвертого регистра, группа информационных входов которого сое25 динена с группой выходов первого дешифратора, группа информационных входов которого соединена с второй группой информационных выходов блока памяти и с группой информационных

30 входов шифратора, группа выходов которого соединена с группой информационных входов пятого регистра, группа информационных выходов которого соединена с группой информа-- ционных входов второго дешифратора, группа выходов которого соединена с группой адресных входов блока памяти, вход чтения первого регистра соединен с выходом третьего Элемента

40 ИЛИ, выход генератора импульсов соединен с.вторым входом третьего элемента И, выход первого элемента ИЛИ соединен с входом запуска второго одновибратора, выход которого .

45 соединен с единичным входом триггера управления.

35

Я

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C ВидЕОТЕРМиНАлОМ | 1979 |

|

SU840872A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1144113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-05—Подача