4

О

СП

о ел

Изобретение относится к вычислительной технике и может быть использовано в приставках к универсальным ЭЦВМ для получения случайных чисел, подчиняющихся законам распределения Пирсона.

Цель изобретения - расширение области применения за счет формирования случайных чисел, подчиняющихся законам распределения Пирсона.

На чертеже показана структурная схема генератора случайных чисел.

Генератор содержит датчик 1 равномерно распределенных случайных чисел j блок 2 сложения и вычитания, блок 3 умножения, блок 4 памяти,блок 5 управления, группы 6-8 элементов ИЛИэ элементы ИЛИ 9-11, элемент 12 задержки, регистры 13 и, 14.

Блок 5 управления содержит элемент ИЛИ 15, счетчик 16, дешифратор 17, элементы ИЛИ 18-27, элементы И 28-30, элемент ИЛИ 31, элемент 32-35 задержки, элемент НЕ 36, элемент ИЛИ 37, триггеры 38-40.

Генератор работает следующим об- разоМо

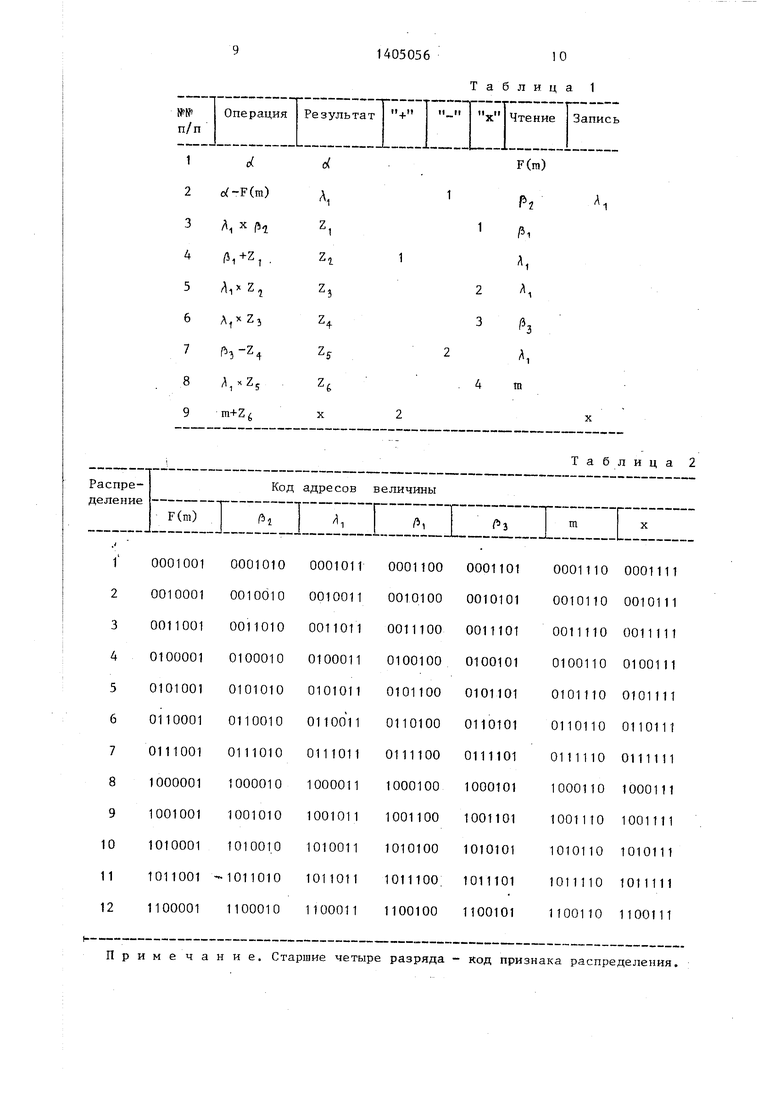

Последовательность выполнения операций приведена в табл. 1 ,

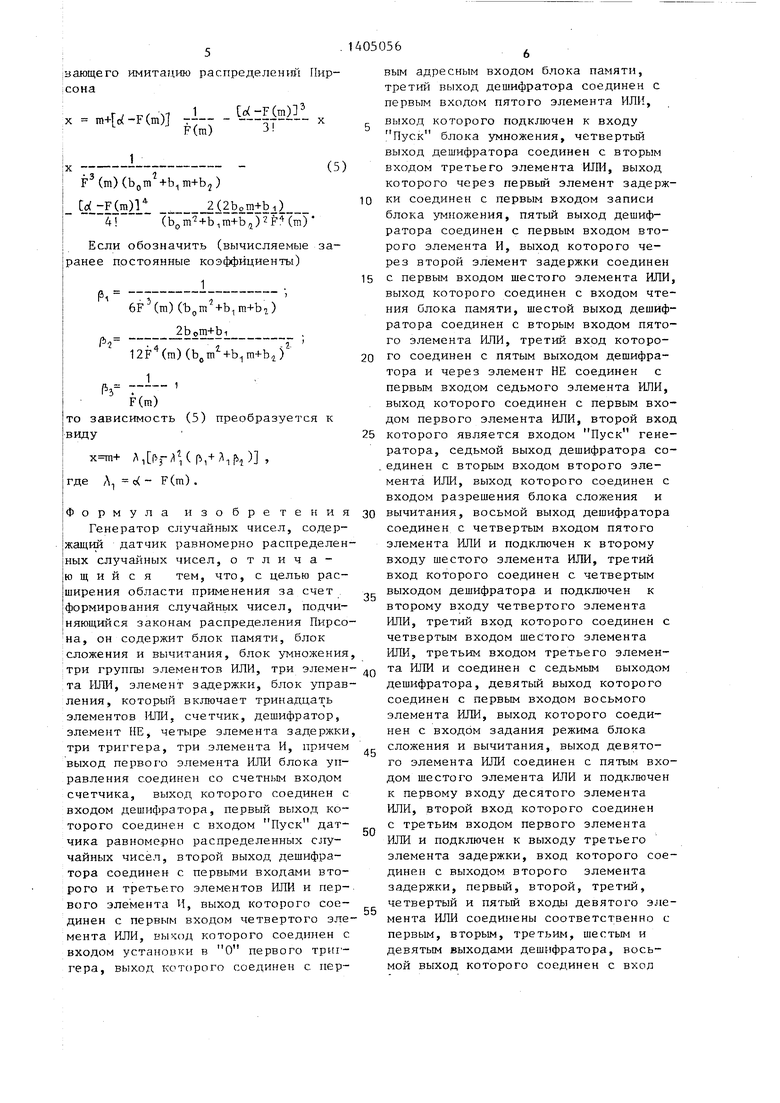

В регистр 13 записывается код признака закона распределения (коды адре сов величин даны в табл. 2), и по сигналу, поступающему на вход Пуск 1 енератора начинается его работа. Ко признака закона распределения и код, определяемый состоянием триггеров 38-40, определяет адрес той или иной величины, хранящейся в блоке 4 памяти.

Под воздействием сигнала запуска в счетчике 16 устанавливается код 0001, на первом выходе дешифратора 17 появляется сигнал, который запускает датчик 15 а также устанавливает триггеры 38-40 в состояние 001. Сигнал с первого выхода дешифратора, кроме того, проходит через элементы ИЛИ 18 и 22 на блок 4 памяти и запускает его на считывание величины F (га) для распределения, например, 1. Величина F (т) из блока 4 заносится в блок 2 под действием сигнала с первого выхода, поступающего на блок 2 через элемент 32 задержки и элемент ИЛИ.

Работа датчика 1 завершается появлением cjjy4ai iHoro числа о на его информационном выходе. Число cf зано0

5

0

5

0

5

0

0 5

сится в блок 2. Сигнал с выхода окончания формирования чисел датчика 1 устанавливает также в счетчике 16 код 0002. На втором выходе дешифратора 17 появляется сигнал, который запускает блок 2 через элемент ИЛИ 25 на выполнение вычитания.

Одновременно по этому сигналу триггеры 38-40 устанавливаются в состояние 002, из блока 4 считывается /Ь2 и заносится в блок 3.

После выполнения вычитания на выходе окончания вычитания А заносится в блок 3. Сигналом с элементов И.28 и ИЛИ 21 триггеры 38-40 устанавливаются в состояние 003, сигналом с элемента 33 задержки запускается блок 4 памяти и в него записывается также результат вычитания / .

Сигнал с выхода окончания сложения и вычитания блока 2 устанавливает в счетчике 16 код 0003. Под действием сигнала с третьего выхода запускается блок 3, триггеры 38-40 устанавливаются в состояние 004, из блока 4 считывается /5 и заносится в блок 2.

Результат умножения Z, по сигналу с выхода окончания умножения блока 3 заносится в блок 2. Теперь сигнал появляется на четвертом выходе дешифратора 17 и запускает блок 2 на выполнение операции сложения через элемент ИЛИ 31. Одновременно триггеры 38-40 устанавливаются в состояние 003, из блока 4 памяти считывается /, и заносится в блок 3.

После операций блоком 2 результат Z под действием сигнала с выхода окончания сложения и вычитания блока 2 заносится в блок 3. В счетчике 16 фиксируется код 0005. Сигнал с пятого выхода дешифратора 17 пускает блок 3.

Результат умножения Z-i, заносится вновь в блок 3 под действием сигнала с выхода элемента И 29. С элемента 35 задержки сигнал проходит через элемент ИЛИ 22 на блок 4 и запускает его на чтение. Считанное заносится в блок 3. Сигнал с элемента 32 задержки устанавливает триггеры 38-40 в состояние 004, а в счетчике 1 6 - код 0006 (так как на пятом выходе дешифрато.ра 17 и -1еется сигнал, то на выходе элемента НЕ 36 - низкий уровень и он закрывает элемент ИЛИ 37).

Сигнал с шестого выхода дешифратора 17 запускает блок 3, а также устанавливает триггеры 38-40 в состояние 005. Из блока 4 считывается я И заносится в блок 2.

После умножения Z заносится в блок 2. В счетчике 16 устанавливается код 0007..Сигнал с седьмого выхода запускает блок 2. Одновременно триггеры 38-40 устанавливаются в состояние 003, из блока 4 считывается Д и заносится в блок 3.

Результат вычитания Zj фиксируется в блоке 3. Сигнал с выхода окочания сложения и вычитания блока 2 вызывает сигнал на восьмом выходе дешифратора 17, который запускает Влок 3, триггеры 38-40 устанавливаются в состояние 006, из блока 4 считывается m и заносится в блок 2.

После умножения Z заносится также в блок 2,

Сигнал с девятого выхода дешифратора 17 запускает блок 2 на выполнение операции сложения. Триггеры 38-40 устанавливаются в состояние 007. Результат операции сложения х заносится в блок 4 памяти. На десятом выходе дешифратора 17 появляется сигнал, который записьюает сформированное число в регистр 14, выхо которого является выходом генератора.

Сущность изобретения состоит в следующем.

Известно, что уравнение

-ьГх-б; Ь: «.

где Ь- (, 1,2)- параметры

m - мода распределения, является уравнением Пирсона.

Зависимости, определяющие связь -между b . и параметрами аппроксимирующего распределения, имеют вид , 1 , S+2

Ьо - si2; - -Г S-2

Ь - А 1 Ь, - - 6 --где S iiill irlA. 3.1-2р,+6

центральные моменты k-ro

порядка.

На практике при аппроксимации эмпирических распределений вычисляют

первые четыре момента и, используя выражения (2), определяют оценки параметров уравнений Пирсона. С помощью рядов вида

, .)1,. .

л)гоVI1Хр

И соотношений

10

15

(3)

и т.д. может быть разработан алгоритм, позволяющий преодолеть трудности прямого моделирования распределе- НИИ, аппроксимированных кривыми Пирсона. Так как распределения заданы дифференциальным уравнением (1), причем граничные условия F (-ос) О, F (СИ ) 1, то из формул (3) и систе

F (Xm) о, .)

(х), F (х), о

35

следует, что

D X

40

D X

X,

О,

D3

1 Li5«l

45

50

и т.д.

Выбирая в качестве опорной точки Хр т, можно получить

F (х ) Й ГI2IS (х)

о- dx L Ьох2+Ь,х+Ц

F (хо),

1

box|+b,

v4 ( -7v rv )2Ьо.

55 F (x,)-2F ( - (,x,-eb)2

(4)

Тем самым определяется структура моделирующего алгоритма, обеспечивающего имитацию распределений Пирсона

X (-F(m)j 7

1 W-F(m)F(m)

3

F CmXbomVb m+b)

(5)

(m)T 2(2bom+b i)

4 (bpm +bim+b,2)2FMm)

Если обозначить (вычисляемые заранее постоянные коэффициенты)

1 Р о,

Р

6F (т)()

2bom+bi

12F (m)() 1

fi --- 1

F(m)

то зависимость (5) преобразуется к виду

() где Л о( - F(m) .

Формула изобретения i Генератор случайных чисел, содер- |жа1ций датчик равномерно распределен ных случайных чисел, о т л и ч а - ю щ и и с я тем, что, с целью расширения области применения за счет формирования случайных чисел, подчи- 1няющийся законам распределения Пирсо на, он содержит блок памяти, блок сложения и вычитания, блок умножения три группы элементов ИЛИ, три элемента РШИ, элемент задержки, блок управления, который включает тринадцать элементов 1ПИ, счетчик, дешифратор, элемент НЕ, четыре элемента задержки три триггера, три элемента И, причем выход первого элемента ИЛИ блока управления соединен со счетным входом счетчика, выход которого соединен с входом деши4 ратора, первый выход которого соединен с входом Пуск датчика равномерно распределенных случайных чисел, второй выход дешифратора соединен с первыми входами второго и третьего элементов ИЛИ и первого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, выкод которого соединен с входом установки в О первого триггера, выход которого соединен с первым адресным входом блока памяти, третий выход дешифратора соединен с первым входом пятого элемента ИЛИ,

выход которого пoдкJroчeн к входу Пуск блока зл ножения, четвертый выход дешифратора соединен с вторым входом третьего элемента ИТШ, выход которого через первый элемент задержки соединен с первым входом записи блока умножения, пятый выход дешифратора соединен с первым входом второго элемента И, выход которого через второй элемент задержки соединен

с первым входом шестого элемента ИЛИ, выход которого соединен с входом чтения блока памяти, шестой выход дешифратора соединен с вторым входом пятого элемента ИЛИ, третий вход которого соединен с пятым выходом дешифратора и через элемент НЕ соединен с первым входом седьмого элемента ИЛИ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход

которого является входом Пуск генератора, седьмой выход дешифратора со- .единен с вторым входом второго элемента ИЛИ, выход которого соединен с входом разрешения блока сложения и

вычитания, восьмой выход дешифратора соединен с четвертым входом пятого элемента ИЛИ и подключен к второму входу шестого элемента ИЛИ, третий вход которого соединен с четвертым выходом дешифратора и подключен к второму входу четвертого элемента ИЛИ, третий вход которого соединен с четвертым входом шестого элемента ИЛИ, третьим входом третьего элемента ИЛИ и соединен с седьмым выходом дешифратора, девятый выход которого соединен с первым входом восьмого элемента ИЛИ, выход которого соединен с входом задания режима блока сложения и вычитания, выход девятого элемента ИЛИ соединен с пятым входом шестого элемента ИЛИ и подключен к первому входу десятого элемента ИЛИ, второй вход которого соединен с третьим входом первого элемента ИЛИ и подключен к выходу третьего элемента задержки, вход которого соединен с выходом второго элемента задержки, первый, второй, третий, четвертый и пятый входы девятого элемента ИЛИ соединены соответственно с первым, вторым, третьим, шестым и девятым выходами дешифратора, восьмой выход которого соединен с вхол

/

установки в 1 первого входом установки в О второго

и ,11

1405056

триггера и элементов

триг- которо го

гера, вход установки в соединен с первым входом одиннадцатого элемента ИЛИ, выход которого соединен со счетньи«1 иходом триггера, выход которого с вторым адресным входом блока памяти, третий адресный вход которого соединен с прямым.выходом второго триггера,счетный вход которого соединен с выходом десятого элемента ИЛИ, выход четвертого элемента задержки соединен с первым входом двенадцатого элемента ИЛИ, выход которого соединен с входом записи блока памяти, второй вход двенадцатого элемента ИЛИ соединен с

выходом третьего элемента И, первьй

вход которого соединен с девятым выходом дешифратора, второй вход третьего элемента И соединен с вторым входом первого элемента И, четвертым ходом первого элемента ИЛИ и выходом окончания сложения и вычитания блока сложения и вычитания, пятый ход первого элемента ИЛИ соединен

с выходом окончания формирования чисел датчика равномерно распределенных случайных чисел, второй вход второго элемента И соединен с вторым входом седьмого элемента ИЛИ и подключен к выходу окончания умножения блока умножения, первый выход дешифратора соединен с первым входом тринадцатого элемента ИЛИ, выход которого соеинен с первым входом записи блока сложения и вычитания, второй вход тринадцатого элемента ИЛИ соединен с выходом конца операции блока умноения, второй вход восьмого элемента ИЛИ соединен с четвертым входом дешифратора, информационные разрядные ыходы датчика равномерно распредеенных случайных чисел соединены с

первыми выходами соответствующих элеентов ИЛИ первой группы, вторые вхоы элементов И.Г1И первой группы соеинены с соответствующими разрядными выходами блока памяти, первой группой информационных входов блока умножения первыми входами соответствующих

10

15

20

25

30

35

40

45

50

элементен} ны с соот информаци и вычитан второй гр вующей вт входов бло информацио рого соеди формационн ка памяти ствукщих э пы, вторые ей группы щими инфор дами блока дешифратор нен с перв ИЛИ, выход задержки с второго эл го соедине блока слож вход второ с выходом сел датчик ных случай первого эл тым выходо ления, вых читания бл соединен с элемента И нен с втор жения и вы тьего элем дом второг ления, чет седьмой ад соединены ными выход формационн входом зад генератора памяти сое рядными вх выход кото нератора, регистра с дешифратор

8

элементов

5

0

5

0

5

0

5

0

ИШ НТОРОЙ ГРУПШ 1, ВЫХ1: ДЫ

элементен} ИЛИ первой гругшы cocnn it ны с сооткетстную1цей nepi oii группой информационных входон блокл сложения и вычитания, выходы злементог ИЛИ второй группы соединены с соответствующей второй гр5 ппой т1формациоиных входов блока сложения и вычитания, информационные разрядные выходы которого соединены с cooTBeTCT sx-winitMn информационными разрядными входами блока памяти и первыми входами соответ- ствукщих элементов И.Ш третьей группы, вторые входы элементов ИЛИ т Н ть-- ей группы соединены с соответетвхто- щими информационными разрядными выходами блока умножения, третий выход дешифратора блока управления соединен с первым входом первого элемента ИЛИ, выход которого через элемент задержки соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом записи блока сложения и вычитания, второй вход второго элемента ИЛИ соединен с выходом окончания формирования чисел датчика равномерно распределенных случайных чисел, второй вход первого элемента ИЛИ соединен с шестым выходом дешифратора блока управления, выход окончания сложения и вычитания блока сложения и вычитания соединен с первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом записи блока сложения и вычитания, второй вход третьего элемента ИЛИ соединен с выходом второго элемента И блока управления, четвертьй, пятый, шестой и седьмой адресные входы блока памяти соединены с соответствующими разрядными выходами первого регистра, информационный вход которого является входом задания закона распределения генератора, разрядные выходы блока памяти соединены с одно -1менными разрядными входами второго регистра, выход которого является выходом генератора, вход синхронизации второго регистра соединен с дес. выходом дешифратора блока управления.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных чисел | 1989 |

|

SU1691838A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ИМПУЛЬСОВ | 1992 |

|

RU2032986C1 |

| Генератор случайных чисел | 1989 |

|

SU1833868A1 |

| Генератор случайных чисел | 1986 |

|

SU1417006A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР | 1991 |

|

SU1800889A1 |

| Вероятностный коррелометр | 1980 |

|

SU932500A1 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| Устройство для обращения матриц | 1988 |

|

SU1647591A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

Изобретение относится к вычис- лительной технике и может быть использовано в приставках к универ-- сальным ЭЦВМ для получения случайных чисел, подчиняющихся законам распределения Пирсона. Цель изобретения - расширение области применения за счет формирования случайных чисел, подчиняющихся законам распределения Пирсона. Генератор содержит датчик 1 равномерно распределенных случайных чисел, блок 2 сложения и вычитания, блок 3 умножения, блок 4 памяти,блок 5.управления, три группы 6, 7, 8 элементов ИЛИ, три злемента 9-11 ИЛИ, элемент 12 задержки и два регистра 13, 14. Поставленная цель достигается за счет введения новых блоков с соответствующими функциональными связями. 1 ил., 2 табл.

d o(-F(m)

Ai X 1 +Z, , AI Z, f,-Z

m+Z

2, Z,

Z,

X

Распределение

Код адресов величины

F(m)

J l J L 1 1 ™

1 2 3 4 5 6 7 8 9

0 11 12

0001001 0010001 0011001 0100001 0101001 0110001 0111001 1000001 1001001 1010001 1011001 1100001

0001010 0010010 0011010 0100010 0101010 0110010 0111010 1000010 1001010 101001,0 1011010 1100010

0001011 0010011 0011011 0100011 0101011 O1100 l1 0111011 1000011 1001011 1010011 1011011 1100011

F(m)

P

Ai Д.

2 3

m

Таблица 2

X

0001101 0010101 0011101 0100101 0101101 0110101 0111101 1000101 1001101 1010101 1011101 1100101

0001110 0010110 0011110 0100110 0101110 0110110 0111110 1000110 1001110 1010110 1011110 1100110

0001111 0010111 0011111 0100111 0101 111 0110111 0111111 1000111 1001111 1010111 1011111 1100111

| Дроздов Е.А | |||

| и др | |||

| Многопрограммные цифровые вычислительные машины | |||

| - М.: Воениздат, 1974 | |||

| Генератор случайных чисел | 1983 |

|

SU1099319A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-23—Публикация

1986-03-28—Подача