S

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для установления соединений в многоканальной цифровой системе связи | 1987 |

|

SU1483659A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СОСТОЯНИЯ И УПРАВЛЕНИЯ КАНАЛАМИ И ТЕХНИЧЕСКИМИ СРЕДСТВАМИ В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1991 |

|

RU2007878C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для оценки состояния каналов в симплексных системах связи | 1987 |

|

SU1554749A2 |

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2296420C1 |

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

| Стартстопно-синхронная система для передачи дискретных сигналов | 1981 |

|

SU1007212A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ АВТОМАТИЗИРОВАННЫМИ ОБЪЕКТАМИ ПО ТЕЛЕФОННЫМ СЕТЯМ | 1994 |

|

RU2106069C1 |

| СПОСОБ СТЕГАНОГРАФИЧЕСКОЙ ПЕРЕДАЧИ ИНФОРМАЦИИ ЧЕРЕЗ ГЛАВНЫЙ ОПТИЧЕСКИЙ ТРАКТ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2496239C1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение пропускной способности системы. Система связи содержит передающий ..блок 1, приемный блок 2, блок контроля 3 и блок опроса 4. Система связи работает в двух режимах: в режиме переключения канальных интервалов для передачи дискретной информации и в режиме переключения канальных интервалов для передачи речевых сигналов. Цель достигается введением блока контроля 3 и блока опроса 4, с помощью которых канальные интервалы, не задействованные под речь, используются для передачи дискретной информации. Система связи по пп.2-10 ф-льг отличается выполнением всех блоков и их узлов. Даны их ил. 9 з.п. ф-лы, 10 ил.

05

00

о

ел

Изобретение относится к радиотехнике и связи и может быть использовано в средствах связи с импульсно-ко- довой модуляцией.

Цель изобретения - увеличение пропускной способности системы.

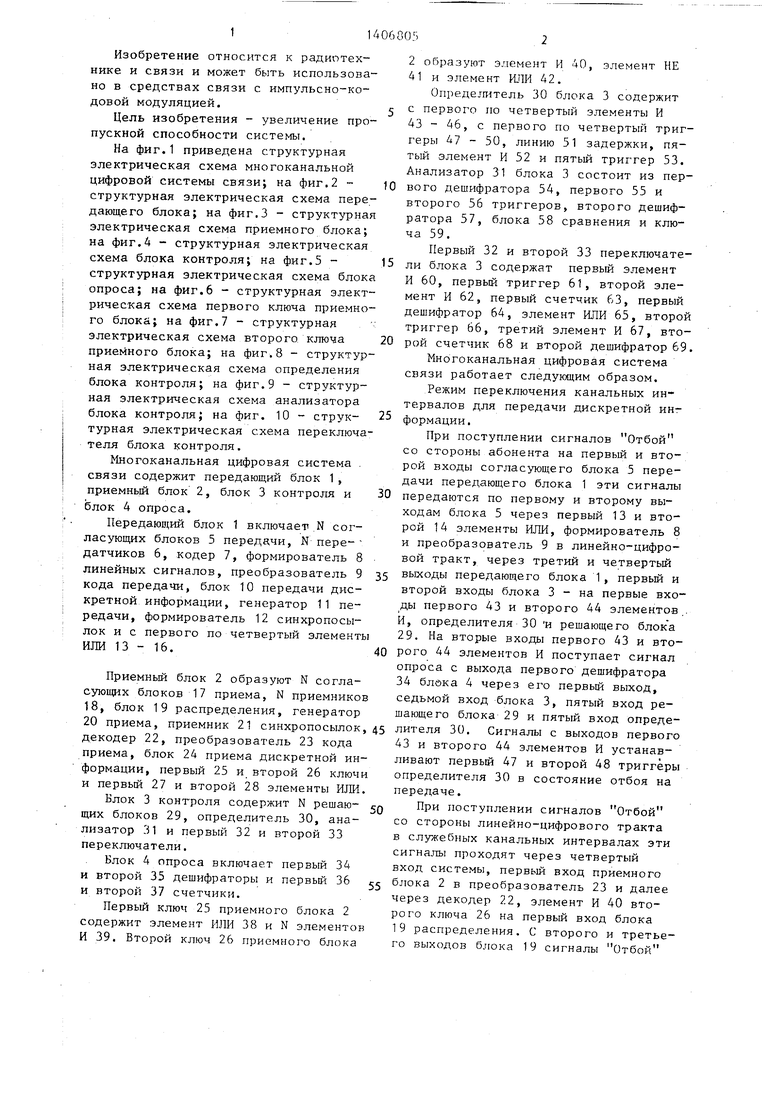

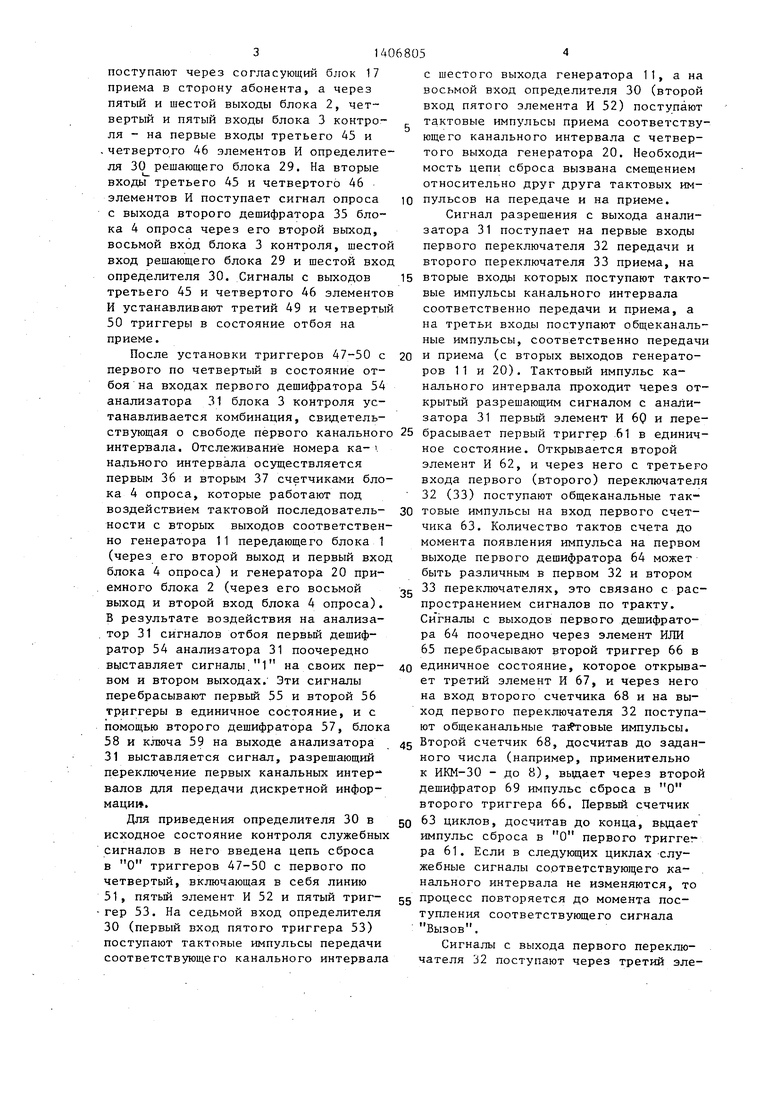

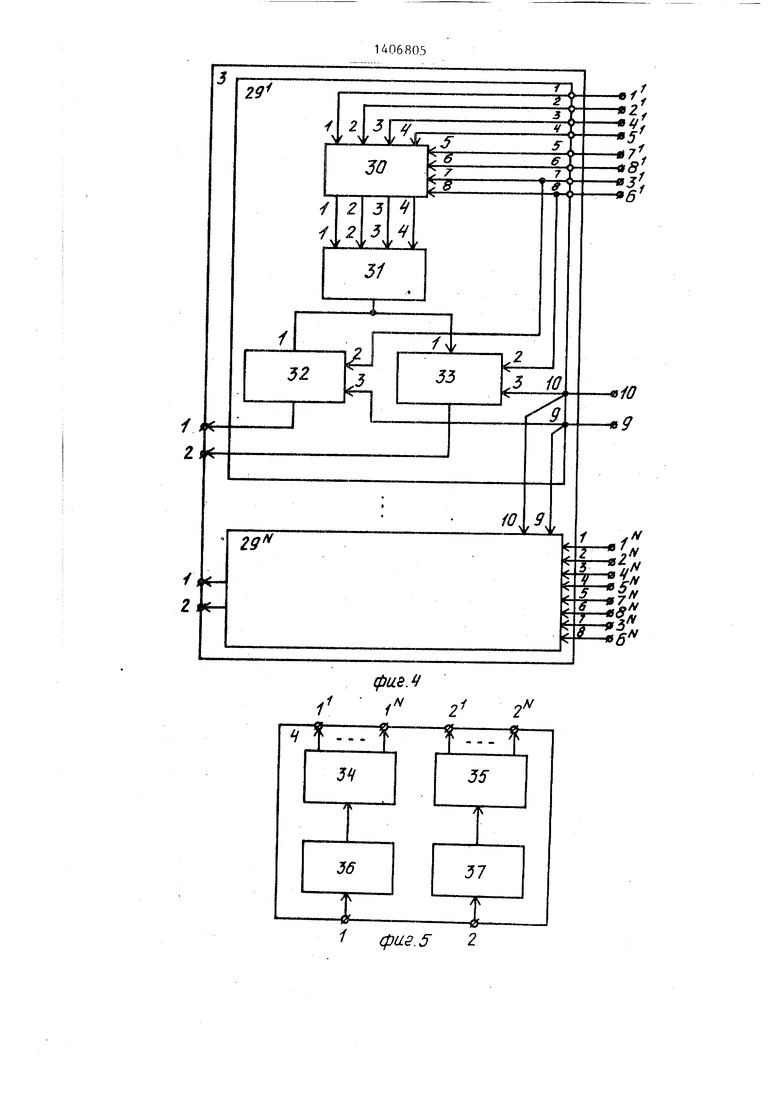

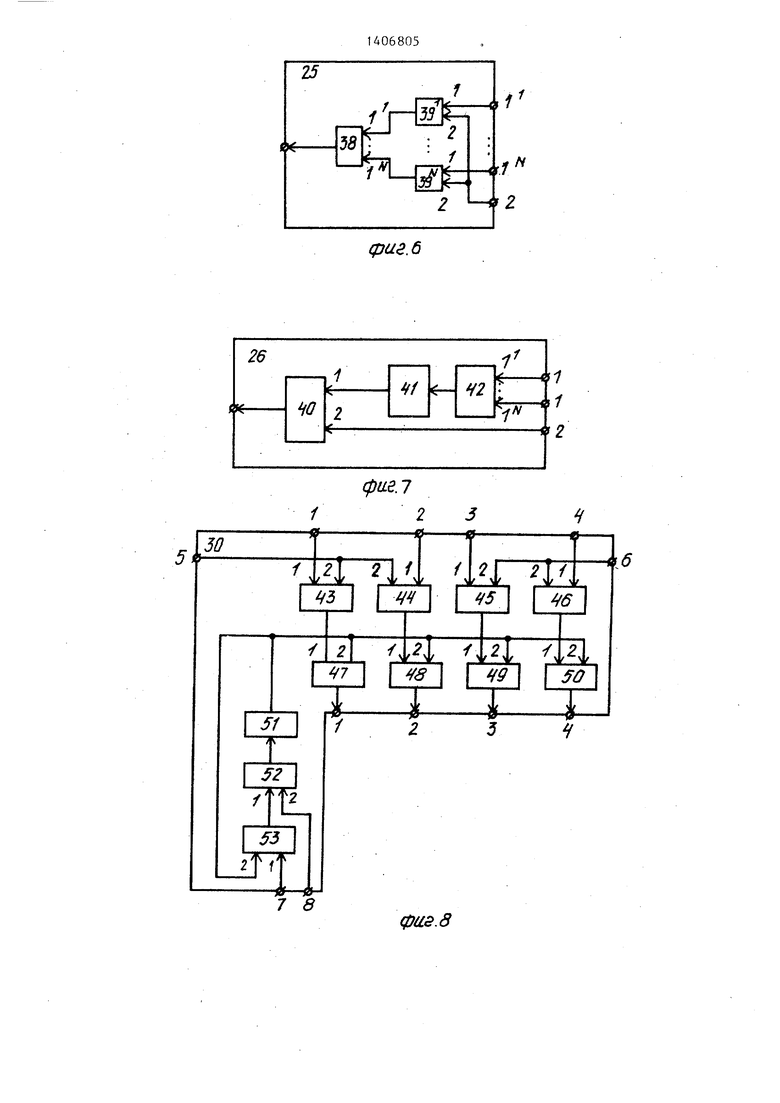

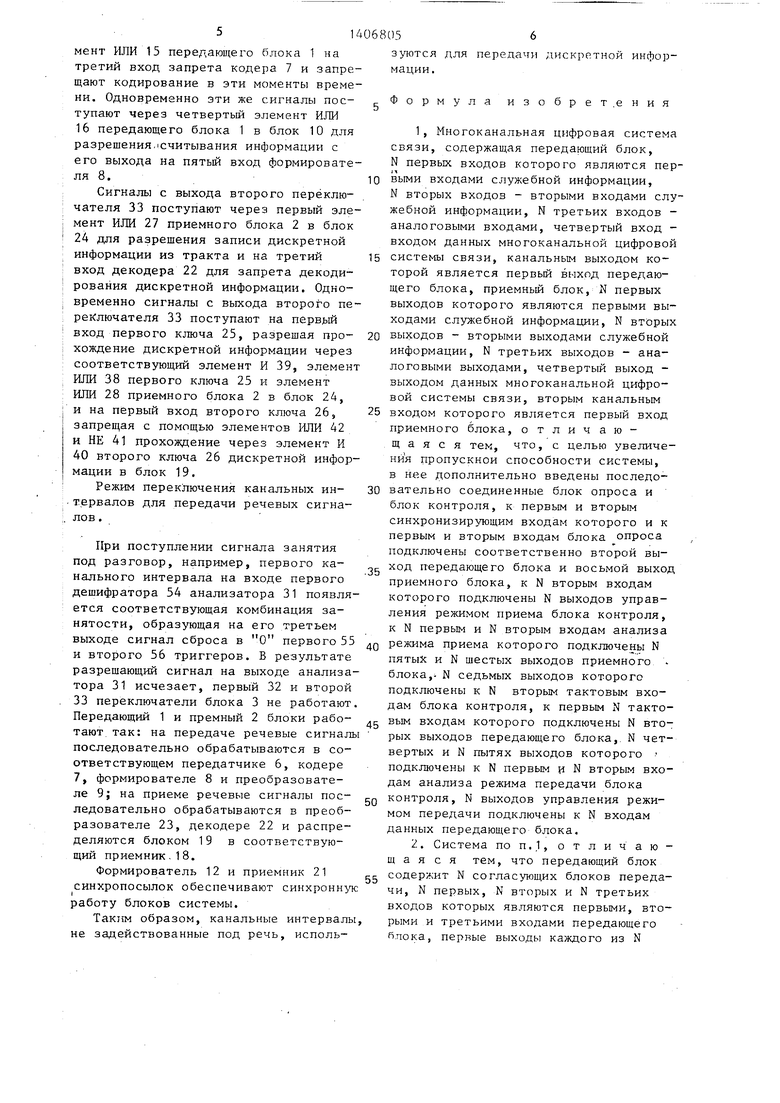

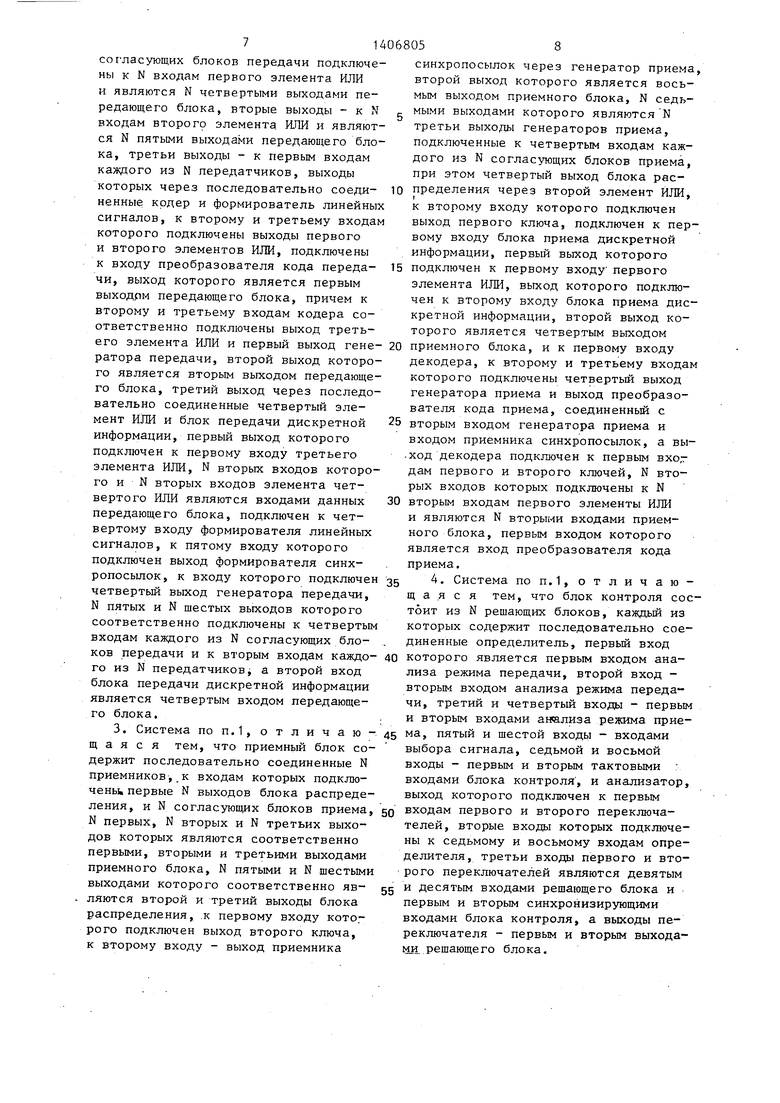

На фиг.1 приведена структурная электрическая схема многоканальной цифровой системы связи; на фиг.2 -- структурная электрическая схема передающего блока; на фиг.З - структурная электрическая схема приемного блока; на фиг.4 - структурная электрическая схема блока контроля; на фиг.З - структурная электрическая схема блока опроса; на фиг.6 - структурная электрическая схема первого ключа приемного блоки; на фиг. 7 - структурная электрическая схема второго ключа приемного блока; на фиг.8 - структурная электрическая схема определения блока контроля; на фиг.9 - структурная электрическая схема анализатора блока контроля; на фиг. 10 - струк- турная электрическая схема переключателя блока контроля.

Многоканальная цифровая система . связи содержит передающий блок 1, приемный блок 2, блок 3 контроля и блок 4 опроса.

Передающий блок 1 включает.N согласующих блоков 5 передачи, N пере- датчиков 6, кодер 7, формирователь 8 линейных сигналов, преобразователь 9 кода передачи, блок 10 передачи дискретной информации, генератор 11 передачи, формирователь 12 синхропосы- лок и с первого по четвертый элементы ИЛИ 13-16.

Приемный блок 2 образуют N согласующих блоков 17 приема, N приемников 18, блок 19 распределения, генератор 20 приема, приемник 21 синхропосылок декодер 22, преобразователь 23 кода приема, блок 24 приема дискретной информации, первый 25 и второй 26 ключи и первый 27 и второй 28 элементы ИЛИ

Блок 3 контроля содержит N решаю- щих блоков 29, определитель 30, анализатор 31 и первый 32 и второй 33 переключатели.

Блок 4 опроса включает первый 34 к второй 35 дешифраторы и первый 36 и второй 37 счетчики.

Первый ключ 25 приемного блока 2 содержит элемент ИЛИ 38 и N элементов И 39. Второй ключ 26 приемного блока

2 образуют элемент И 40, элемент НЕ 41 и элемент ИЛИ 42.

Опреде1гитель 30 блока 3 содержит с первого по четвертый элементы И 43 - 46, с первого по четвертый триггеры 47 - 50, линию 51 задержки, пятый элемент И 52 и пятый триггер 53. Анализатор 31 блока 3 состоит из первого дешифратора 54, первого 55 и второго 56 триггеров, второго дешифратора 57, блока 58 сравнения и ключа 59.

Первый 32 и второй 33 переключатели блока 3 содержат первый элемент И 60, первый триггер 61, второй элемент И 62, первый счетчик 63, первый дешифратор 64, элемент ИЛИ 65, второ триггер 66, третий элемент И 67, второй счетчик 68 и второй дешифратор 69

Многоканальная цифровая система связи работает следующим образом.

Режим переключения канальных интервалов для передачи дискретной информации.

При поступлении сигналов Отбой со стороны абонента на первый и второй входы согласующего блока 5 передачи передающего блока 1 эти сигналы передаются по первому и второму выходам блока 5 через первый 13 и второй 14 элементы ИЛИ, формирователь 8 и преобразователь 9 в линейно-цифровой тракт, через третий и четвертый выходы передающего блока 1, первый и второй входы блока 3 - на первые входы первого 43 и второго 44 элементов И, определителя 30 и решающего блок а 29. На вторые входы первого 43 и второго 44 элементов И поступает сигнал опроса с выхода первого дешифратора 34 блока 4 через его первый выход, седьмой вход блока 3, пятый вход решающего блока 29 и пятый вход определителя 30. Сигналы с выходов первого 43 и второго 44 элементов И устанавливают первый 47 и второй 48 триггеры определителя 30 в состояние отбоя на передаче.

При поступлении сигналов Отбой со стороны линейно-цифрового тракта в служебных канальных интервалах эти сигналы проходят через четвертый вход системы, первый вход приемного блока 2 в преобразователь 23 и далее через декодер 22, элемент И 40 второго ключа 26 на первый вход блока 19 распределения. С второго и третьего выходов блока 19 сигналы Отбой

поступают через согласующий блок 17 приема в сторону абонента, а через пятый и шестой выходы блока 2, четвертый и пятый входы блока 3 контроля - на первые входы третьего 45 и четвертого 46 элементов И определителя 30 решающего блока 29. На вторые входы третьего 45 и четвертого 46 элементов И поступает сигнал опроса с выхода второго дешифратора 35 блока 4 опроса через его второй вькод, восьмой вход блока 3 контроля, шестой вход решающего блока 29 и шестой вход определителя 30. Сигналы с выходов третьего 45 и четвертого 46 элементов И устанавливают третий 49 и четвертый 50 триггеры в состояние отбоя на приеме.

После установки триггеров 47-50 с первого по четвертый в состояние отбоя на входах первого дешифратора 54 анализатора 31 блока 3 контроля устанавливается комбинация, свидетельствующая о свободе первого канального 25 брасывает первый триггер 61 в единич- интервала. Отслеживание номера ка- . ное состояние. Открывается второй

нального интервала осуществляется первым 36 и вторым 37 счетчиками блока 4 опроса, которые работают под воздействием тактовой последовательности с вторых выходов соответственно генератора 11 передающего блока 1 (через его второй выход и первый вход блока 4 опроса) и генератора 20 приемного блока 2 (через его восьмой выход и второй вход блока 4 опроса). В результате воздействия на анализатор 31 сигналов отбоя первый дешифратор 54 анализатора 31 поочередно выставляет сигналы.1 на своих первом и втором выходах. Эти сигналы перебрасывают первый 55 и второй 56 триггеры в единичное состояние, и с помощью второго дешифратора 57, блока 58 и ключа 59 на выходе анализатора 31 выставляется сигнал, разрешающий цереключение первых канальных интер валов для передачи дискретной информации.

Для приведения определителя 30 в исходное состояние контроля служебных сигналов в него введена цепь сброса в О триггеров 47-50 с первого по четвертый, включающая в себя линию 51, пятый элемент И 52 и пятый триг- гер 53. На седьмой вход определителя 30 (первый вход пятого триггера 53) поступают тактовые импульсы передачи соответствующего канального интервала

с шестого выхода генератора 11, а на восьмой вход определителя 30 (второй вход пятого элемента И 52) поступают

тактовые импульсы приема соответству

ющего канального интервала с четвертого выхода генератора 20. Необходимость цепи сброса вызвана смещением относительно друг друга тактовых импульсов на передаче и на приеме.

Сигнал разрешения с выхода анализатора 31 поступает на первые входы первого переключателя 32 передачи и второго переключателя 33 приема, на

вторые входы которых поступают тактовые импульсы канального интервала соответственно передачи и приема, а на третьи входы поступают общеканальные импульсы, соответственно передачи

и приема (с вторых выходов генераторов 11 и 20). Тактовый импульс канального интервала проходит через открытый разрешающим сигналом с анализатора 31 первый элемент И 60 и переэлемент И 62, и через него с третьего входа первого (второго) переключателя 32 (33) поступают общеканальные тактовые импульсы на вход первого счетчика 63. Количество тактов счета до омента появления импульса на первом выходе первого дешифратора 64 может быть различным в первом 32 и втором

33 переключателях, это связано с распространением сигналов по тракту. Си гналы с выходов первого дешифратора 64 поочередно через элемент ИЛИ 65 перебрасывают второй триггер 66 в

единичное состояние, которое открывает третий элемент И 67, и через него на вход второго счетчика 68 и на выод первого переключателя 32 поступают общеканальные та1 товые импульсы.

Второй счетчик 68, досчитав до заданного числа (например, применительно к ИКМ-30 - до 8), вьщает через второй ешифратор 69 импульс сброса в О второго триггера 66. Первый счетчик

63 циклов, досчитав до конца, вьщает импульс сброса в О первого триггег- ра 61. Если в следующих циклах служебные сигналы соответствующего канального интервала не изменяются, то

процесс повторяется до момента поступления соответствующего сигнала Вызов.

Сигналы с выхода первого переклюателя 32 поступают через третий элемент ИЛИ 15 передающего блока 1 на третий вход запрета кодера 7 и запрещают кодирование в эти моменты времени. Одновременно эти же сигналы поступают через четвертый элемент ИЛИ 16 передающего блока 1 в блок 10 для разрешения, Считывания информации с его выхода на пятый вход формирователя 8.

Сигналы с выхода второго переключателя 33 поступают через первый элемент ИЛИ 27 приемного блока 2 в блок 24 для разрешения записи дискретной информации из тракта и на третий вход декодера 22 для запрета декодирования дискретной информации. Одновременно сигналы с выхода второго переключателя 33 поступают на первой вход первого ключа 25, разрешая прохождение дискретной информации через соответствующий элемент И 39, элемент ИЛИ 38 первого ключа 25 и элемент ИЛИ 28 приемного блока 2 в блок 24, и на первый вход второго ключа 26, запрещая с помощью элементов ИЛИ 42 и НЕ 41 прохождение через элемент И 40 второго ключа 26 дискретной информации в блок 19,

Режим переключения канальных ин- .тервалов для передачи речевых сигналов .

При поступлении сигнала занятия под разговор, например, первого канального интервала на входе первого дешифратора 54 анализатора 31 появляется соответствующая комбинация занятости, образующая на его третьем выходе сигнал сброса в О первого 55 и второго 56 триггеров. В результате разрешающий сигнал на выходе анализатора 31 исчезает, первый 32 и второй 33 переключатели блока 3 не работают Передающий 1 и премный 2 блоки работают, так: на передаче речевые сигнал последовательно обрабатываются в соответствующем передатчике 6, кодере 7, формирователе 8 и преобразователе 9; на приеме речевые сигналы последовательно обрабатываются в преобразователе 23, декодере 22 и распределяются блоком 19 в соответствующий приемник,18.

Формирователь 12 и приемник 21 синхропосылок обеспечивают синхронну работу блоков системы.

TaKiiM образом, канальные интервалы не задействованные под речь, исполь6

для передачи дискретной инфор

Формула изобрет.ения

1, Многоканальная цифровая система связи, содержащая передающий блок, N первых входов которого являются первыми входами служебной информации,

N вторых входов - вторыми входами служебной информации, N третьих входов - аналоговыми входами, четвертый вход - входом данных многоканальной цифровой

системы связи, канальным выходом которой является первый вЕ-1Ход передающего блока, приемный блок, N первых выходов которого являются первыми выходами служебной информации, N вторых

выходов - вторыми выходами служебной информации, N третьих выходов - аналоговыми выходами, четвертый выход - выходом данных многоканальной цифровой системы связи, вторым канальным

входом которого является первый вход приемного блока, отличающаяся тем, что, с целью увеличения пропускной способности системы, в нее дополнительно введены последо

вательно соединенные блок опроса и блок контроля, к первым и вторым синхронизирующим входам которого и к первым и вторым входам блока опроса подключены соответственно второй выход передающего блока и восьмой выход приемного блока, к N вторым входам которого подключены N выходов управления режимом приема блока контроля, к N первым и N вторым входам анализа режима приема которого подключены N пятых и N шестых выходов приемного . блока,- N седьмых выходов которого подключены к N вторым тактовым входам блока контроля, к первым N такто- вым входам которого подключены N вторых выходов передающего блока,. N четвертых и N пытях выходов которого подключены к N первым и N вторым входам анализа режима передачи блока контроля, N выходов управления режимом передачи подключены к N входам данных передающего блока.

714

согласующих блоков передачи подключены к N входам первого элемента ИЛИ и являются N четвертыми выходами передающего блока, вторые выходы - к N входам второг9 элемента КПИ и являются N пягъши выходами передающего блока, третьи выходы - к первым входам каждого из N передатчиков, выходы которых через последовательно соеди- ненные кодер и формирователь линейных сигналов, к второму и третьему входам которого подключены выходы первого и второго элементов ИЛИ, подключены к входу преобразователя кода переда- чи, выход которого является первым выходрм передающего блока, причем к второму и третьему входам кодера соответственно подключены выход треть

его элемента ИЛИ и первый выход гене- 20 приемного блока, и к первому входу

ратора передачи, второй выход которого является вторым выходом передающего блока, третий выход через последовательно соединенные четвертый элемент ИЛИ и блок передачи дискретной информации, первый выход которого подключен к первому входу третьего элемента ИЛИ, N вторых входов которого и N вторых входов элемента четвертого ИЛИ являются входами данных передающего блока, подключен к четвертому входу формирователя линейных сигналов, к пятому входу которого подключен выход формирователя синх- ропосылок, к входу которого подключен четвертый выход генератора передачи, N пятых и N шестых выходов которого соответственно подключены к четвертым входам каждого из N согласующих блоков передачи и к вторым входам каждо- го из N передатчиковj а второй вход блока передачи дискретной информации является четвертым входом передающего блока.

синхропосылок через генератор приема второй выход которого является восьмым выходом приемного блока, N седьмыми выходами которого являются N третьи выходы генераторов приема, подключенные к четвертым входам каждого из N согласующих блоков приема, при этом четвертый выход блока распределения через второй элемент ИЛИ, к второму входу которого подключен выход первого ключа, подключен к первому входу блока приема дискретной информации, первый выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к второму входу блока приема дискретной информации, второй выход которого является четвертым выходом

декодера, к второму и третьему входам которого подключены четвертый выход генератора приема и выход преобразователя кода приема, соединенньй с вторым входом генератора приема и входом приемника синхропосылок, а вы- - ход декодера подключен к первым вхо,- дам первого и второго ключей, N вторых входов которых подключены к N вторым входам первого элементы ИЛИ и являются N вторыми входами приемного блока, первым входом которого является вход преобразователя кода приема,

второй счетчик, вход которого являет- 10 которого являются вторые входы пятого ся вторым входом блока опроса, и вто- триггера и пятого элемента И.

рой дешифратор, N выходов которого являются N вторыми выходами блока опроса.

6,Система по п.З, о тлич аю щ а я с я тем, что первый ключ приемного блока содержит N элементов И, первые входы которых являются первым входом ключа, вторые входы - N вторыми входами ключа, выходы N элементов И подключены к N входам элемента ИЛИ, выход которого является выходом ключа,

15 первый, второй, третий и четвертый .«входы которого являются соответственно первым, вторым, третьим и четвертым входами анализатора, первый выход первого дешифратора через первый

20 триггер подключен к первым входам второго дешифратора и блока сравнения, выходы которых подключены к первому и второму входам, ключа, выход которого. Является выходом анализато25

ра, второй выход первого дешифратора подключен к первому входу второго триггера, третий выход - к вторым входам первого и второго триггеров, выход второго триггера подключен к

И, второй вход которого является пер- 30 вторым входам второго дешифратора и

вым входом второго ключа, а выход - блока сравнения.

первым выходом второго ключа.10. Система по п.4, отличаю8. Система по п.4,отличаю- щаяся тем, что переключатель

блока контроля содержит последова- 3g тельно соединные первый элемент И, входы которого являются первым и втощаяся тем, что определитель блока контроля содержит первый, второй, третий, четвертый элементы И, первые входы которых являются первым, вторым, третьим и четвертым входами определителя, вторые входы первого и второго элементов И являются пятым входом определителя, вторые входы третьего и четвертого элементов И г шестым входом определителя, выходы первого, второго, третьего и четвертого элементов И hoдключeны соответственно к первым входам первого, второго, третьего и четвертого триггеров, к вторым входам которых через последовательно соединенные пятый

рым входами переключателя, первый триггер, второй элемент И, первый счетчик, первьм дешифратор, N-й выход

40 которого подключен к второму входу . первого триггера, элемент ИЛИ, второй триггер, третий элемент И, второй вход которого и второй вход второго элемента И являются третьим входом

45 переключателя, второй счетчик и второй дешифратор, выход которого подключен к второму входу второго триггера, а выход третьего элемента И является выходом переключателя.

10

И и линию задержки подключен

выход пятого триггера, к первому входу которого подключен выход линии задержки, а выходы первого, второго, третьего и четвертого триггеров являются соответственно первым, вторым, третьим и четвертым выходами определителя, седьмым и восьмым входами

15 первый, второй, третий и четвертый .«входы которого являются соответственно первым, вторым, третьим и четвертым входами анализатора, первый выход первого дешифратора через первый

20 триггер подключен к первым входам второго дешифратора и блока сравнения, выходы которых подключены к первому и второму входам, ключа, выход которого. Является выходом анализато25

ра, второй выход первого дешифратора подключен к первому входу второго триггера, третий выход - к вторым входам первого и второго триггеров, выход второго триггера подключен к

рым входами переключателя, первый триггер, второй элемент И, первый счетчик, первьм дешифратор, N-й выход

40 которого подключен к второму входу . первого триггера, элемент ИЛИ, второй триггер, третий элемент И, второй вход которого и второй вход второго элемента И являются третьим входом

45 переключателя, второй счетчик и второй дешифратор, выход которого подключен к второму входу второго триггера, а выход третьего элемента И является выходом переключателя.

фиё.

7 8

фаг.б

ф1лг.1

фИ5.8

/ 2 JV

cpue.9

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1988-06-30—Публикация

1986-02-04—Подача