(jO 00

ел N3

О5

задержки, второй одновибратор 47, элемент ИЛИ 48, первый одновибратор 49 и второй элемент 50 задержки.

Коммутатор 9 контрольных сигналов выполнен на элементах ИЛИ 51 и 52 и элементе И-НЕ 53.

Кроме того, устройство содержит мультиплексор 54, третий регистр 55, дешифратор 56, двунаправленный коммутатор 57 и четвертый элемент И 58.

Двунаправленный коммутатор 57 образован матрицей НХ Н двунаправленных ключей 59 (где Н - число строк и столбцов в матрице).

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения большой ЭВМ высокой производительности с микроэвм при построении локальных вычислительных сетей (например, БЭСМ - 6 и «Электроника-60).

Цель изобретения - расширение функциональных возможностей устройства и повышение достоверности обмена ЭВМ за счет аппаратной упаковки разрядов слова данных ю и взаимного независимого двустороннего контроля канала сопряжения.

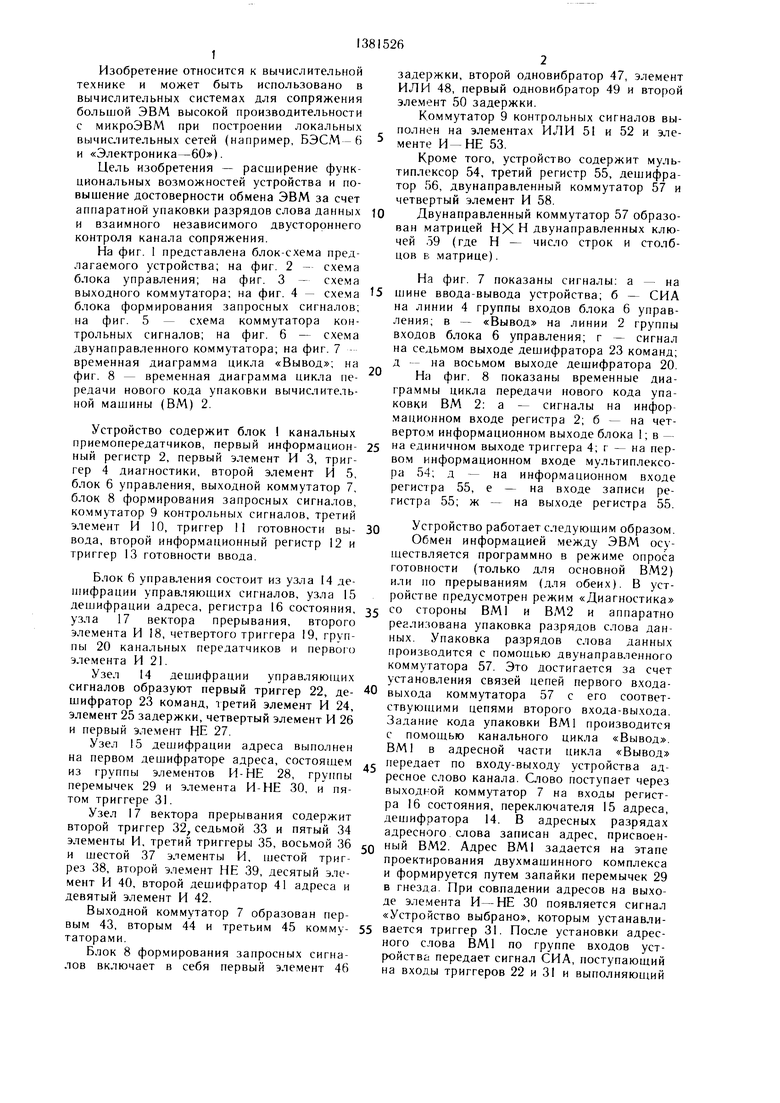

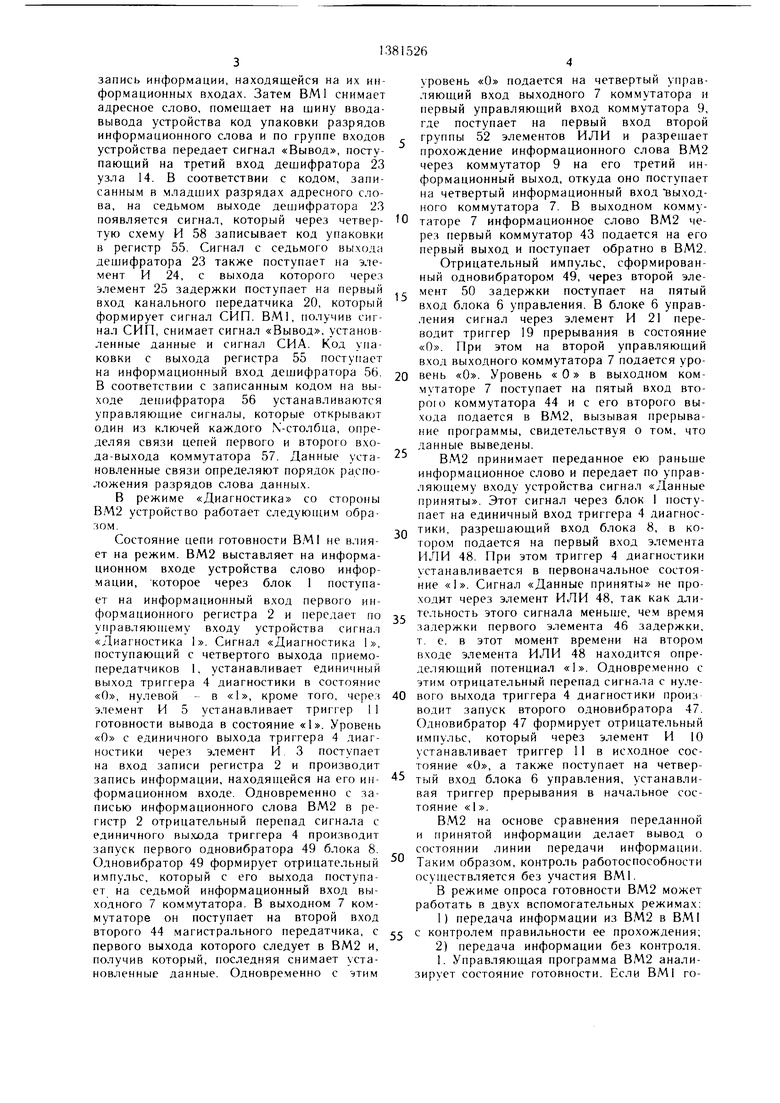

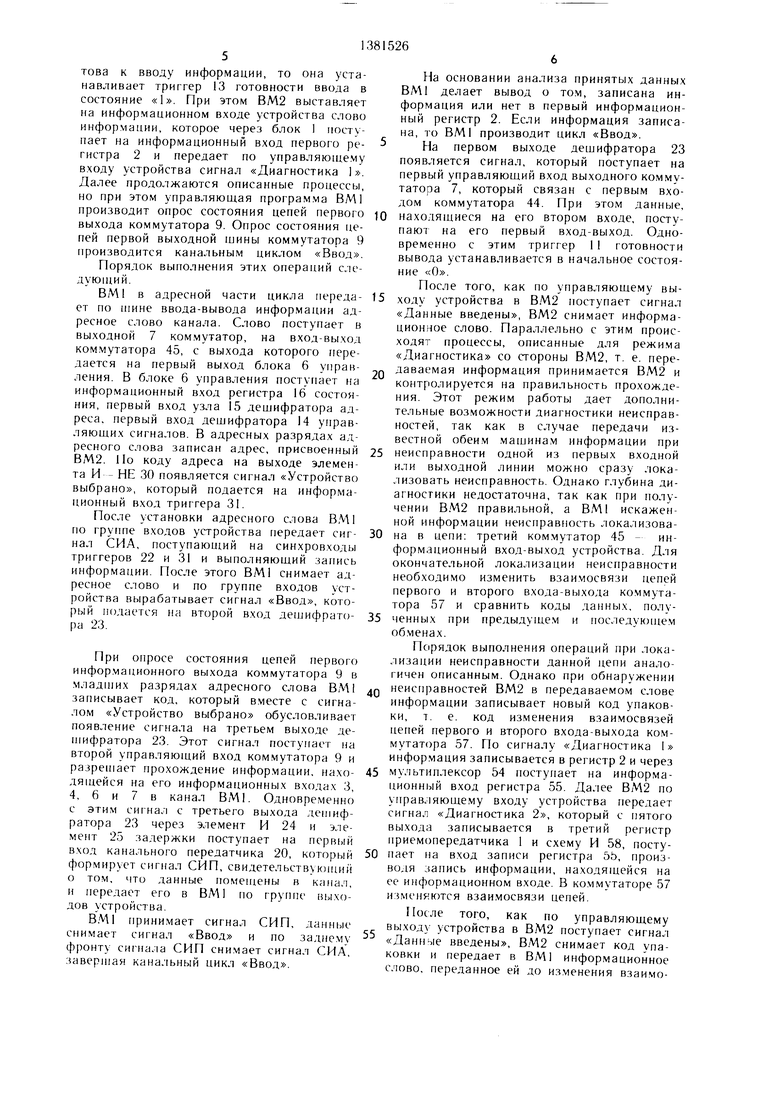

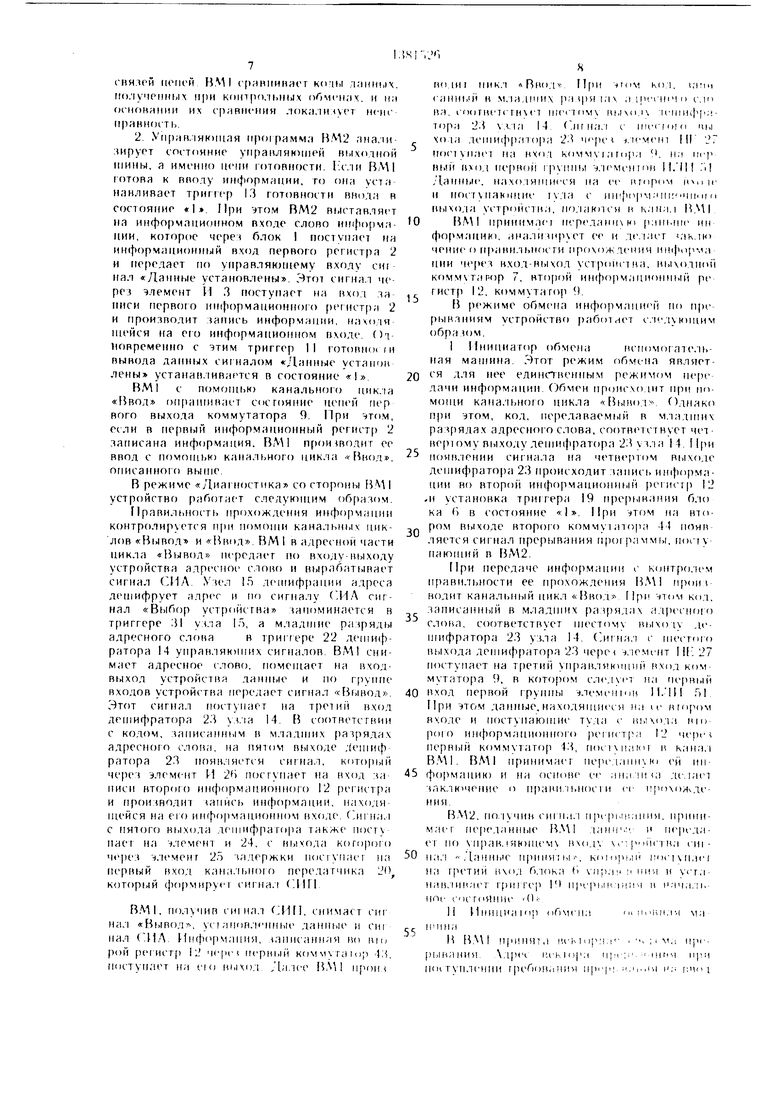

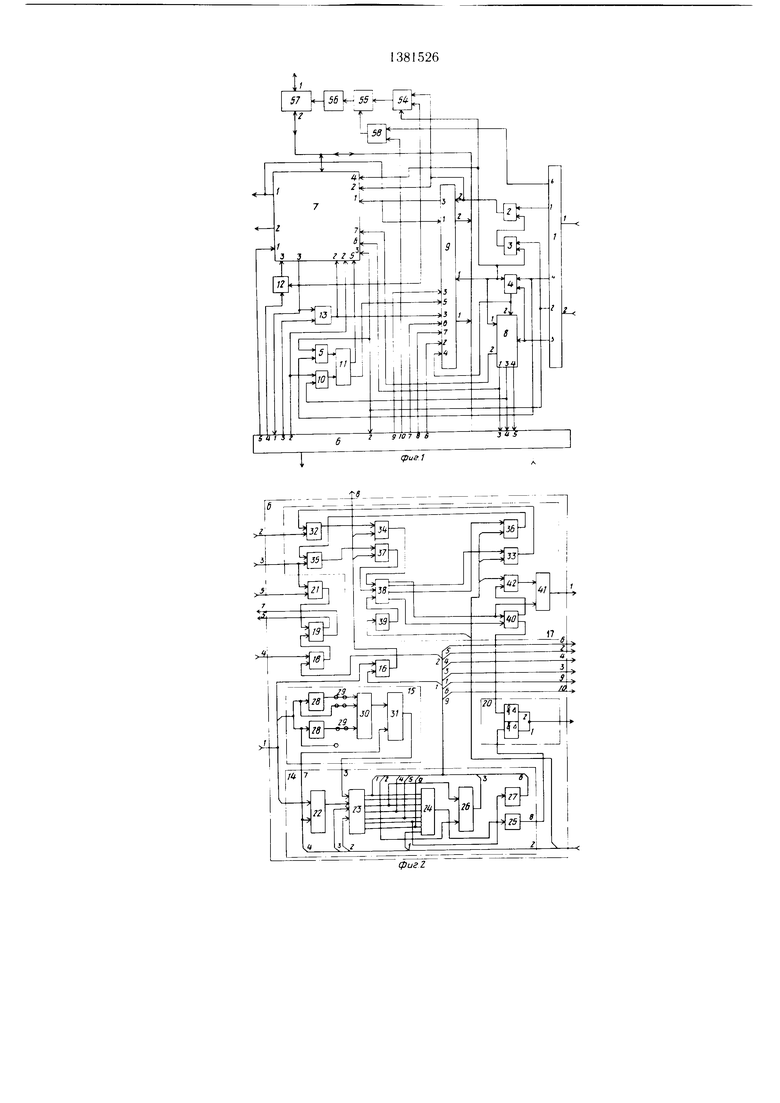

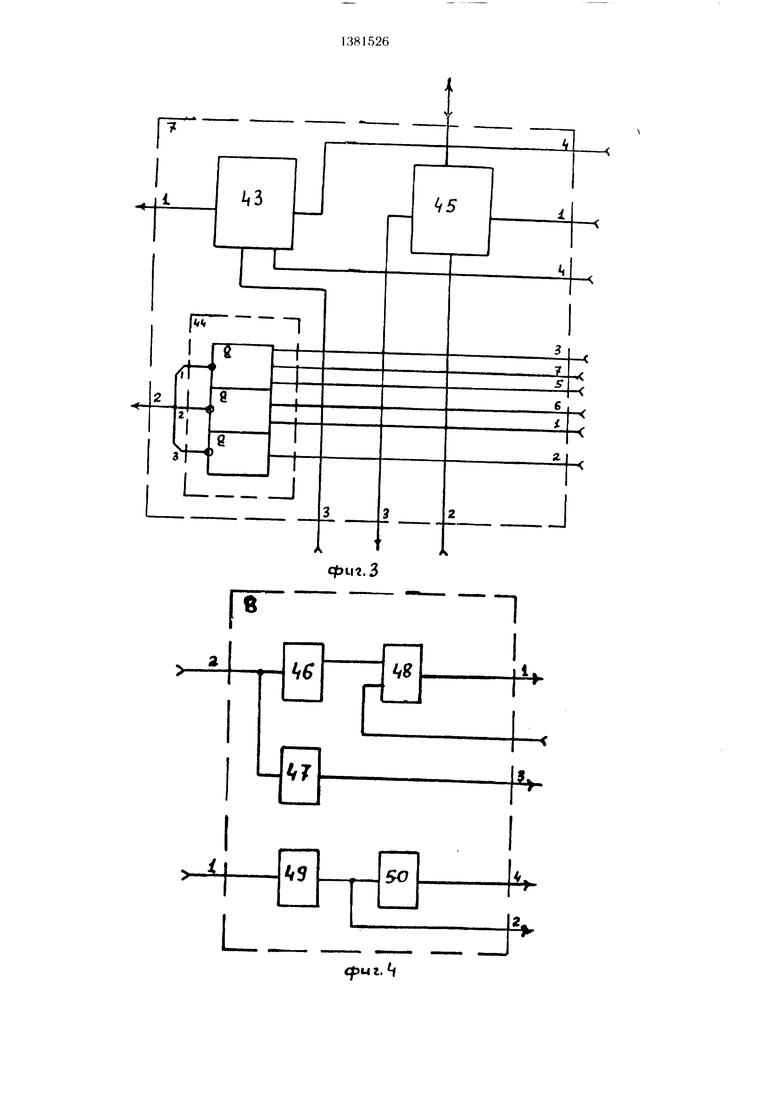

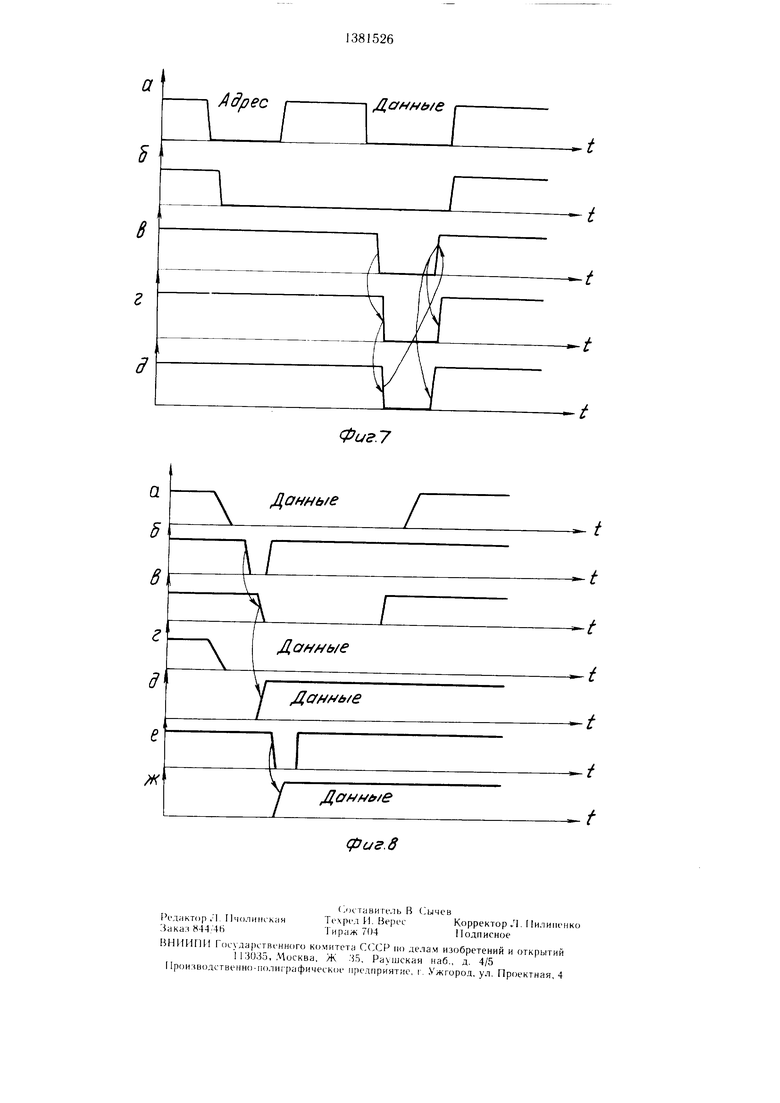

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема выходного коммутатора; на фиг. 4 - схема 5 шине ввода-вывода устройства; б - СИЛ блока формирования запросных сигналов;на линии 4 группы входов блока 6 управна фиг. 5 - схема коммутатора контрольных сигналов; на фиг. 6 - схема двунаправленного коммутатора; на фиг. 7

временная диаграмма цикла «Вывод ; наД - на восьмом выходе дешифратора 20.

фиг. 8 - временная диаграмма цикла пе- На фиг. 8 показаны временные диаграммы цикла передачи нового кода упаковки ВМ 2: а - сигналы на информационном входе регистра 2; б - на чет- верто.м информационном выходе блока 1; в -

приемопередатчиков, первый информацион- 25 единичном выходе триггера 4; г на пер- ный регистр 2, первый элемент И 3, триг-вом информационном входе мультиплексогер 4 диагностики, второй элемент И 5, блок 6 управления, выходной коммутатор 7, блок 8 формирования запросных сигналов, ко.ммутатор 9 контрольных сигналов, третий элемент И 10, триггер 11 готовности вы- 30 вода, второй информационный регистр 12 и триггер 13 готовности ввода.

На фиг. 7 показаны сигналы: а - на

ления; в - «Вывод на линии 2 группы входов блока 6 управления; г - сигнал на седьмом выходе дешифратора 23 команд;

фиг. 8 - временная диаграмма редачи нового кода упаковки вычислительной машины (ВМ) 2.

Устройство содержит блок I канальных

ра 54; д - на информационном входе регистра 55, е - на входе записи регистра 55; ж - на выходе регистра 55.

Устройство работает следующим образом.

Обмен информацией между ЭВМ осуществляется программно в режиме опроса готовности (только для основной ВМ2) или по прерываниям (для обеих). В устройстве предусмотрен режим «Диагностика)

Обмен информацией между ЭВМ осуществляется программно в режиме опроса готовности (только для основной ВМ2) или по прерываниям (для обеих). В устройстве предусмотрен режим «Диагностика)

Блок 6 управления состоит из узла 14 дешифрации управляющих сигналов, узла 15

дещифрации адреса, регистра 16 состояния,35 со стороны ВМ1 и ВМ2 и аппаратно узла 17 вектора прерывания, второгореализована упаковка разрядов слова дан- элемента И 18, четвертого триггера 19, груп-ных. Упаковка разрядов слова данных пы 20 канальных передатчиков и первогопроизводится с помощью двунаправленного элемента И 21.коммутатора 57. Это достигается за счет

Узел 14 дещифрации управляющихустановления связей цепей первого входасигналов образуют первый триггер 22, де-40 выхода коммутатора 57 с его соответшифратор 23 команд, третий элемент И 24,ствуюшими цепями второго входа-выхода,

элемент 25 задержки, четвертый элемент И 26Задание кода упаковки ВМ1 производится

и первый элемент НЕ 27.с помощью канального цикла «Вывод.

Узел 15 дешифрации адреса выполненВМ1 в адресной части цикла «Вывод

на первом дешифраторе адреса, состоящем.с передает по входу-выходу устройства адиз группы элементов И-НЕ 28, гру1щыресное слово канала. Слово поступает через

перемычек 29 и элемента И-НЕ 30, и пя-выходной коммутатор 7 на входы регисттом триггере 31.ра 16 состояния, переключателя 15 адреса.

Узел 17 вектора прерывания содержитдешифратора 14. В адресных разрядах

второй триггер 32, седьмой 33 и пятый 34адресного слова записан адрес, присвоенэлементы И, третий триггеры 35, восьмой 36JQ ный ВМ2. Адрес ВМ1 задается на этапе

и щестой 37 элементы И, щестой триг-проектирования двухмашинного комплекса

рез 38, второй элемент НЕ 39, десятый эле-и формируется путем запайки перемычек 29

мент И 40, второй дещифратор 41 адреса ив гнезда. При совпадении адресов на выходевятый элемент И 42.де элемента 30 появляется сигнал

Выходной коммутатор 7 образован пер-«Устройство выбрано, которым устанавливым 43, вторым 44 и третьим 45 комму-55 вается триггер 31. После установки адрестаторами.ного слова ВМ1 по группе входов устБлок 8 формирования запросных сигна-ройства передает сигнал СИЛ, поступающий

лов включает в себя первый элемент 46на входы триггеров 22 и 31 и выполняющий

задержки, второй одновибратор 47, элемент ИЛИ 48, первый одновибратор 49 и второй элемент 50 задержки.

Коммутатор 9 контрольных сигналов выполнен на элементах ИЛИ 51 и 52 и элементе И-НЕ 53.

Кроме того, устройство содержит мультиплексор 54, третий регистр 55, дешифратор 56, двунаправленный коммутатор 57 и четвертый элемент И 58.

Двунаправленный коммутатор 57 образован матрицей НХ Н двунаправленных ключей 59 (где Н - число строк и столбцов в матрице).

шине ввода-вывода устройства; б - СИЛ на линии 4 группы входов блока 6 управне ввода-вывода устройства; б - СИЛ линии 4 группы входов блока 6 управНа фиг. 7 показаны сигналы: а - на

шине ввода-вывода устройства; б - СИЛ на линии 4 группы входов блока 6 управления; в - «Вывод на линии 2 группы входов блока 6 управления; г - сигнал на седьмом выходе дешифратора 23 команд;

единичном выходе триггера 4; г на пер- вом информационном входе мультиплексора 54; д - на информационном входе регистра 55, е - на входе записи регистра 55; ж - на выходе регистра 55.

Устройство работает следующим образом.

Обмен информацией между ЭВМ осуществляется программно в режиме опроса готовности (только для основной ВМ2) или по прерываниям (для обеих). В устройстве предусмотрен режим «Диагностика)

со стороны ВМ1 и ВМ2 и аппаратно реализована упаковка разрядов слова дан- ных. Упаковка разрядов слова данных производится с помощью двунаправленного оммутатора 57. Это достигается за счет

запись информации, иаходящейся на их информационных входах. Затем ВМ1 снимает адресное слово, помещает на шину ввода- вывода устройства код упаковки разрядов информационного слова и по группе входов устройства передает сигнал «Вывод, поступающий на третий вход дешифратора 23 узла 14. В соответствии с кодом, записанным в младших разрядах адресного слова, на седьмом выходе дешифратора 23

уровень «О подается на четвертый управляющий вход выходного 7 коммутатора и первый управляющий вход коммутатора 9, где поступает на первый вход второй - группы 52 элементов ИЛИ и разрешает прохождение информационного слова ВМ2 через коммутатор 9 на его третий информационный выход, откуда оно поступает на четвертый информационный вход выходного коммутатора 7. В выходном коммупоявляется сигнал, который через четвер- tO таторе 7 информационное слово ВМ2 че- тую схему И 58 записывает код упаковкирез первый коммутатор 43 подается на его

в регистр 55. Сигнал с седьмого выход; дешифратора 23 также поступает на элемент И 24, с выхода которого через

первый выход и поступает обратно в ВМ2. Отрицательный импульс, сформированный одновибратором 49, через второй элеэлемент 25 задержки поступает на первыймент 50 задержки поступает на пятый

вход канального передатчика 20, который вход блока б управления. В блоке б управ- формирует сигнал СИП. ВМ1, получив сиг- -. -нал СИП, снимает сигнал «Вывод, установленные данные и сигнал СИА. Код упаковки с выхода регистра 55 поступает

на информационный вход дешифратора 56. 20 вень «О. Уровень «О в выходном ком- В соответствии с записанным кодом на вы-мутаторе 7 поступает на пятый вход втоходе дешифратора 56 устанавливаются

ления сигнал через элемент И 21 переводит триггер 19 прерывания в состояние «О. При этом на второй управляющий вход выходного коммутатора 7 подается уроуправляющие сигналы, которые открывают один из ключей каждого N-столбца, определяя связи цепей первого и второго входа-выхода коммутатора 57. Данные уста- 25 новленные связи определяют порядок расположения разрядов слова данных.

В режиме «Диагностика со CTopofibi ВМ2 устройство работает следующим образом.

Состояние цепи готовности B.MI не влияет на режим. ВМ2 выставляет на информационном входе устройства слово информации, -которое через блок 1 поступает на информационный вход первого ин30

рою коммутатора 44 и с его второго выхода подается в ВМ2, вызывая прерывание программы, свидетельствуя о том, что данные выведены.

принимает переданное ею раньше информационное слово и передает по управ- ляюще.му входу устройства сигнал «Данные приняты. Этот сигнал через блок 1 поступает на единичный вход триггера 4 диагностики, разрещающий вход блока 8, в котором подается на первый вход элемента ИЛИ 48. При этом триггер 4 диагностики устанавливается в первоначальное состояние «1. Сигнал «Данные приняты не проходит через элемент ИЛИ 48, так как длиформационного регистра 2 и перелает по 35 тельность этого сигнала меньше, чем время управляющему входу устройства сигналзадержки первого элемента 46 задержки,

«Диагностика 1. Сигнал «Диагностика 1,т. е. в этот момент времени на втором

поступающий с четвертого выхода приемо-входе элемента ИЛИ 48 находится опрепередатчиков 1, устанавливает единичныйделяющий потенциал «1. Одновре.менпо с

выход триггера 4 диагностики в состояниеэтим отрицательный перепад сигнала с нуле«0, нулевой - в «1, кроме того, через 40 вого выхода триггера 4 диагностики произ эле.мент И 5 устанавливает триггер 1 1водит запуск второго одновибратора 47.

готовности вывода в состояние «Ь. УровеньОдновибратор 47 формирует отрицательный

«О с единичного выхода триггера 4 диаг-импульс, который через элемент И 10

ностики через элемент И 3 поступаетустанавливает триггер 11 в исходное сосна вход записи регистра 2 и производиттояние «О, а также поступает на четверзапись информации, находящейся на его ин- 45 вход блока 6 управления, устанавли- формационном входе. Одновременно с за-вая триггер прерывания в начальное сосписью информационного слова ВМ2 в ре-тояние «I.

гистр 2 отрицательный перепад сигнала сВМ2 на основе сравнения переданной

единичного выхода триггера 4 производити принятой информации делает вывод о

запуск первого одновибратора 49 блока 8.состоянии линии передачи информации.

Одновибратор 49 формирует отрицательныйТаким образом, контроль работоспособности

и.мпульс, который с его выхода поступа-осуществляется без участия ВМ1.

В режиме опроса готовности ВМ2 может работать в двух вспомогательных режимах: 1) передача информации из ВМ2 в BMI второго 44 магистрального передатчика, с 55 с контролем правильности ее прохождения; первого выхода которого следует в ВМ2 и,2) передача информации без контроля.

1. Управляющая программа ВМ2 анализирует состояние готовности. Если ВМ1 гоет на седьмой информационный вход выходного 7 коммутатора. В выходном 7 коммутаторе он поступает на второй вход

получив который, последняя снимает установленные данные. Одновременно с этим

уровень «О подается на четвертый управляющий вход выходного 7 коммутатора и первый управляющий вход коммутатора 9, где поступает на первый вход второй группы 52 элементов ИЛИ и разрешает прохождение информационного слова ВМ2 через коммутатор 9 на его третий информационный выход, откуда оно поступает на четвертый информационный вход выходного коммутатора 7. В выходном коммутаторе 7 информационное слово ВМ2 че- рез первый коммутатор 43 подается на его

вход блока б управления. В блоке б управ- -. -вень «О. Уровень «О в выходном ком- мутаторе 7 поступает на пятый вход втоления сигнал через элемент И 21 переводит триггер 19 прерывания в состояние «О. При этом на второй управляющий вход выходного коммутатора 7 подается уро30

това к вводу информации, то она устанавливает триггер 13 готовности ввода в состояние «1. При этом ВМ2 выставляет на информационном входе устройства слово информации, которое через блок I поступает на информационный вход первого ре- гистра 2 и передает по управляющему входу устройства сигнал «Диагностика 1. Далее продолжаются описанные процессы, но при этом управляющая программа ВМ1 производит опрос состояния цепей первого выхода коммутатора 9. Опрос состояния цепей первой выходной шины коммутатора 9 производится канальным циклом «Ввод.

Порядок выполнения этих операций следующий.

ВЛА в адресной части цикла переда- ет по пжне ввода-вывода информации адресное слово канала. Слово поступает в выходной 7 коммутатор, на вход-выход коммутатора 45, с выхода которого передается на первый выход блока 6 управления. В блоке б управления поступает на информационный вход регистра 16 состояния, первый вход узла 15 дешифратора адреса, первый вход дешифратора 14 управляющих сигналов. В адресных разрядах адресного слова записан адрес, присвоенный ВМ2. Но коду адреса на выходе элемента И - НЕ 30 появляется сигнал «Устройство выбрано, который подается на информационный вход триггера 31.

После установки адресного слова ВМ1 по группе входов устройства передает сиг- нал СИЛ, поступающий на синхровходы триггеров 22 и 31 и выполняющий запись инфор.мации. После этого ВМ1 снимает адресное слово и цо группе входов устройства вырабатывает сигнал «Ввод, который подается на второй в.ход дешифрато- ра 23.

При опросе состояния цепей первого инфор.мационного выхода коммутатора 9 в младших разрядах адресного слова ВМ1 записывает код, который вместе с сигналом «Устройство выбрано обусловливает появление сигнала на третьем выходе де- 1иифратора 23. Этот сигнал цостуггает на второй управляющий вход коммутатора 9 и разрешает прохождение информации, нахо- дящейся на его информационных входах 3, 4, 6 и 7 в канал ВМ1. Одновременно с этим сигнал с третьего выхода деп1иф- ратора 23 через элемент И 24 и элемент 25 задержки поступает на первый вход канального передатчика 20, который формирует сигнал СИП, свидетельствуюи1ий о том, что данные помещены в канал, и передает его в ВМ1 по группе выходов устройства.

ВМ1 принимает сигнал СИП, данные снимает сигнал «Ввод и по заднему фронту сигнала СИП снимает сигнал СИЛ, завершая канальный цикл «Ввод.

0

5

5 5

0 5

5 0

0

На основании анализа принятых данных делает вывод о том, записана информация или нет в первый информационный регистр 2. Если информация записана, то ВМ1 производит цикл «Ввод.

На первом выходе дешифратора 23 появляется сигнал, который поступает на первый управляющий вход выходного коммутатора 7, который связан с первым входом коммутатора 44. При этом данные, находящиеся на его втором входе, поступают на его первый вход-выход. Одновременно с этим триггер 11 готовности вывода устанавливается в начальное состояние «О.

После того, как по управляющему выходу устройства в ВМ2 поступает сигнал «Данные введены, ВМ2 снимает информационное слово. Параллельно с этим происходят процессы, описанные для режи.ма «Диагностика со стороны ВМ2, т. е. передаваемая информация принимается ВМ2 и контролируется на правильность прохождения. Этот режим работы дает дополнительные возможности диагностики неисправностей, так как в случае передачи известной обеи.м мащинам информации при неисправности одной из первых входной или выходной линии можно сразу локализовать неисправность. Однако глубина диагностики недостаточна, так как при получении ВМ2 правильной, а ВМ1 искаженной инфор.мации неисправность локализована в цепи: третий коммутатор 45 - информационный вход-выход устройства. Для окончательной локализации неисправности необходимо изменить взаимосвязи цепей первого и второго входа-выхода коммутатора 57 и сравнить коды данных, полученных при предыдущем и последуюп1ем об.менах.

Порядок выполнения операций при локализации неисправности данной цепи аналогичен описанным. Однако при обнаружении неисправностей ВМ2 в передаваемом слове информации записывает новый код упаковки, т. е. код изменения взаимосвязей цепей первого и второго входа-выхода коммутатора 57. По сигналу «Диагностика I информация записывается в регистр 2 и через мультиплексор 54 поступает на информационный вход регистра 55. Да. 1ее ВМ2 по управляющему входу устройства передает сигна.п «Диагностика 2, который с пятого выхода записывается в третий регистр приемопередатчика 1 и схему И 58, поступает на вход записи регистра 55, производя запись информации, находящейся на ее информационном входе. В коммутаторе 57 изменяются взаимосвязи цепей.

После того, как по управляющему выходу устройства в ВМ2 поступает сигнал «Данные введены, ВМ2 снимает код упаковки и передает в ВМ) информационное слово, переданное ей до изменения взаимоснч.юй попой BMI o);iH:iHFiaoT коцы лпиных. rio. iyiioiiMMx |1()И К(11п|и)лы1ых оОмонах. и n;i осипвнмии их срнниоиня Л()к;1ли:(уо7 ноис правногть.

2. Уп);|р. 1ЯК)1иля программ,) F1M2 .чна.чи- .чируот ооотснпио упранляюпюй Н1,(холппн 111ННЫ, а нмонно цопи готопиости. дми R (отова к пволу информации, го она упа манливаот триггор 13 готовности Р)мола в состояпио «1. При этом ВМ2 выставляот на информационном входе слово инфо)ма- ции, котороо чореч блок I поступаот на )рмационный вхол первого рогистра 2 и по)олаот по управляющему в.холу cm нал «Данные установлены. Этот сигнал чо рез элемент И 3 поступает на Е1чол за имей первою пн(и)рмапион11огч) ()е(ист)а 2 и производит загшсь информапии, н.чхолч пюйся на информационном входе. От повременно с этим триггер II готопно (и вывода данных сигналом «/1анмые устанои лены устанавмивается в состояние г I

ВМ1 с П() канальпого пикла ofifiaiuMBaoT сосгоярню погкм пор вого выхода коммутатора 9. При этом, если в первый информапионнь 1Й регист) 2 записана информация. ВМ1 производит ее ввод с помощью канального цикла . описанногг) выше.

В режиме «Диагностика со стороны fiMI устройство pafioTaeT следующим .

Правильность прохождения информации контролируется при помощи кана, 1ьньгх циклов «Вывод и . FiMl в адресной части цикла «Вывод передает по входу-нь1Х()ду устройства адресное слово и вырабатьпчает сигнал СИЛ. Узел 15 л(мпиф)ации адреса дешифрует адрес и по сигналу ( ИЛ сигнал «ВыГ)с)р устройсгва запоминается н триггере 31 у.чла |Г), а младшие разряды адресного словав 1риггере 22 де1пи()ратора 14 упран. 1яи)Ц1их сигналов. ВМ1 снимает адресное слово, помешает на вход- выход устройства да)1ные и по r iynne входов устройства передаст сигнал .шод. Этот сигнал поступает на T)einii вход дешифратора 23 y.i. ia 14. 5 соответсг и(и с кодом, загшсанным в м. ьздших разрядах ад)есного . на пяюм выходе ;ienni(() ратора 23 появ. тотся сигнал. к(1то)ый через элем(-цт И 2Н поступает на вход за писн второго информапионного 12 регистра и производит запись и({)Opмaции. паходч- ШОЙСЯ на его ип(о|1мациоппом входе. Гдц на.1 с пятого вьгх()да дешифратора также посту паег на э:1емет и 24. с Fiыxoдa которого че1)ез э. 1еме1гт 25 задержки пост пас т па первый кана. п.ного передатчика L O который (|)о()мируот сигна.1 (.ИИ.

ВЛ11. получив си1иал (JHl. снимает сиг na. i «Вывод - . ус1 аповл1 ппь1е данные и сиг пал ( ИЛ. Ии())( рмацпя. записанная wi то )ой )ег ист) I L че|им псршлй коммутаюр 1Л, поступаот на сю выход Да.юо l )из

0

5

0

5

0

5

0

5

0

5

В0.1И1 никл лВвод. 1)и -(М)м К0.1. (ами сапнь.|й в м.юлших patpHiax а inci HIM и c.i ва. со(1Г1(О1сгв Т ш(члпм iu,i(i.i iciiniit pii- тора 23 .via 14. C.nrna.i с iiu i-ioMi ruj хола Л(ЧПИ({1ра1()|1а 23 .IOмeнI III . 7 посчупао па вхол ком 1 лагора I. п.ч пср вы1( вход iiefiBoii rjiynnbi э. |ем1 нмш И. П .i Данные. нахо.1Я1цисся па ее ичип н ноступакипие гула с nn np i;ini 4nni и выхода устройства, подакпся и K. iiia.i

принимас поредан1| 1о рапыцс им формации. ,и ализируот ( с и до.ьзсг ак.1Ю чепие о г1равпл1)Нос ТИ прохождения информа ПИИ че)ез вход-В1 1ход устройства, выходной комм тарор 7. второй ин()ормационн(.ц 1 ре 12. коммутатор 9.

fi режиме обмена информаци1м ) по прерываниям устройство работает следующим )бра.и)м.

Ишшиатор обменарн помог ательная ма|нина. Этот режим обмс На является для нее единственным режимом перо дачи информации. нроисхолит црн помощи кана. Ьного ц|1кда (о. 1 Однако при этом, код, передаваемый в младп1их разрядах адресиого слова, соответствует четвертому вь1ходу дешифратора 23 ла 14. При пс)яв.тении сигнала на четЕ)ертг)м вьгходе дешифратора 23 происходит запись ин||и)рма- ции во второй информациопньп регистр 12 -и установка триггера 19 прерывания бло ка Г) в состояние «I. Ири этом на втором выходе второго кгжмутатора 44 появ ляется сигнал прерывания программы, посту паюший в .

1ри ртеродаче ин4н)рмации с контро.чом правильности ее Г1рг)хождепия проиь водит канальньп цикл «Ввод этом код, записанный в младших (разрядах а.чресного сло1(а. соответствует П1естому выхо чу дешифратора 23 узла 14. ( дильз.ч i шестого выхода депшфратора 23 чере элемент ИГ. 27 поступает на третий уп 1ар ЛЯК11ц)1Й вход коммутатора 9, в )м сле.чует па первы(1 вход первой группы элемеипш И. 1И 51. Ири этом даппые, находяпиич я на ic нгором входе и поступающие ту.ча с иыхо.ча то рого ип(1Ормационного рсгист а 12 черт i первый KOMMV TaTfip 43, (инлхпакм в капа.) ВЛА1. ВМI принимает nepcM, ей информацию и на оспове I e ana .че.1ает заклк чепне о П(1ав11. 1ьности ее прпхончдо- ния.

. по.тучив сигпа.ч nprpi-П ; мает гюреданныо .чаним от по п)авляк)шем вчо.г. с;| па.1 Данш.ю п|1ипи ы -. кокцмли на третий б.кжа ti ii;ia: ii навлииаст триггер I l прсрын iHir.i not- . остоЯП11е (.1 i И нициа I op ,i i

iiMina

И I ПрИПЯ ,1 lU h . . )1,|пании. Л.чрес 1 д-к||)|м npi;; .- noiTyn.ieHnn T ie6oii,iiiM4 iipi j i .и.

H;IH вывод информации различен и зани- сан в дешифраторе 41 адреса узла 17. При работе в режиме прерываний ВМ1 во время кана,тьног ) цикла «Вывод производит запись кодов в рег истр 16 состояния, разрешающих ВМ1 ввод или вывод информации в peжflмe прерываний. При этом на первый в.ход элемента И 34 узла 17 поступает потенциал, разрец аю1ций или запрещающий работу BMI по вводу информации в режиме прерываний, а на первый элемент И 37 по выводу информации. ВМ2 передает требова)1ие црерывания на вывод информации сигналом «Данные приняты, который через блок I и элемент ИЛИ 48 блока 8 поступает на третий вход блока Н управления и устанавливает триггер 35 требования прерывания в состояние «О.

Сигнал требования прерывания с выхода триггера 35 через элемент И 37, триггер 38 предоставления прерывания и элемент И 40 поступает на второй вход канального iie)e- датчика 20, с выхода которого поступает в канал .

Процессор BiMl вырабатывает сигнал предостав.ления прерывания (ПИР). Сигнал ППР поступает на второй вход дешифратора 14 управляющих сигналов и первый вход узла 17. В узле 17 он через мент ПН 39 поступает на нулевой вход три1гера 38 предоставления прерывания, который запо.минает требование прерывания. С выхода элемента И 36 сигнал «1 поступает па единичный триггера 35, устанавливая его в состояние «I. Дешифратор 41 адреса помешает адрес вектора на первый выход узла 17 векторного прерывания, связанного с входом-выходом ВМ1. В деп1ифраторе 14 управляющих сигналов сигна;| ППР поступает па четвертый вход элемента И 24, с выхс)да KOTOpoi o через элемепт 25 задержки поступает па первый вход канального передатчика 20. Канальный передатчик 20 формирует сигна; СИП, свидетельствующий о том, что адрес помешен в канал. ВМI принимает вектор прерывания, сни.мает сиг нал ППР и переходит к обс.пуживанию под- прог раммы прерывания по выводу информации.

При передаче информации в ВМ1 по прерыванию устройство работает следующим образо.м.

выставляет слово информации и передает сигпал «Лан)1ые установлены. Слово информации записывается в первый информационный регистр 2. триггер 11 готовности вывода устанавливается в состояние «I, в блоке 6 управления триггер 32 требования прерывания устанавливается также в состояние «I. Сигнал с выхода триггера 32 требования прерывания через эле- .мент П 34 поступает на триггер 38. с первого единичного выхода которого поступает на первый вход элемепта И 40 и на

второй вход дешифратора 41 адреса, а со вто- рог о нулевого выхода на второй вход элемента И 33. С прямого выхода элемента И 40 сигнал ППР поступает па второй вход канального передатчика 20. с выхода которого поступает в канал ВМ1. Далее повторяются описанные процессы, но при этом формируется вектор прерывания на ввод информации.

10

Формула изобретения

I. Устройство для сопряжения разно- типны.х вычислительных машин по авт. св. № 1257651, отличающееся тем, что, с целью расп ирения функциональных возможностей 5 устройства и повышения достоверности обмена ЭВМ за счет аппаратной упаковки разрядов слов данных и взаимного независимого двустороннего контроля канала сопряжения, в него введены третий регистр, деп1ифратор, двунаправленный коммутатор и

МUI

четвертый элемент И, приче.м первый информационный вход .мультиплексора подключен к выходу первого регистра, второй информационный вход мультиплексора подключен к третьему информационному выходу

5 выходного коммутатора, управляюпшй вход мультиплексора соединен с единичным выходом триггера диагностики, выход мультиплексора подключен к информационному входу третьего регистра, нервый и второй входы четвертого элемента И соединены с

0 выходо.м записи в третий регистр блока канал1 ных приемопередатчиков и с выходо.м записи кода упаковки блока управ.чепия, выход четвертого элемента П подключен к входу записи третьего регист)а, выход которого соединен с входом деп1ифратора,

5 выход которого подключен к управляю- П1ему входу двунаправленного коммутатора, первый вход-выход двунаправленного коммутатора является информационным входом- выходом устройства, второй вход-выход дву

направленного коммутатора соединен с информационным входом-выходом выходного коммутатора, кроме того, в блоке управления седьмой выход деп1ифратора команд подключен к восьмо.му входу третье1Ч) элемента И и соединен с выходом записи

кода упаковки блока управ.тепия.

2. Устройство по п. 1, отличающееся тем, что двунаправленный коммутатор содержит матрицу HX Н двунаправленных ключей ( П-разрядность слова данных), причем первый вход-выход каждого ключа i-й строки (i-1, П) соединен с i-м разрядом первого информационного входа-выхода двуна- прав.ченного ко.ммутатора, второй вход- выход каждого ключа j-ro столбца (J-1, П) соединен с j-м разрядом второго информационного входа-выхода двунанравленнок)

ко.ммутатора, а управляющий вход каждого ключа подключен к управ. тюшему входу двунаправленного коммутатора.

ll

55

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения разнотипных вычислительных машин | 1984 |

|

SU1257651A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1179312A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Вычислительная система с холодным резервом | 2021 |

|

RU2771211C1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения болыиой ЭВМ высокой производительности с микроэвм при построении локальных вычислительных сетей. Цель изобретения заключается в расширении функциональных возможностей устройства и повышении достоверности обмена ЭВ.М за счет аппаратной упаковки разрядов слова данных и взаимного независимого двустороннего контроля канала сопряжения. С этой целью в устройство по авт. св. № 1257651 дополнительно введены мультиплексор, третий регистр, дешифратор, двунаправленный коммутатор и четвертый элемент И. Изобретение позволяет производить аппаратную упаковку разрядов слова данных, изменять которую можно в произвольном порядке. При этом задержка преобразования слова данных определяется только паразитными емкостями его устройства преобразования. Структура данного устройства позволяет производить коммутацию в произвольном порядке цепей входа-выхода устройства с цепями входа- выхода выходного ко.ммутатора, что позволяет значительно облегчить поиск их неисправностей. 1 з. п. ф-лы, 8 ил. I (Л

tput.S

5

L

«риг. f

SO

-j

L

LJ

N5

Я5

,J

Фиг.7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1984 |

|

SU1257651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-08-19—Подача