Изобретение относится к области электротехники, в частности к вторичным источникам питания, и может быть использовано в системах электропитания узлов информационно-измерительных систем и других радиотехнических устройств.

Целью изобретения является уменьшение пульсаций выходного напряжения.

На фиг. 1-3 представлены функциональные схемы соответственно предлагаемо- fo стабилизатора напряжения, логического блока и генератора пилообразного напря- |кения; на фиг. 4 - диаграммы, харак- феризующие работу стабилизатора напря- ения.

; Многофазный импульсный стабилизатор |1апряжения содержит параллельно соеди- Йенные силовые ячейки 1-4, включенные |иежду одноименными входным и выходным выводами, подключенные к выходным выводам сглаживающий конденсатор 5 и вход уз- |ia 6 сравнения, выход которого соединен С первыми входами компаратора 7 и ши- ротно-импульсного модулятора 8, генератор 9 Пилообразного напряжения, первый - третий выходы которого соединены соответст- 5енно с первым входом сумматора 10, вхо- |;iOM регистра 11 сдвига, вторым входом ком- Иаратора 7 и через ключ 12 с вторым вхо- дом сумматора 10, выход которого подключен к второму входу широтно-импульсного модулятора 8, выход компаратора 7 под- :ключен к управляющему входу ключа 12, логический блок 13, первые входы которого соединены с соответствующими выходами регистра 11 сдвига, второй вход - с Е ыходом н иротно-импульсного модулятора 8, третий вход - с выходом компа- |ратора 7, а выходы - с управляющими входами соответствующих силовых ячеек 1-4.

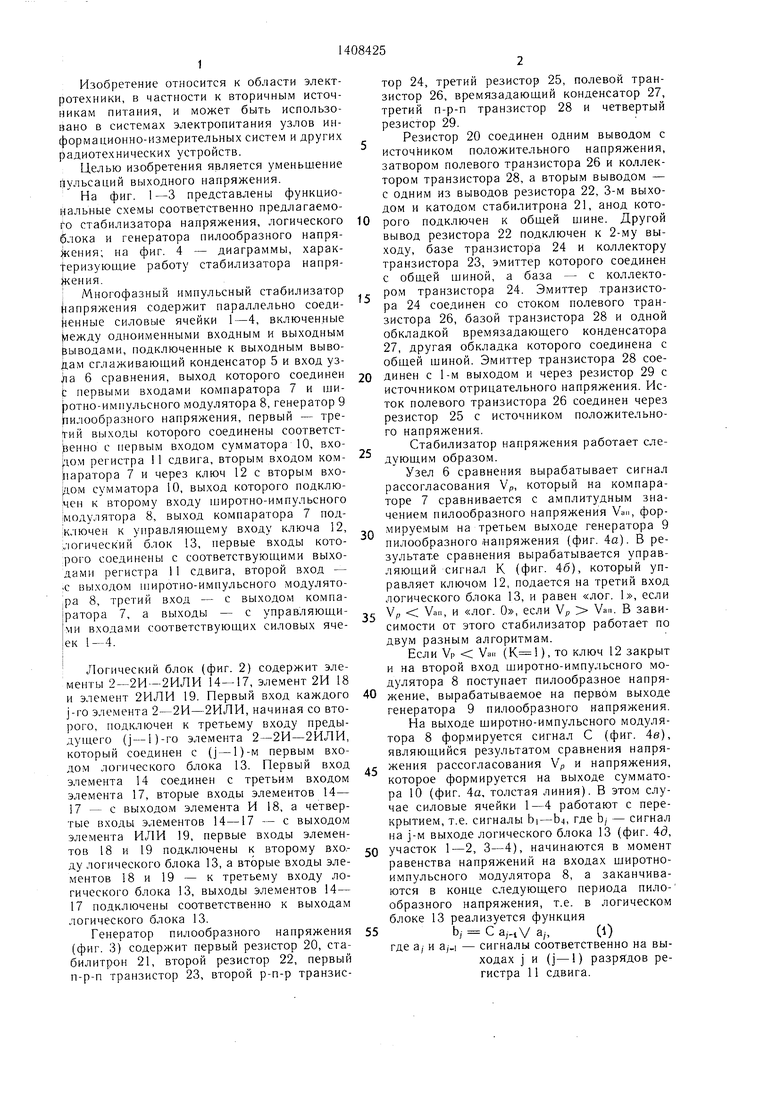

Логический блок (фиг. 2) содержит элементы 2- 2И-2ИЛИ 14-17, элемент 2И 18 и элемент 2ИЛИ 19. Первый вход каждого j-ro элемента 2-2И-2ИЛИ, начиная со второго, подключен к третьему входу преды- дупхего (J - 1)-го элемента 2-2И-2ИЛИ, который соединен с (J - 1)-м первым входом логического блока 13. Первый вход элемента 14 соединен с третьим входом элемента 17, вторые входы элементов 14- 17 - с выходом элемента И 18, а четвертые элементов 14-17 - с выходом элемента ИЛИ 19, первые входы элементов 18 и 19 подключены к второму вхо.- ду логического блока 13, а вторые входы элементов 18 и 19 - к третьему входу логического блока 13, выходы элементов 14- 17 подключены соответственно к выходам логического блока 13.

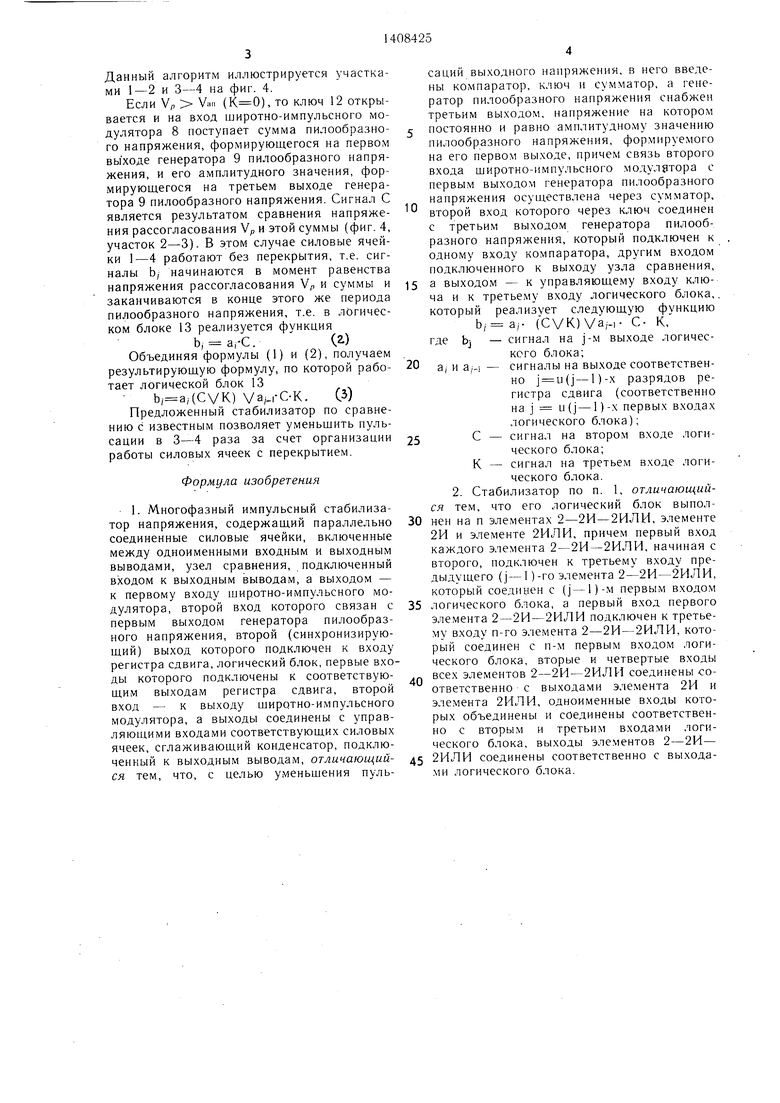

Генератор пилообразного напряжения (фиг. 3) содержит первый резистор 20, стабилитрон 21, второй резистор 22, первый п-р-п транзистор 23, второй р-п-р транзис

0

5

5

тор 24, третий резистор 25, полевой транзистор 26, времязадающий конденсатор 27, третий п-р-п транзистор 28 и четвертый резистор 29.

Резистор 20 соединен одним выводом с источником положительного напряжения, затвором полевого транзистора 26 и коллектором транзистора 28, а вторым выводом - с одним из выводов резистора 22, 3-м выходом и катодом стабилитрона 21, анод которого подключен к общей шине. Другой вывод резистора 22 подключен к 2-му выходу, базе транзистора 24 и коллектору транзистора 23, эмиттер которого соединен с общей шиной, а база - с коллекто ром транзистора 24. Эмиттер транзистора 24 соединен со стоком полевого транзистора 26, базой транзистора 28 и одной обкладкой времязадающего конденсатора 27, другая обкладка которого соединена с общей шиной. Эмиттер транзистора 28 сое0 динен с 1-м выходом и через резистор 29 с источником отрицательного напряжения. Исток полевого транзистора 26 соединен через резистор 25 с источником положительного напряжения.

Стабилизатор напряжения работает сле- дуюпхим образо.м.

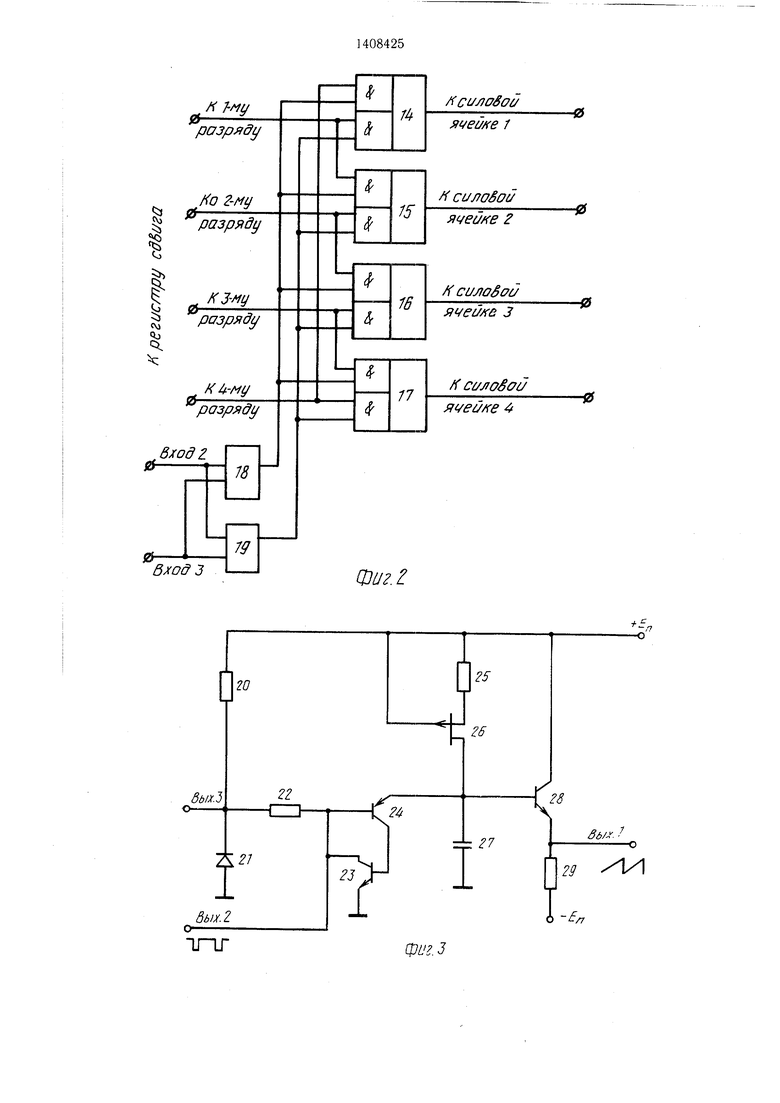

Узел 6 сравнения вырабатывает сигнал рассогласования Vp, который на компараторе 7 сравнивается с амплитудным значением пилообразного напряжения Van, форQ мируемым на третьем выходе генератора 9 пилообразного/напряжения (фиг. 4а). В результате сравнения вырабатывается управляющий сигнал К (фиг. 46), который управляет ключом 12, подается на третий вход логического блока 13, и равен «лог. 1, если

5 «лог. О, если Vp Van. В зависимости от этого стабилизатор работает по двум разным алгоритмам.

Если VP Van (К 1), то ключ 12 закрыт и на второй вход широтно-импульсного модулятора 8 поступает пилообразное напря0 жение, вырабатываемое на первом выходе генератора 9 пилообразного напряжения. На выходе щиротно-импульсного модулятора 8 формируется сигнал С (фиг. 4в), являющийся результатом сравнения напряс жения рассогласования Vp и напряжения, которое формируется на выходе сумматора 10 (фиг. 4а, толстая линия). В этом случае силовые ячейки 1-4 работают с перекрытием, т.е. сигналы bi-b4, где b/ - сигнал на J-M выходе логического блока 13 (фиг. 4с, участок 1-2, 3-4), начинаются в момент равенства напряжений на входах широтно- импульсного модулятора 8, а заканчиваются в конце следующего периода пило- образного напряжения, т.е. в логическом блоке 13 реализуется функция

by С a;-tV а;,(1)

где а/ и - сигналы соответственно на выходах j и (J-) разря дов регистра 11 сдвига.

0

Данный алгоритм иллюстрируется участками 1-2 и 3-4 на фиг. 4.

Если VP Van (), то ключ 12 открывается и на вход широтно-импульсного модулятора 8 поступает сумма пилообразного напряжения, формирующегося на первом выходе генератора 9 пилообразного напряжения, и его амплитудного значения, формирующегося на третьем выходе генератора 9 пилообразного напряжения. Сигнал С является результатом сравнения напряжения рассогласования V и этой суммы (фиг. 4, участок 2-3). В этом случае силовые ячейки 1-4 работают без перекрытия, т.е. сигналы Ь/ начинаются в момент равенства напряжения рассогласования Vp и суммы и заканчиваются в конце этого же периода пилообразного напряжения, т.е. в логическом блоке 13 реализуется функция

Ь, а,-С.(а)

Объединяя формулы (1) и (2), получаем результирующую формулу, по которой работает логической блок 13

(CVK) Va;-rC-K. СЗ)

Предложенный стабилизатор по сравнению с известным позволяет уменьщить пульсации в 3-4 раза за счет организации работы силовых ячеек с перекрытием.

Формула изобретения

. Многофазный импульсный стабилизатор напряжения, содержащий параллельно соединенные силовые ячейки, включенные между одноименными входным и выходным выводами, узел сравнения, подключенный входом к выходным выводам, а выходом - к первому входу широтно-импульсного модулятора, второй вход которого связан с первым выходом генератора пилообразного напряжения, второй (синхронизирующий) выход которого подключен к входу регистра сдвига, логический блок, первые входы которого подключены к соответствующим выходам регистра сдвига, второй вход - к выходу широтно-импульсного модулятора, а выходы соединены с управляющими входами соответствующих силовых ячеек, сглаживающий конденсатор, подключенный к выходным выводам, отличающийся тем, что, с целью уменьшения пуль0

саций выходного напряжения, в него введены компаратор, ключ и сумматор, а генератор пилообразного напряжения снабжен третьим выходом, напряжение на котором постоянно и равно амплитудному значению пилообразного напряжения, формируемого на его первом выходе, причем связь второго входа широтно-импульсного модулятора с первым выходом генератора пилообразного нанряжения осуществлена через сумматор, второй вход которого через ключ соединен с третьим выходом генератора пилообразного напряжения, который подключен к одному входу компаратора, другим входом подключенного к выходу узла сравнения, 5 а выходом - к управляющему входу ключа и к третьему входу логического блока,. который реализует следующую функцию

Ь,- а/. ( CVK) Va, С- К, где bj - сигнал на J-M выходе логического блока;

0 а, и а/-| - сигналы на выходе соответственно (j - 1)-х разрядов регистра сдвига (соответственно на j u(j-1)-х первых входах логического блока);

5С - сигнал на втором входе логического блока;

К - сигнал на третьем входе логического блока.

2. Стабилизатор по п. 1, отличающийся тем, что его логический блок выпол- 0 нен на п элементах 2-2И-2ИЛИ, элементе 2И и элементе 2ИЛИ, причем первый вход каждого элемента 2-2И-2ИЛИ, начиная с второго, подключен к третьему входу предыдущего (J - 1)-го элемента 2-2И-2ИЛИ, который соединен с (j-1)-м первым входом 5 логического блока, а первый вход первого элемента 2-2И-2ИЛИ подключен к третьему входу п-го элемента 2-2И-2ИЛИ, который соединен с п-м первым входом логического блока, вторые и четвертые входы всех элементов 2-2И-2ИЛИ соединены-соответственно с выходами элемента 2И и элемента 2ИЛИ, одноименные входы которых объединены и соединены соответственно с вторым и третьим входами логического блока, выходы элементов 2-2И- 5 2ИЛИ соединены соответственно с выходами логического блока.

0

ZW .,-

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Устройство для управления @ -фазным импульсным регулятором постоянного напряжения | 1990 |

|

SU1767669A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для измерения тока | 1984 |

|

SU1255944A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Однофазный инвертор напряжения с многофазной широтно-импульсной модуляцией | 2023 |

|

RU2804997C1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1989 |

|

SU1707609A1 |

| Импульсный стабилизатор напряжения | 1983 |

|

SU1121659A1 |

Изобретение относится к электротехнике, в частности к вторичным источникам питания, и .может быть использовано в система.х электропитания узлов информационно-измерительных систем и других радиотехнических устройств. Целью изобретения является уменьшение пульсаций выходного напряжения. Узел сравнения 6 вырабатывает сигнал рассогласования, который на компараторе / сравнивается с амп.1и;ул- ным значением пилообразного напряжения, поступающего с генератора пи. юобраз- ного напряжения (ГПН) 9. В результате сравнения вырабатывается управляющий сигнал, который управляет ключо.м 12 и подается на логический блок 13. На выходе ни- ротно-импульсного модулятора (ШИМ) 8 фор.мируется сигнал, являЮ1цийся результатом сравнения сигнала рассогласования от узла сравнения 6 и напряжения, которое получается на выходе сумматора 10. Когда ключ 12 заперт, силовые ячейки 1-4 работают с перекрытием. При этом логический блок 13 вырабатывает на своих выходах управляющие сигналы, которые начинаются в момент равенства напряжений на входах ШИМ 8, а заканчиваются в конце следующего периода пилообразного напряжения. При открыто.м ключе 12 силовые ячейки 1-4 работают без перекрытия. За счет организации работы силовых ячеек 1-4 с перекрытием стабилизатор позволяет существенно снизить пульсации выходно- г.о напряжения. 1 з.п. ф-лы. 4 ил. бхоЗ Т I I Звио СО сл 00 4 N3 СЛ Фиг.

т a

д

sn

| Шуваев Ю | |||

| Н., Виленкин А | |||

| Г | |||

| Многофазные импульсные стабилизаторы | |||

| - Сб | |||

| Электронная техника в автоматике | |||

| Под ред | |||

| Ю | |||

| И | |||

| Конева | |||

| М.: Советское радио, 1977, вып | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Многофазный импульсный стабилизатор напряжения | 1982 |

|

SU1092477A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-07-07—Публикация

1986-11-12—Подача