котором формируется двухуровневый 2g сигнал с крутыми фронтами при перехотолько на неинвертирующий вход опера- зо на информационный вход приемного ре- ционного усилителя 16, так как выход- гистра 13. Сигнал поступает также на ное (уопротивление вторичной обмотки , вход блока 14 синхронизации и затем линейного трансформатора 5 близко к на вход усилителя-ограничителя 21, в нулю и инвертирующий вход операционного усилителя 16 для сигнала с линии связи имеет нулевой потенциал. В результате на выходе операционного усилителя 16 присутствует только уси-ленный сигнал, приходящий с линии. В этом случае напряжение на инверсном о входе операционного усилителя 16 равно О, так как внутреннее сопро- тивление R „рр выходного каскада (передатчика) очень мало по сравнению с

.сопротивлением R j, резистора 15 согласования и сопротивлением R , линии связи. В то же время, так как RC R, то напряжение на единичном входе операционного усилителя и 5 (где Оду - напряжение, принимаемое с линии ). Напряжение на выходе операционного усилителя 16, обусловленное воздействием на его неинвертирующий вход

де его через нулевой уровень. Затем этот сигнал поступает на формирователь 22 синхроимпульсов, в котором формируются короткие импульсы на каждом- тактовом интервале и через элемент И 23 поступают-на тактируемый вход приемного регистра 13. В каждом байте первый бит всегда 1, после которого следует информаЦион45 ное слово. По этому единичному биту триггер 20 устанавливается в единичное состояние, и элемент И 23 пропускает тактовые импульсы, по которым приемный регистр 13 записьгоает инфор50 мационный байт. Счетчик 24 подсчитывает биты и по последнему биту каждого байта вьщает импульс байтовой синхронизации, по которому приемный регистр 13 осуществляет побайтовую

и

2 и„„„/2

50 мационный байт. Счетчик 24 подсчитывает биты и по последнему биту каждого байта вьщает импульс байтовой синхронизации, по которому приемный регистр 13 осуществляет побайтовую

g, равно UB(,,, К,,-и J . Изложенные выкладки справедли -1 д перезапись информации. вы при условии, когда ROC;RI; ,; Устройство позволяет передавать Rf..цифровые сигналы данных ЭВМ и друТаким образом, на выходе блока. 10 гую информацию на большие расстояния согласования присутствует только сиг- без промежуточных усилителей (по кокотором формируется двухуровневый сигнал с крутыми фронтами при перехона информационный вход приемного ре- гистра 13. Сигнал поступает также на вход блока 14 синхронизации и затем на вход усилителя-ограничителя 21, в

де его через нулевой уровень. Затем этот сигнал поступает на формирователь 22 синхроимпульсов, в котором формируются короткие импульсы на каждом- тактовом интервале и через элемент И 23 поступают-на тактируемый вход приемного регистра 13. В каждом байте первый бит всегда 1, после которого следует информаЦионное слово. По этому единичному биту триггер 20 устанавливается в единичное состояние, и элемент И 23 пропускает тактовые импульсы, по которым приемный регистр 13 записьгоает информационный байт. Счетчик 24 подсчитывает биты и по последнему биту каждого байта вьщает импульс байтовой синхронизации, по которому приемный регистр 13 осуществляет побайтовую

перезапись информации. Устройство позволяет передавать цифровые сигналы данных ЭВМ и друаксиальной паре с волновым сопротивлением 50 Ом на расстояния до 50 со- скоростью 1000 кбит/с), что обеспечивается высокой помехоустойчивостью устройства. При по одной физической паре передача может осуществляться как в полудуплексном режиме, так и в дуплексном, обеспечивая высокие экономические показатели систем цифровой связи.

Формула изобретения

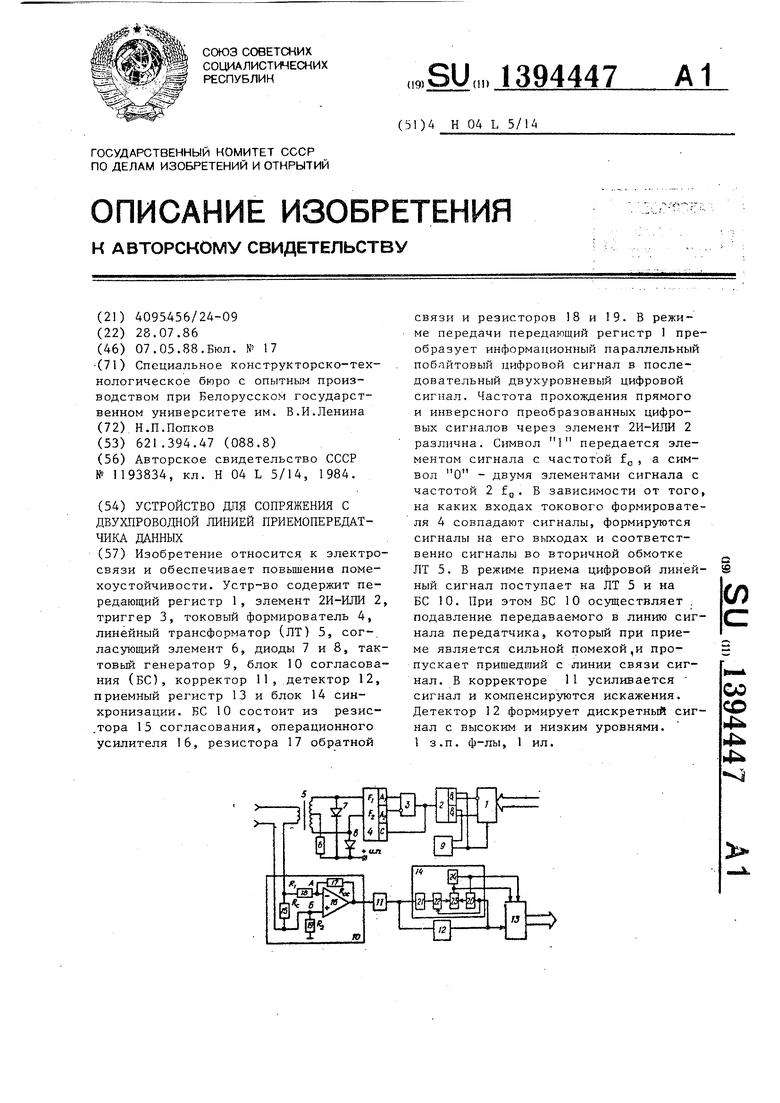

1. Устройство для сопряжения с двухпроводной линией приемопередатчика данных, содержащее линейный трансформатор, первый и второй выводы первичной обмотки которого соединены с анодами соответственно первого и второго диодов, катоды которых подключены к первому выводу согласующего элемента, второй вывод которого подключен к среднему вьшоду первич- ной обмотки линейного трансформатора триггер,блок синхронизации, блок согласования, тактовый генератор, первый выход которого соединен с тактовым входом передающего регистра, приемный регистр, при этом катод первого диода является опорным входом устройства, отличающееся тем, что, с целью повьппения помехоустойчивости, введены токовый формирователь, корректор, детектор и элемент 2И-ИЛИ, выход которого соединен с первым входом токового формирователя и с входом триггера, единичный и инверсный выходы которого подключены соответственно к второму и третьему входам токового формирователя, первый и второй выходы которого соединены соответственно с лервым и вторым вьгоодами первичной обмотки линейного трансформатора, первый вы

0

5

20

25

вод вторичной обмотки которого соединен с первым входом блока согласования, выход которого через корректор соединен с входом детектора и-с первым входом блока синхронизации, первый и второй выходы которого подключены соответственно к первому и второму входам приемного регистра, третий вход которого подключен к выходу детектора и к второму входу блока синхронизации, единичный и инверсный выходы передающего регистра соединены соответственно с первым и вторым входами элемента 2И-ИЛИ, третий и четвертый входы которого подключены соответственно к первому и второму выходам тактового генератора, при этом второй вьшод вторичной обмотки линейного трансформатора и второй , вход блока согласования подключены к линии связи.

5

0

2. Устройство по п.1, о т л и - чающееся тем, что блок согла-( сования содержит резистор обратной связи, резистор согласования, первый и второй резисторы и операционный усилитель, выход которого подключен к первому вьгводу резистора обратной связи, второй вьшод которого соеди- нен с инверсным входом операционного усилителя и с первым вьшодом первого резистора, второй вьгоод которого подключен к первому выводу резистора 5 согласования,второй вьшод которого подключен к первому выводу второго резистора и единичному входу операционного усилителя, выход которого является выходом блока согласования, первым и вторым входами которого являются соответственно первый и второй выводы резистора согласования, при этом второй вьшод второго резистора подключен к шине нулевого потенциала.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения с двухпроводной линией трактов приема и передачи | 1984 |

|

SU1193834A1 |

| Устройство для дуплексной цифровой связи | 1986 |

|

SU1408537A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| Устройство для сопряжения с двухпроводной линией связи трактов приема и передачи | 1987 |

|

SU1462390A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

Изобретение относится к электросвязи и обеспечивает повьшениа помехоустойчивости. Устр-во содержит передающий регистр 1, элемент 2И-ИЛИ 2, триггер 3, токовый формирователь 4, линейный трансформатор (ЛТ) 5, сог-. ласующий элемент 6, диоды 7 и 8, тактовый генератор 9, блок 10 согласования (БС), корректор 11, детектор 12, приемный регистр 13 и блок 14 синхронизации. БС 10 состоит из резис- .тора 15 согласования, операционного усилителя 16, резистора 17 обратной связи и резисторов 18 и 19. В режиме передачи передающий регистр 1 преобразует информационный параллельный побайтовый цифровой сигнал в последовательный двухуровневый цифровой сигнал. Частота прохождения прямого и инверсного преобразованных цифровых сигналов через элемент 2И-ИЛИ 2 различна. Символ 1 передается элементом сигнала с частотой „, а символ О - двумя элементами сигнала с частотой 2 fц. В зависимости от того, на каких входах токового формирователя 4 совпадают сигналы, формируются сигналы на его выходах и соответственно сигналы во вторичной обмотке ЛТ 5. В режиме приема цифровой линейный сигнал поступает на ЛТ 5 и на БС 10. При этом БС 10 осуществляет . подавление передаваемого в линию сигнала передатчика, который при приеме является сильной помехой,и пропускает пришедший с пинии связи сигнал. В корректоре 11 усиливается сигнал и компенсируются искажения. Детектор 12 формирует дискретный сигнал с высоким и низким уровнями. 1 3.п. ф-лы, 1 ил. с (Л оо со 4; 4;; 4

| Устройство для сопряжения с двухпроводной линией трактов приема и передачи | 1984 |

|

SU1193834A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-07—Публикация

1986-07-28—Подача