fff ..

; Л t t 1 i

f6

A.

J7

Ю

Изобретение относится к вьиисли- вльной технике и может использоваться в многопроцессорных системах для распределения заданий между процессорами «

Цель изобретения - расширение функ™ йиональных возможносте.й устройства Sa счет распределения заданий как по принципу дальнодействия, так и по принципу близкодействия.tO

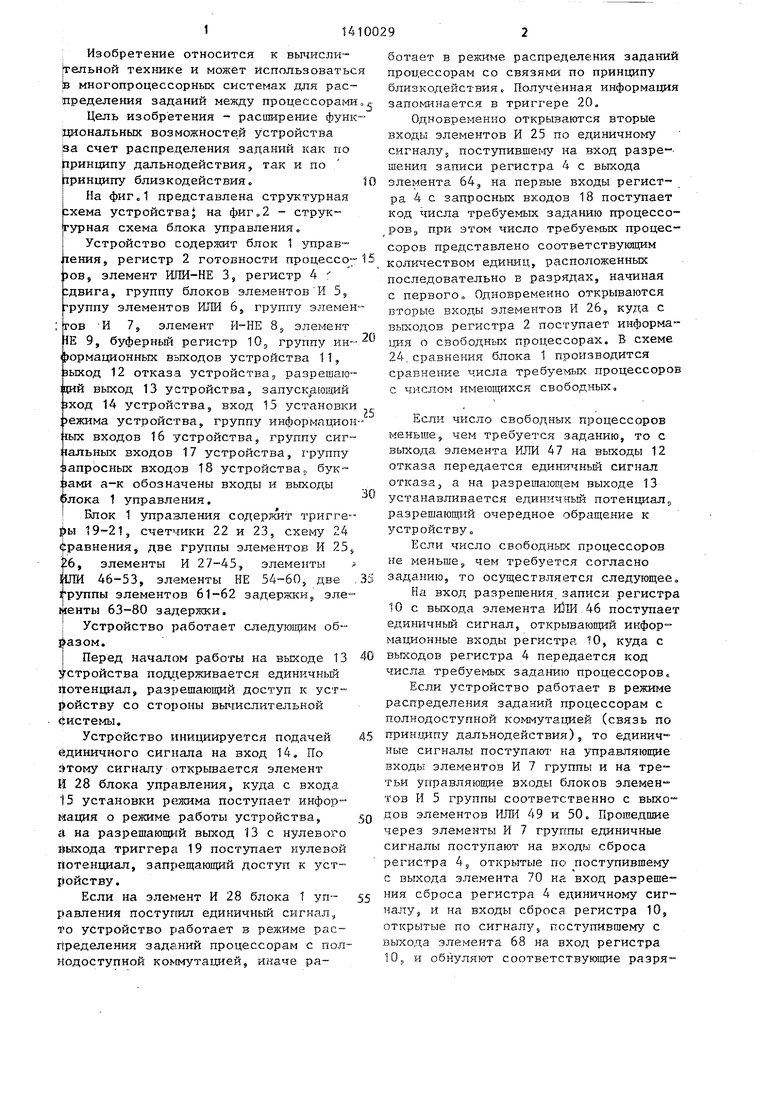

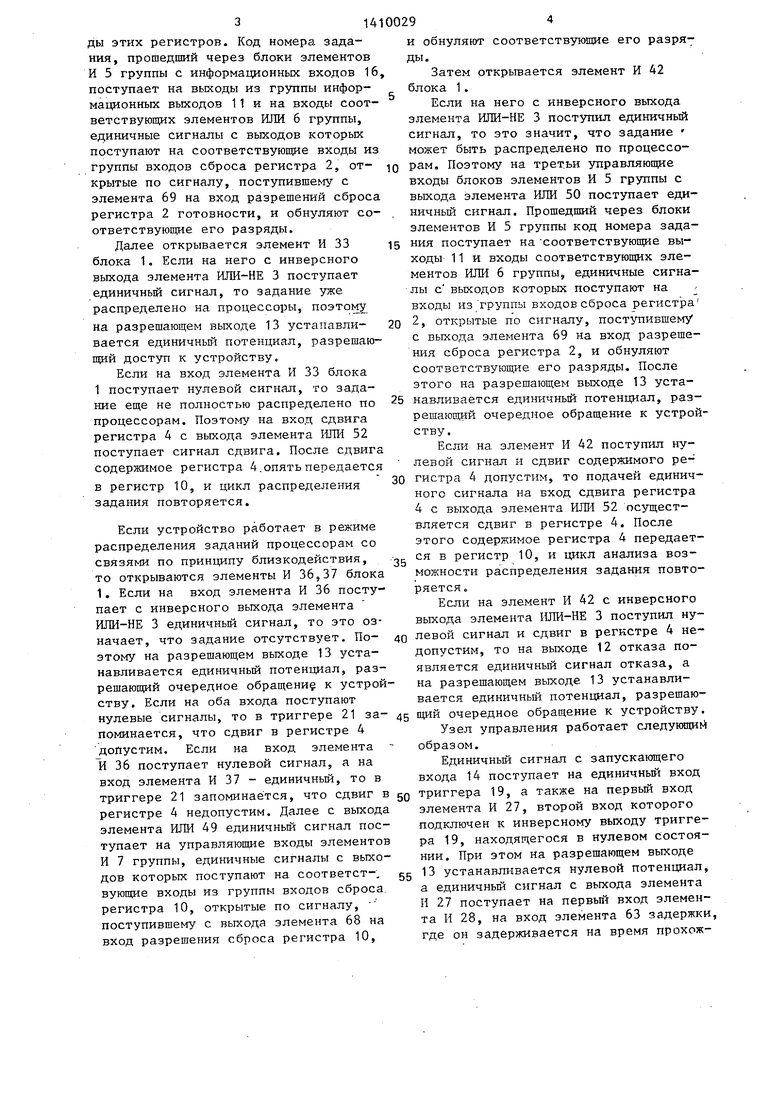

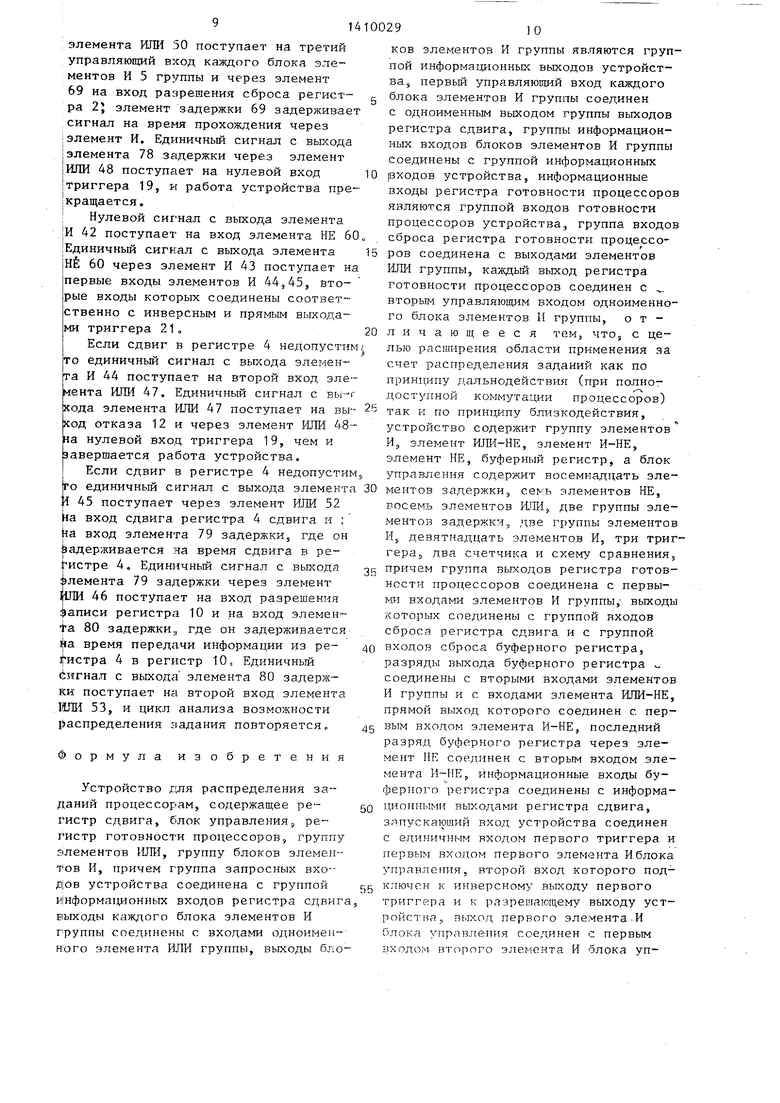

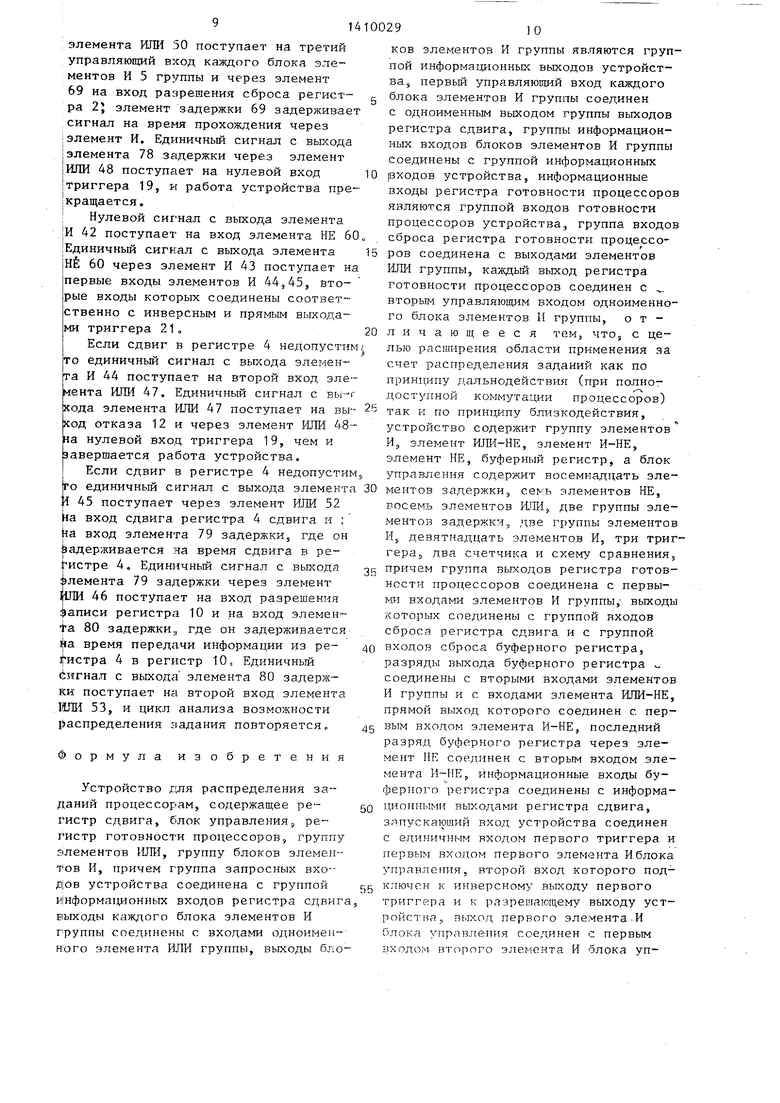

На представлена стрз турная зхема устройстваJ на фиг„2 - структурная схема блока управления,

Устройство содержит блок 1 управ- ,пения, регистр 2 готовности процессо-15 зов, элемент ИГМ-НЕ 3, регистр 4 : ;двига, группу блоков элементов И 5, группу элементов ИЛИ 6, группу элеменгов И 7j элемент И-НЕ 8., элемент IE 9, буферньш регистр Ю группу ин гоормационных выходов устройства 11, выход 12 отказа устройства, разрешаю11ЩЙ выход 13 устройства, запускаюш -ш зход 14 устройства, вход 15 установки :)ежима устройства, группу информацион пых входов 16 устройства, группу сигнальных входов 17 устройства, группу запросных входов 18 устройства„ бук- а-к обозначены входы и выходы (шока 1 управления.

Блок 1 упра зления содержит триггеры 19-21, счетчики 22 и 23, схему 24 сравнения, две группы элементов И 25, 26, элементы И 27-45, элементы )ШИ 46-53, элементы НЕ 54-60, две группы элементов 61-62 задержки, элементы 63-80 задержки.

Устройство работает следующим образом.

Перед началом работы на выходе 13 устройства пoд epживaeтcя единичньй йотенциал, разрешающий доступ к уст- 1 ойству со стороны вычислительной Системы,

Устройство инициируется подачей (Единичного сигнала на вход 14. По сигналу открывается элемент Н 28 блока управления, куда с входа 15 установки режима поступает информация о режиме работы устройства, и на разрешающий выход 13 с нулевого «ыхода триггера 19 поступает нулевой г(отенциал, запрещающий доступ к устройству ,

Если на элемент И 28 блока 1 уп™ р авления постуггил единичный сигнал, о устройство работает в режиме распределения заданий процессорам с пол- Иодоступной коммутацией, иначе ра.

я «

™ tO

15 . . 20

30

40

50

55

ботает в режиме распределения заданий процессорам со связями по принципу блиэкодействия,. Пол ченная информация запоминается в триггере 20„

Одновременно открываются вторые входы элементов И 25 по единичному сигналуS поступившему на вход разре- шения записи регистра 4 с выхода элемента 64, на первые входы регист- ра 4 с запросных входов 18 поступает код числа требуемых заданию процессо- дэовэ при этом число требуемых процессоров представлено соответствующим количеством единиц, расположенных последовательно в разрядах, начиная с первого Одновременно открываются вторые входы элементов И 26, куда с выходов регистра 2 поступает информация о свободных процессорах. В схеме 24,сравнения блока 1 производится сравнение числа требуемых процессоров с числом имеющихся свободных.

Если число свободных процессоров меньше, чем требуется заданию, то с выхода элемента ИЛИ 47 на выходы 12 отказа передается единигчный сигнал отказаJ а на разрешаюш;ем выходе 13 устанавливается единичный потенциал, разрешающТ Гй очередное обращение к устройству о

Если число свободных процессоров не меньше, чем требуется согласно заданию, то осуществляется следующее

На вход разрешения, записи регистра 10 с выхода элемента .46 поступает единичный сигнал, открывающий информационные входы регистра 10, куда с выходов регистра 4 передается код числа требуемых заданию процессоров.

Если устройство работает в режиме распределения заданий процессорам с полнодоступной ком1чутацией (связь по принтдипу дальнодействия), то единичные сигналы поступают на управляющие входы элементов И 7 группы и на третьи управляющие входы блоков элементов И 5 группы соответственно с выходов элементов ИЛИ 49 и 50. Прошедшие через элементы И 7 группы единичные сигналы поступают на входы: сброса регистра 4 открытые по поступивше 1у с выхода элемента 70 на вход разрешения сброса регистра 4 единичному сигналу, и на входы сброса регистра 10, открытые по сигналу, поступившему с выхода элемента 68 на вход регистра 10,, и обнуляют соответствующие разря31410029

ды этих регистров. Код номера задания, прошедший через блоки элементов И 5 группы с информационных входов 16, поступает на выходы из группы информационных выходов 11 и на входы соответствующих элементов РШИ 6 группы, единичные сигналы с выходов которых поступают на соответствующие входы из

и оонуля от соответствующие его разряды.

Затем открывается элемент И 42 блока 1.

Если на него с инверсного выхода элемента ИЛИ-НЕ 3 поступил единичкьй сигнал, то это значит, что задание может быть распределено по процессо- группы входов сброса регистра 2, от- ig рам. Поэтому на третьи зт1равляюш;ие крытые по сигналу, поступившему с входы блоков элементов И 5 группы с

элемента 69 на вход разрешений сброса регистра 2 готовности, и обнуляют соответствующие его разряды.

Далее открывается элемент И 33 блока 1. Если на него с инверсного выхода элемента ИЖ-НЕ 3 поступает единичньй сигнал, то задание уже распределено на процессоры, поэтому на разрешающем выходе 13 устанавливается единичный потенциал, разрешаю- 1щй доступ к устройству.

Если на вход элемента И 33 блока 1 поступает нулевой сигнал, то задавыхода элемента ИЛИ 50 поступает единичный сигнал. Прошедший через блоки элементов И 5 группы код номера зада-

15 НИН поступает на соответствуюшре выходы 11 и входы соответствующих элементов РШИ 6 группы, единичные сигналы с выходов которых поступают на входы из группы входов сброса регистра

20 2, открытые по сигналу, поступившему с выхода элемента 69 на вход разрешения сброса регистра 2, и обнуляют соответствующие его разряды. После этого на разрешающем выходе 13 устание еще не полностью распределено по 25 навливается единичный потенциал, развыхода элемента ИЛИ 50 поступает единичный сигнал. Прошедший через блоки элементов И 5 группы код номера зада-

НИН поступает на соответствуюшре выходы 11 и входы соответствующих элементов РШИ 6 группы, единичные сигналы с выходов которых поступают на входы из группы входов сброса регистра

2, открытые по сигналу, поступившему с выхода элемента 69 на вход разрешения сброса регистра 2, и обнуляют соответствующие его разряды. После этого на разрешающем выходе 13 уста

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения задач между процессорами | 1988 |

|

SU1532929A1 |

| Устройство для распределения заявок по процессорам | 1982 |

|

SU1121671A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1151966A1 |

| Устройство для распределения заданий процессорам | 1981 |

|

SU957211A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1413637A1 |

| Устройство для распределения задач между процессорами | 1989 |

|

SU1663611A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

процессорам. Поэтому на вход сдвига регистра 4 с выхода элемента ИЛИ 52 поступает сигнал сдвига. После сдвига содержимое регистра 4. опять передается в регистр 10, и цикл распределения задания повторяется.

Если устройство работает в режиме распределения заданий процессорам со связями по принципу близкодействия, то открываются элементы И 36,37 блока 1. Если на вход элемента И 36 поступает с инверсного выхода элемента ЙЛИ-НЕ 3 единичньй сигнал, то это означает, что задание отсутствует. Поэтому на разрешающем выходе 13 устанавливается единичный потенциал, раз30

решающий очередное обращение к устройству.

Если на элемент И 42 поступил нулевой сигнал и сдвиг содержимого регистра 4 допустим, то подачей единичного сигнала на вход сдвига регистра 4 с выхода элемента ИЛИ 52 осуществляется сдвиг в регистре 4. После этого содержимое регистра 4 передается в регистр 10, и цикл анализа возможности распределения задания повторяется с,

Если на элемент И 42 с инверсного выхода элемента ИЛИ-НЕ 3 поступил ну- 40 левой сигнал и сдвиг в регистре 4 недопустим, то на выходе 12 отказа по35

является единичный сигнал отказа, а решающий очередное обращение к устрой- на разрешающем выходе 13 устанавли- ству. Если на оба входа поступают вается единичный потенциал, разрешаю- нулевые сигналы, то в триггере 21 за- 45 очередное обращение к устройству.

Узел управления работает следующий

образом.

Единичный сигнал с запускающего

входа 14 поступает на единичный вход триггере 21 запоминается, что сдвиг в 50 триггера 19, а также на первьш вход регистре 4 недопустим. Далее с выхода элемента И 27, второй вход которого

поминается, что сдвиг в регистре 4 допустим. Если на вход элемента И 36 поступает нулевой сигнал, а на вход элемента И 37 - единичный, то в

элемента ИЛИ 49 единичный сигнал поступает на управляющие входы элементов И 7 группы, единичные сигналы с выходов которых поступают на соответст-, вующие входы из группы входов сброса регистра 10, открытые по сигналу, поступившему с выхода элемента 68 на вход разрешения сброса регистра 10,

решающий очередное обращение к устройству.

Если на элемент И 42 поступил нулевой сигнал и сдвиг содержимого регистра 4 допустим, то подачей единичного сигнала на вход сдвига регистра 4 с выхода элемента ИЛИ 52 осуществляется сдвиг в регистре 4. После этого содержимое регистра 4 передается в регистр 10, и цикл анализа возможности распределения задания повтояется с,

Если на элемент И 42 с инверсного выхода элемента ИЛИ-НЕ 3 поступил ну- евой сигнал и сдвиг в регистре 4 недопустим, то на выходе 12 отказа по

подключен к инверсному выходу триггера 19, находящегося в нулевом состоянии. При этом на разрешающем выходе 5g 13 устанавливается нулевой потенциал, а единичный сигнал с выхода элемента И 27 поступает на первьй вход элемента И 28, на вход элемента 63 задержки, где он задерживается на время прохож514400296

Жения сигнала через элемент И 28 и „ распределения задания по процес- флемент НЕ 54, на входы сброса скат- сорам с полнодоступной ком,утацией. чиков 22,23 и на элемент 64 задержки. Нулевой сигнал с выхода элемента tAe он задерживается на .время сброса и 28 поступает на вход элемента НЕ 54, фчетчиков 22 и 23, с выхода элемен- Единичный сигнал с выхода элемента Фа 64 единичный сигнал поступает на нЕ 54 проходит через элемент И 29 на 1.ХОД разрешения записи регистра И нулевой вход триггера 20, устанавли- сдвига, на входы первых элементов за- вал его в нулевое состояние, что со- лержки первой и второй групп 61,62, ответствует работе устройства в режи- где он задерживается на время прохож- ме распределения заданий по процессо- дения сигнала через элемент И и время рам со связями по принципу близкодей- с;рабатывания счетчика, и на первые ствия.

входы первых элементов И первой и i Если число требуемых заданию про- иторой групп 25,26 блока управления. 15 цессоров превышает количество свобод- Иа второй вход каждого элемента И ных процессоров, то нулевой сигнал И 25(26) группы поступает информация с выхода схемы 24 сравнения поступает С; одноименного входа из группы запрос- на вход элемента НЕ 55, Единичный сиг- гых входов 18 (группы выходов регист- нал с выхода элемента НЕ 55 проходит ра 2 готовности процессоров). Сигнал 20 через элемент И 32 и через элемент с выхода первого элемента И 25 (26), ИЛИ 47 и поступает на выход 12 отказа, группы поступает на счетньй вход сообщая об отказе. С выхода элемента счетчика 22(23). Единичный сигнал с ИЛИ 47 единичный сигнал через элемент Еыхода первого из элементов задержки ИЛИ 48 поступает на нулевой вход триг- 61(62) группы поступает на первый 25 гера 19, сбрасывая его в нулевое сос- Еход очередного элемента И 25 (26) тояние. При этом на разрешающий выход группы и на вход очередного элемента 13 с инверсного выхода триггера 19 пе- 61 (62) задержв:и группы и т.д. Еди- редается единичный потенциал, разре- иичньй сигнал с выхода последнего шая тем самым очередное обращение к элемента 61 (62) задержки группы пос- 30 устройству.

тупает на первый вход последнего эле- Если число требуемых заданию про- N:eHTa И 25(26) группы, разрешая про- цессоров не больше числа свободных вождение информации с последнего вхо- процессоров, то единичньм сигнал с ца из группы запросных входов 18 . выхода схемы 24 сравнения через эле- (группы выходов регистра 2 готовности 5 мент ИЛИ 46 поступает на вход разре- процессоров) на. счетный вход счетчи- шения записи регистра 10, а также на на 22(23). Единичньм сигнал с выхода первый вход элемента И 30 и на первый последнего элемента 62 задержки груп- вход элемента И 31, вторые входы копы поступает, также на вход элемента торых подключенысоответственно кпря- 65 задержки, где он задерживается на 40 мому иинверсному выходу триггера 20. прохождения сигнала через эле- Если устройство должно работать И и время суммирования в счетчи- в режиме распределения заданий по к. С выхода элемента 65 задержки процессорам с полнодоступной коммута- еДиничный сигнаа поступает на управ- цией, то единичный сигнал с выхода лйющий вход схемы 24 сравнения, разре-45 элемента И 30 поступает через элемент Ш&.Я сравнение числа требуемых заданию ИЛИ 49 на входы элементов И 7 группы,че- процессоров, находящегося в счетчике рез элемент ИЛИ 50 - на третьи управляю- 22, с числом свободных процессоров, щие входы блоков элементов И 5 группы и находящимся в счетчике 23. Одновремен- через элемент ИЛИ 51 и элемент 70 задбр- но сигнал с выхода элемента 65 задерж-5о жки,где он задерживается на время про- кй поступает на вход элемента 66 за- хождения сигнала через элемент И. Еди- держки, где он задерживается на время ничный сигнал с выхода элемента срабатывания схемы сравнения,ИЛИ 49 (50) поступает также на вход

Единичный сигнал с выхода элемента элемента 68(69) задержки, где он за- И 28, второй вход которого подключен 55 держивается на время прохождения сиг- к входу 15 установки режима, поступа- нала через элемент И с выхода , на единичный вход триггера 20, пе- мента 68 (69) единичный сигнал посту- рВводя его в единичное состояние, что пает на вход разрешения сброса регист- соответствует работе устройства в ре- ра Ю (2). Кроме того, единичный сиг7 1

нал с выхода элемента И 30 поступает на первьн вход элемента 67 задержки, где он задерткивается на время сброса в регистре 4 и на время прохождения сигнала через схемы И, ИЛИ-НЕ и ИЛИ. С выхода элемента 67 задержки единич ньгй сигнал поступает на первьй вход элемента И 33 и на вход элемента 71 задержки, где он задерживается на время прохождения сигнала через элемент И и элемент НЕ.

Если на выходе элемента И 33 появляется единичный сигнал, . распределение задания уже завершилось, то он поступает на первый вход элемента ИЛИ 48, с выхода которого еди- ничньм сигнал поступает на, нулевой вход триггера 19, переводя его в нулевое состояние. При этом на разре- шающем выходе 13 устанавлиЕается еди ничньш потенциал, разрешая очередное обращение к устройству.

Нулевой сигнал с выхода элемента И 33 поступает на вход элемента НЕ 5 С выхода элемента НЕ 56 сигнал проходит через элемент И 34 и черезг элемент ИЛИ 52 поступает на вход сдвига регистра 4 сдвига. Едини

ный сигнал с выхода элемента И 34 пос-зо ИЛИ, через элемент И и время сброса тупает также на вход элемента 72 задержки, где он задерживается на время прохождения сигнала через элемент ШМ и время сдвига в регистре 4„ Единичный сигнал с выхода элемента 72 задержки поступает через элемент ИЛИ 46 на вход разрешения записи регистра 10 и на элемент 73 задержки, где он задерживается на время передачи информации из регистра 4 в регистр 10. Еди- Q поступает на второй вход элемента 76 ничный сигнал с выхода элемента 73 задержки, на четвертый вход элемента

регистра 10, и через элемент I-tTtti 49 - ка входы элементов И 7 группы. Единич ный сигнал с выхода элемента ИЛИ 49 через элемент 68 задержки поступает 2g также на вход разрешения сброса регистра 10, Нулевой сигнал с выхода элемента И 39 поступает на вход элемента НЕ 59. Единичный сигнал с выхода элемента НЕ 59 через элемент И 41

задержки поступает на первый вход элемента И 35, второй вход которого подключен к прямому выходу триггера 20. Единичный сигнал с выхода элемента g И 35 поступает на вторые входы элементов ИЛИ 49-51 и на второй вход элемента 67 задержки, и цикл распределения задания по процессорам повторяется. Если устройство должно работать в

режиме распределения заданий по процессорам со связями по принципу близ- кодействия, то единичный сигнал с вы1ШИ 49 и на нулевой вход триггера 21, где запоминается, при этом сдвиг в регистре 4 недопустим.

Единичный сигнал с выхода элемента 76 задержки подается на вход элемента 77 задержки, где он задерживается на время прохождения сигнала через элемент И, элемент НЕ, и на nepBbffi вход элемента И 42, второй вход которого подключен к инверсному выходу элемента ИЛ11-НЕ 3.

Единичный сигнал с выхода элемента И 42 поступает на третий вход элемента

хода элемента И 31 поступает на пер- 55 50 и на вход элемента 78 задержки, вый вход элемента ИЛИ 53. Единичный где он задерживается на время прохождения сигнала через элемент ИЛИ, через элемент И и время сброса регистра 2. Единичпьм с выхода

сигнал с выхода элемента ИЛИ 53 пос- тупает на первые входы элементов.

И 36,37 и на вход элемента 74 задержки, где он задерживается на время прохождения сигнала через элемент И и через элемент НЕ, Вторые входы элементов И 36,37 подключены соответственно к инверсным выходам элементов VJm-UE 3, И-НЕ 8,

Единичный сигнал с выхода элемента И 36 поступает через элемент PUBi 48 на нулевой вход триггера 19, сбрасывая его в нулевое состояние, чем завершается работа устройства.

Нулевой сигнал с выхода элемента И 36 поступает на вход элемента НЕ 57, сигнал с выхода элемента И 37 поступает на вход элемента НЕ 58, С выхода элемента НЕ 58 сигнал через элемент И 40 поступает на первьй вход элемента И 39„ Единичньш сигнал с выхода элемента И 38 поступает на второй вход, элемента И 39 и на вход элемента 75 задержки, где он задерживается на время прохолдденпя сигнала через элемент И и элемент НЕ.

Единичньш сигнал с выхода элемента И 39 поступает на единичньш вход триггера 21, на первьт вход элемента 76 задержки, где он задерживается на вре- ьш прохождения сигнала через элемент

ИЛИ, через элемент И и время сброса поступает на второй вход элемента 76 задержки, на четвертый вход элемента

о ИЛИ, через элемент И и время сброса Q поступает на второй вход элемента 76 задержки, на четвертый вход элемента

регистра 10, и через элемент I-tTtti 49 - ка входы элементов И 7 группы. Единичный сигнал с выхода элемента ИЛИ 49 через элемент 68 задержки поступает 2g также на вход разрешения сброса регистра 10, Нулевой сигнал с выхода элемента И 39 поступает на вход элемента НЕ 59. Единичный сигнал с выхода элемента НЕ 59 через элемент И 41

1ШИ 49 и на нулевой вход триггера 21, где запоминается, при этом сдвиг в регистре 4 недопустим.

Единичный сигнал с выхода элемента 76 задержки подается на вход элемента 77 задержки, где он задерживается на время прохождения сигнала через элемент И, элемент НЕ, и на nepBbffi вход элемента И 42, второй вход которого подключен к инверсному выходу элемента ИЛ11-НЕ 3.

Единичный сигнал с выхода элемента И 42 поступает на третий вход элемент

9

элемента HJHi 50 поступает на третий управляющий вход каждого блока элементов И 5 группы и через элемент 69 на вход разрешения сброса регистра 2} элемент задержки 69 задерживае сигнал на время прохождения через элемент И. Единичный сигнал с выхода элемента 78 задержки через элемент ИЛИ 48 поступает на нулевой вход триггера 19, и работа устройства пре (кращается.

I Нулевой сигнал с выхода элемента |И 42 поступает на вход элемента НЕ 6 |Единичный сигнал с выхода элемента НЕ 60 через элемент И 43 поступает н первые входы элементов И 44,45, вторые входы которых соединены соответственно с инверсным и прямым выходами триггера 21 „

Если сдвиг в регистре 4 недопусти то единичный сигнал с выхода элемента И 44 поступает на второй вход элемента ИЛИ 47. Единичный сигнал с выхода элемента ИЛИ 47 поступает на вЫ ход отказа 12 и через элемент ИЛИ 48 на нулевой вход триггера 19, чем и завершается работа устройства.

Если сдвиг в регистре 4 недопусти го единичный сигнал с выхода элемент Л 45 поступает через элемент ИЛИ 52 ia вход сдвига регистра 4 сдвига и ; ha вход элемента 79 задержки, где он Задерживается на время сдвига в ре- HiCTpe 4, Единичный сигнал с выхода Элемента 79 задержки через элемент iJlH 46 поступает на вход разрешения г аписи регистра 10 и на вход элемента 80 задержки,, где он задерживается а время передачи информации из ре- ij HCTpa 4 в регистр 10, Единичный йигнал с выхода элемента 80 задерл - 1Ш поступает на второй вход элемента 1ШИ 53, и цикл анализа возможности {распределения задания повторяется „

Формула изобретения

Устройство для распределения заданий процессорам, содержащее регистр сдвига, блок управления; регистр готовности процессоров, группу элементов ИЛИ, группу блоков элемен- И, причем группа запросных входов устройства соединена с группой и|нформаи1ионных входов регистра сдвига выходы каждого блока элементов И группы соединены с входами одноименного элемента ИЛИ группы, выходы блоО

0

5

0

0 ментов

ков элементов И группы являются группой информационньк выходов устройства, первый управляю1ций вход каждого блока элементов И группы соединен с одноименным выходом группы выходов регистра сдвига, группы информационных входов блоков элементов И группы соединены с группой информационных (ВХОДОВ устройства, информационные входы регистра готовности процессоров являются группой входов готовности процессоров устройства, группа входов сброса регистра готовности процессоров соединена с выходами элементов ИЛИ группы, каждый выход регистра готовности процессоров соединен с . вторым управляющим входом одноименного блока элементов 1 группы, отличающееся тем, чтОз с целью расширения области применения за счет распределения заданий как по принципу дальнодействия (при полнодоступной коммутации процессо ров) Ь так и по близкодействия,

устройство содержит группу элементов И, элемент ИЛИ-НЕ, элемент И-НЕ, элемент НЕ, буферный регистр, а блок управления содержит восемнадцать элезадержки, семь элементов НЕ, восемь элементов ИЛИ, две группы элементов задержки, две группы элементов И, девятнадцать элементов И, три триггера, два счетчика и схему сравнения, причем группа выходов регистра готовности процессоров соединена с первыми входами элементов И группы,- выходы которых соединен) с группой входов сброса регистра сдвига и с группой входов сброса буферного регистра, разряды выхода буферного регистра - соединены с вторыми входами элементов И группы и с входами элемента ИЛИ-НЕ, прямой выход которого соединен с первым входом элемента И-НЕ, последний разряд буферного регистра через элемент НЕ соединен с вторым входом элемента , информационные входы буферного регистра соединены с информационными выходами регистра сдвига, запускающий вход устройства соединен с единичным входом первого триггера и первым входом первого элемента И блока управле 1ия, второй вход которого подключен к инверсному выходу первого триггера и к разрешающему выходу устройства., выход первого элемента-И блока управления сое,инен с первым входом второго элемента И блока уп5

0

5

0

5

11

равления, с входом первого элемента задержки, с входами сброса первого и второго счетчиков и с входом второго элемента задержки, выход которого соединен с входом разрешения записи регистра сдвига, с входами первых элементов задержки первой к второй групп и с первьмн входами первых элементов И первой и второй групп блока управления, вторые входы элементов И первой и второй групп блока управления соединены соответственно с одноименными входами группы запросных входов устройства и с одноименными выходами группы выходов регистра готовности процессоров, выходы элемен- тов № первой и второй групп блока управления соединены со счетны-ми входами соответственно первого и второго счетчиков, выходы каждых элементов задержки первой и второй групп, кроме последних, соединены с входом следующего элемента задержки своей группы., выход последнего элемента задержки второй группы соединен с входом третьего элемента задержки, выход которого соединен с тактовым входом схемы сравнения и с входом четвертого элемента задержки, второй вход второго элемента И блока управления является входом установки режима устройства, выход второго элемента И блока управления соединен с единичным входом второго триггера и с входом первого элемента,НЕ блока управления, выход которого соединен с первым входом третьего элемента И блока управления, второй вход и выход которого соединены соответственно с выходом первого элемента задержки и с нулевым входом второго триггера, выход схемы сравнения соединен с входом второго элемента НЕ блока управления и с первыми входами первого элемента ИЛИ, четвертого и пятого элементов И блока управления, вторые входы четвертого и пятого элементов И соединены соответственно с прямьм и инверсным выходами второго триггера, выход первого элемента ИЛИ блока управления соединен с входом разрешения записи буферного регистра, выход второго элемента НЕ блока управления соединен с,первым входом шестого элемента И блока управления, второй вход и выход которого соединены соответственно с выходом четвертого элемента задержки и первым входом второго элемента ИЛИ блока упе, о и ввм41002912

равления, выход второго элемента ИЛИ соединен с выходом отказа устройства и с первым входом третьего элемента

g ИЛИ блока управления, выход третьего элемента ИЛИ соединен с нулевым входом первого триггера, вькод четвертого элемента И блока управления соединен с первыми входами четвертого,

10 пятого, шестого элементов ИЛИ блока управления и с первым входом пятого элемента задержки, выход четвертого элемента ИЛИ блока управления соединен с третьими входами элементов И

15 группы и с входом шестого элемента задержки, выход которого соединен с входом разрешения сброса буферного регистра, выход пятого элемента ИЛИ блока управления соединен с третьим

20 управляющим входом каждого блока элементов И группы и с входом седьмого элементгг задержки, выход которого соединен с входом разрешения сброса регистра готовности процессоров, вы(

25 ход шестого элемента блока управления соединен с входом восьмого -элемента задержки, выход которого соединен с входом разрешения сброса регистра сдвига, выход пятого элемен30 та задержки соединен с первым входом седьмого элемента И блока управления и входом девятого элемента задержки, . второй вход и выход седьмого элемента И блока управления соединены соот35 ветственно с инверсным выходом элемента ИЛИ-НЕ и с вторым входом третьего элемента ИЛИ блока управления, выход седьмого элемента И соединен с входом третьего элемента НЕ блока управления,

40 выход третьего элемента НЕ соединен с первым входом восьмого элемента И блока управления, второй вход и выход восьмого элемента И соединены соответственно с выходом девятого

45 элемента задержки и с первьм входом седьмого элемента ИЛИ блока управления, выход седьмого элемента 1ШИ соединен с входом сдвига регистра сдвига,выход восьмого элемента И через десятый

gQ элемент задержки соединен с вторым входом первого элемента ИЛИ блока управления и через одиннадцатый элемент. задержки с первым входом девятого элемента И, второй вход которого соеgg динен с прямьм выходом второго триггера, выход девятого элемента И соединен с вторыми входами четвертого, пятого и шестого элементов ИЛИ и с вторым входом пятого элемента задержки.

31410029

выход пятого элемента И блока управления соединб .н с первым входом восьмого элемента ИЛИ, выход которого соединен с пефвыми входами десятого и одиннадцатого элементов И ис входом

14

двенадцатого элемента задержки, втo- рые входы десятого и одиннадцатого элементов И блока управления соединены соответственно с

элемента ИЛИ-НЕ и с выходом элемента И-НЕ, выход десятого элемента И блока управления соединен с третьим входом третьего элемента ИЛИ и с входом четвертого элемента HEj выход которого соединен с первым входом двенадцатого элемента И, второй вход которого сое- динен с выходом двенадцатого элемента задержки, выход двенадцатого элемента И соединен с входом тринадцатого элемента задержки и с первым входом тринадцатого элемента И блока управления, выход одиннадцатого элемента И соединен через пятый элемент НЕ с первым входом четьфнадцатого элемента И, второй вход и выход которого соединены соответственно с выходом двенадцатого элемента задержки и с вторым входом тринадцатого элемента И, выход которого соединен с входом шестого элемента НЕ блока управления, с единичным входом третьего триггера, с информационным входом четырнадцатого элемента задержки и с третьим входом четвертого элемента KTDij выход шестого элемента НЕ соединен с первым входом пятнадцатого элемента И, второй вход которого соепятнадцатого элемента задержки и с первым входом шестнадцатого элемента И второй вход которого соединен с g инверсным выходом элемента ИЛИ-НЕ, выход шестнадцатого элемента И соединен с входом шестнадцатого элемента задержки, третьим входом пятого элемента ИЛИ и с входом седьмого элеменинверсным вьпсодом -ю . g, выход которого соединен с первым входом семнадцатого элемента И, второй вход которого соединен с выходом пятнадцатого элемента задержки, выход семнадцатого элемента И соеди15 нен с первыми входами восемнадцатого и девятнадцатого элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами третьего триггера, выход восемнадцатого .

20 элемента И блока управления соединен с вторым входом второго элемента ИЛИ блока управления, выход девятнадцатого элемента И блока управления соединен с входом семнадцатого элемента

25 задержки и с вторым входом седьмого элемента ИЛИ блока управления, выход семнадцатого элемента задержки соединен с третьим входом первого элемента ИЛИ блока управления и через восем30 надцатьгй элемент задержки с вторым

входом восьмого элемента ИЛИ блока управления, выходы первого и второго счетчиков соединены соответственно с первым и вторым входами схемы срав35 нения, выход шестнадцатого элемента задержки соединен с четвертым входом третьего элемента 1ШИ блока управления, второй вход i-ro (, . .. ,п) , (п - количество запросньп входов устдинен с выходом тринадцатого элемента

задержки, выход пятнадцатого элемента 40 ройства) элемента Р1 первой группы И соединен с четвертым входом четвертого элемента ИЛИ, с нулевым входом третьего триггера и с управляющим входом четырнадцатого элемента задержки, выход которого соединен с входом 45

соединен с выходом (i-1)-ro элемента задержки первой группы, второй вход i-ro элемента И второй группы соединен с выходом (i-1)-ro элемента задержки второй группы.

14

ройства) элемента Р1 первой группы

соединен с выходом (i-1)-ro элемента задержки первой группы, второй вход i-ro элемента И второй группы соединен с выходом (i-1)-ro элемента задержки второй группы.

Фи8.2

а

f

ff

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-09-04—Подача