Изобретение относится к вычислительной технике и может быть использовано при построении отказоустойчивых многопроцессорных вычислительных систем (ВС).

Цель изобретения - повышение оперативности диагностирования.

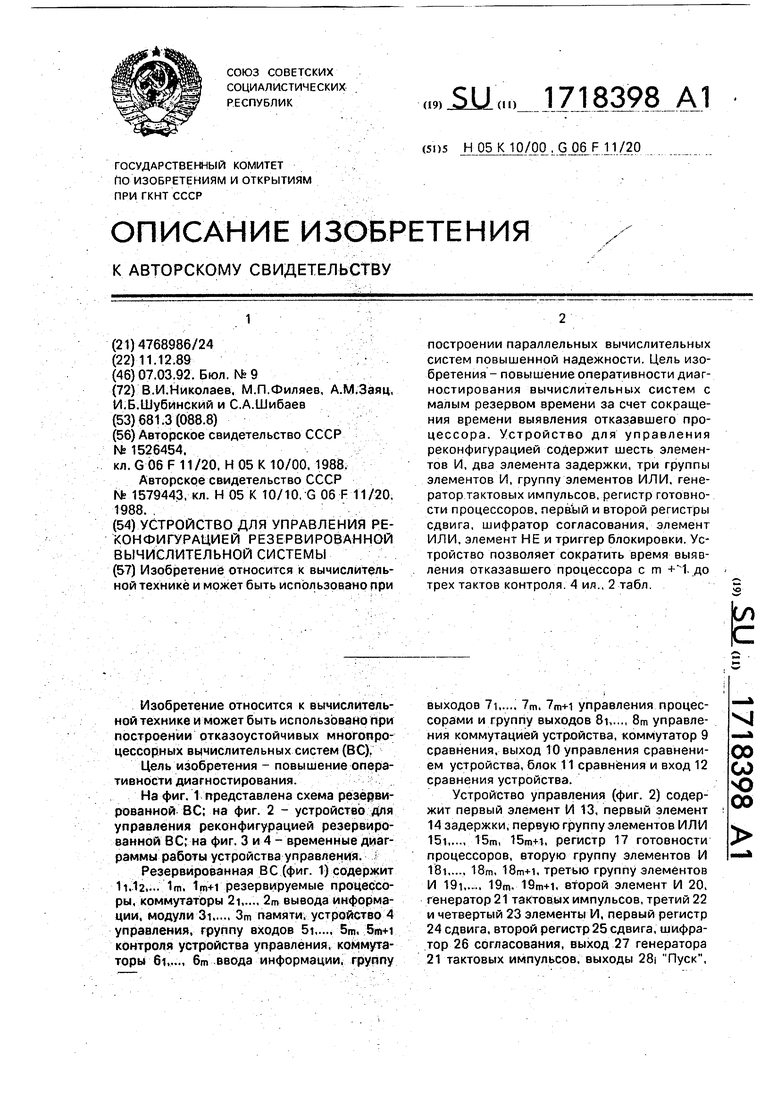

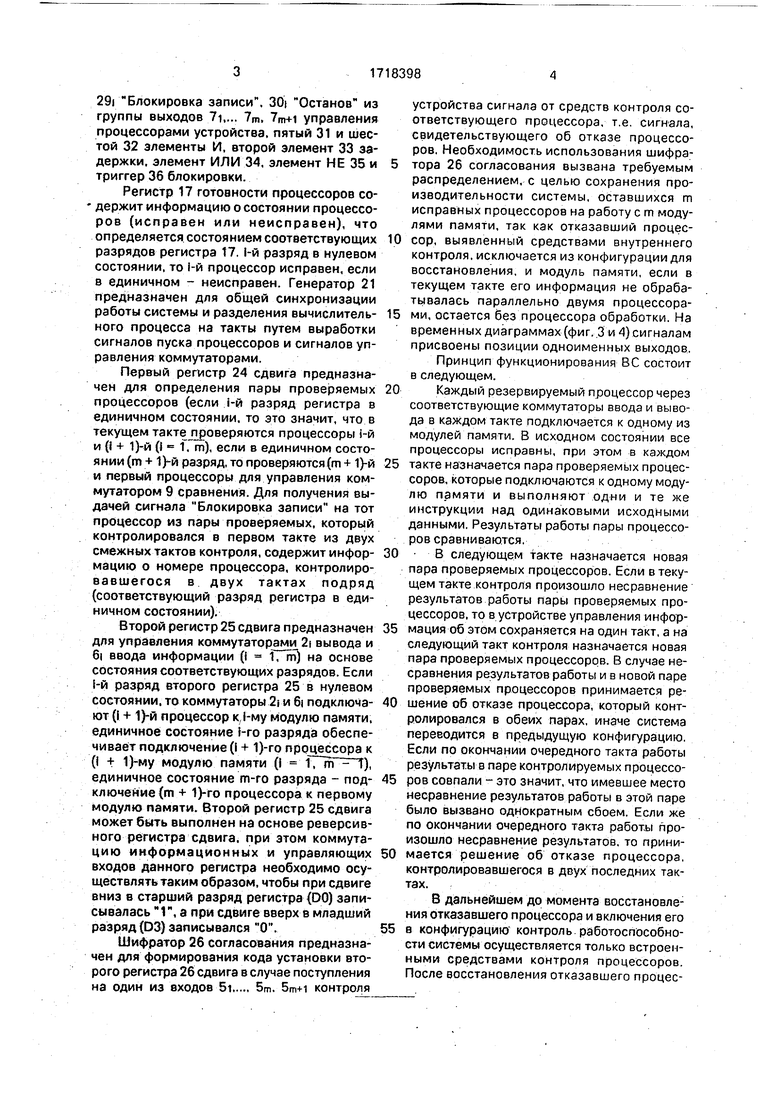

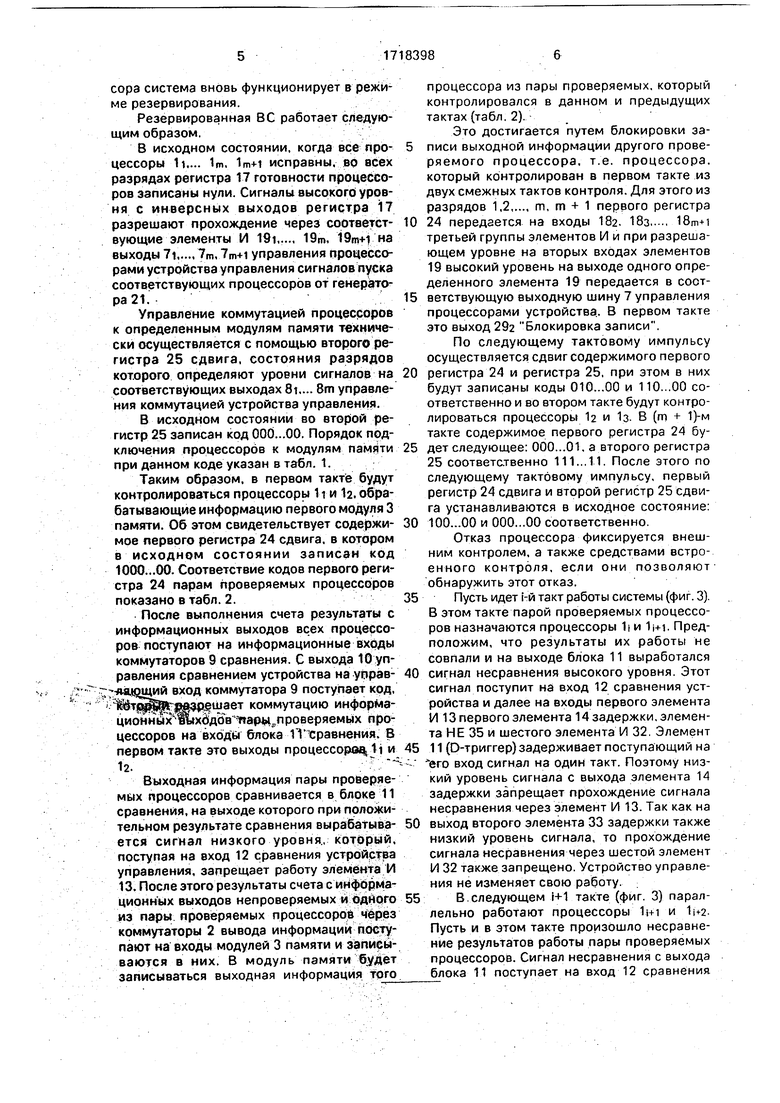

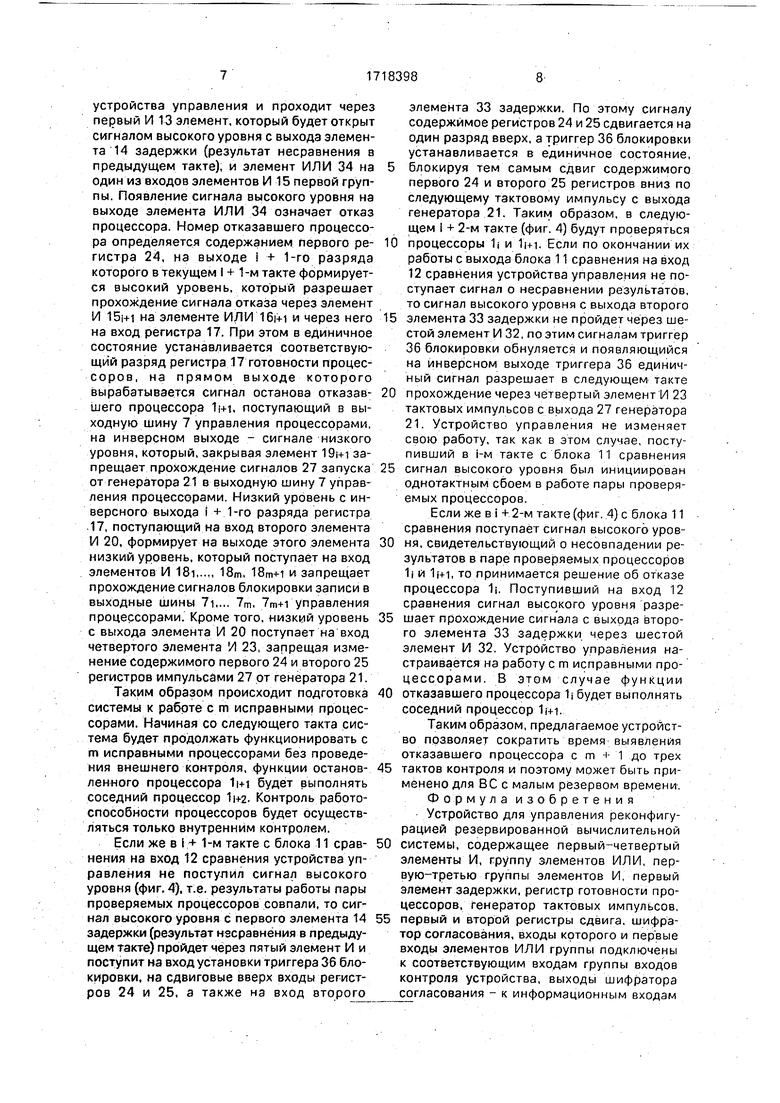

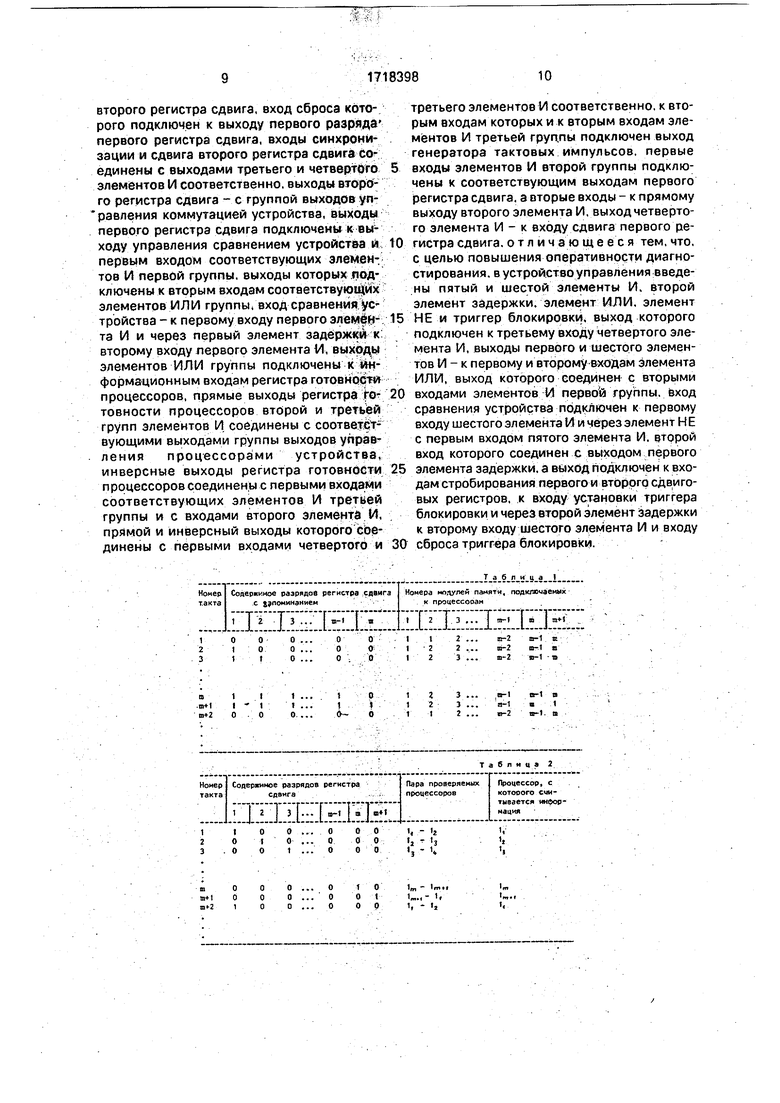

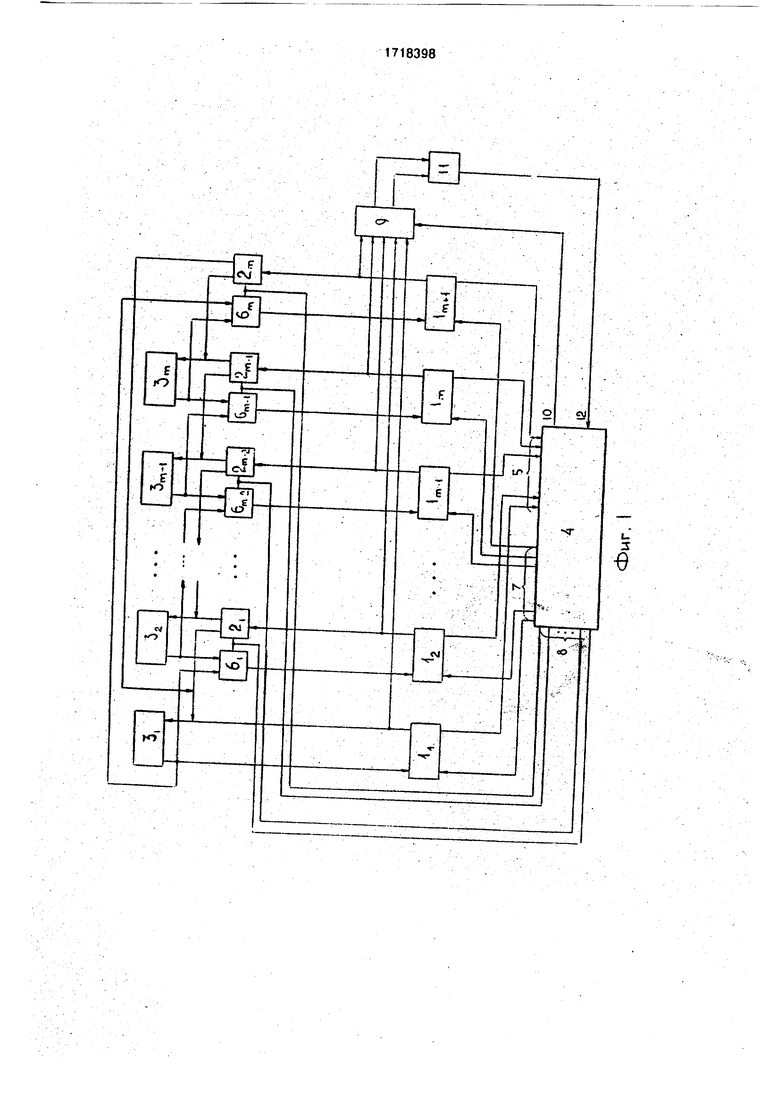

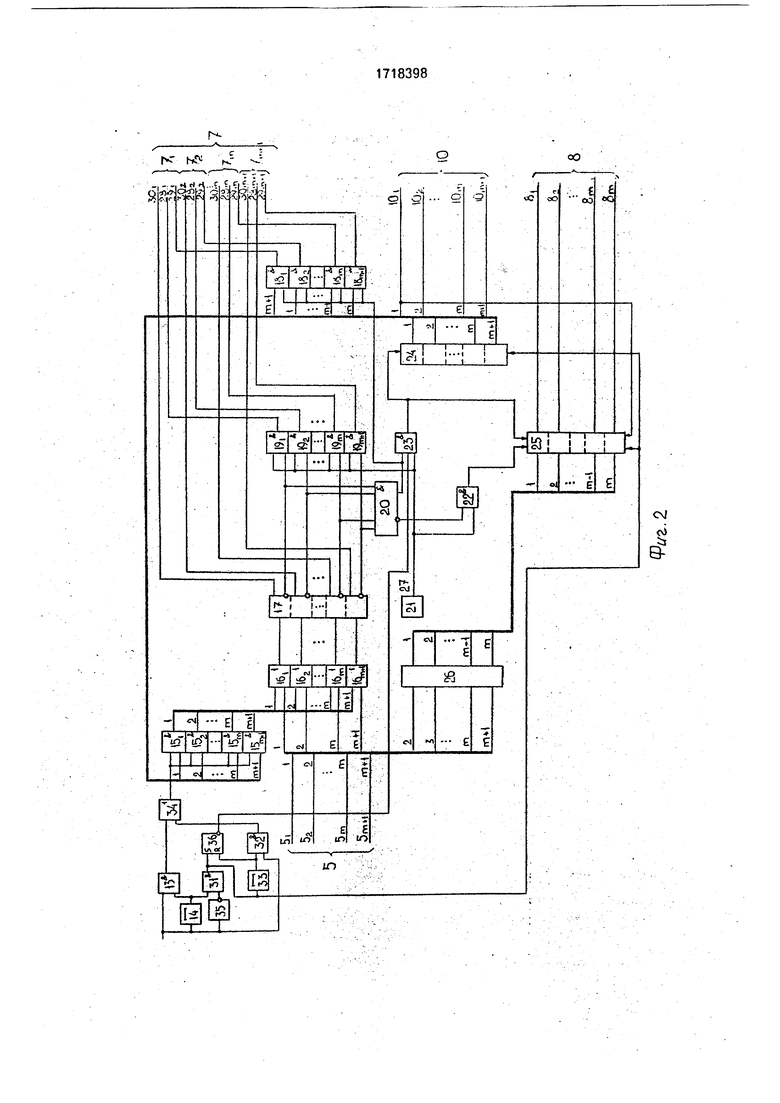

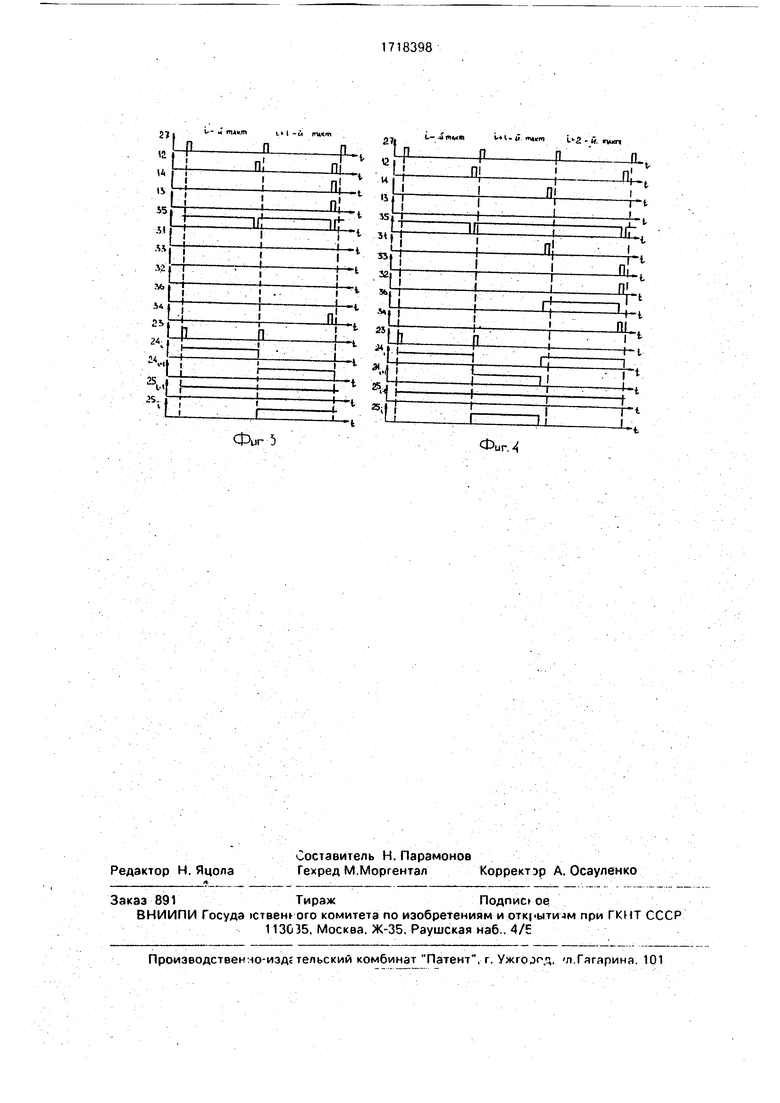

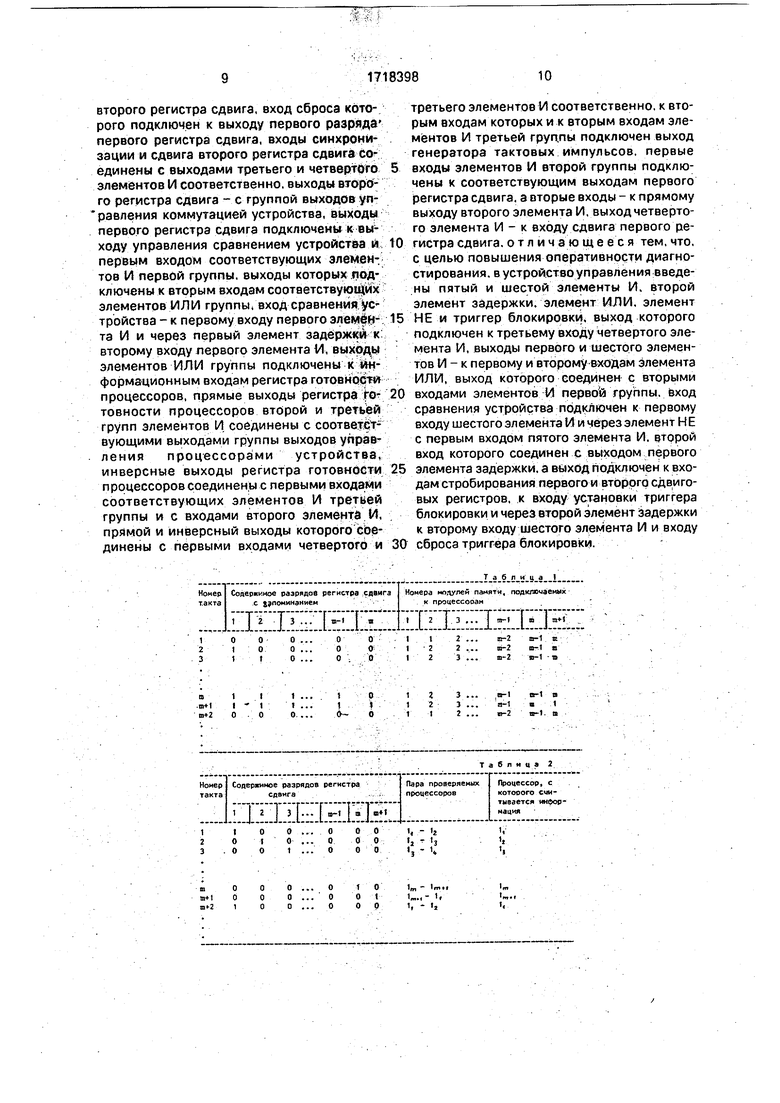

На фиг. 1 представлена схема резервированной ВС; на фиг. 2 - устройство для управления реконфигурацией резервированной ВС; на фиг. 3 и 4 - временные диаграммы работы устройства управления.

Резервированная В С (фиг. 1) содержит 1i.l2,- 1m. iro+i резервируемые процессоры, коммутаторы 2i,..., 2п вывода информации, модули 3i...., 3m памяти, устройство 4 управления, группу входов 5t,..., 5m. 5m+i контроля устройства управления, коммутаторы 6i,,.., 6m ввода информации, группу

выходов 7i,.... 7m. 7т+1 управления процессорами и группу выходов 8i,..., 8m управления коммутацией устройства, коммутатор 9 сравнения, выход 10 управления сравнением устройства, блок 11 сравнения и вход 12 сравнения устройства.

Устройство управления (фиг. 2) содержит первый элемент И 13, первый элемент 14 задержки, первую группу элементов ИЛИ 15i,..., 15m, 15nvH, регистр 17 готовности процессоров, вторую группу элементов И 18i,..., 18m, 18m+i, третью группу элементов И 19ь.,., 19m, 19т+1, второй элемент И 20. генератор 21 тактовых импульсов, третий 22 и четвертый 23 элементы И, первый регистр 24 сдвига, второй регистр 25 сдвига, шифратор 26 согласования, выход 27 генератора 21 тактовых импульсов, выходы 28i Пуск,

00

со

Ч) 00

29i Блокировка записи. 30| Останов из группы выходов 7i,... 7т, 7т+ управления процессорами устройства, пятый 31 и шестой 32 элементы И, второй элемент 33 задержки, элемент ИЛИ 34, элемент НЕ 35 и триггер 36 блокировки.

Регистр 17 готовности процессоров содержит информацию о состоянии процессоров (исправен или неисправен), что определяется состоянием соответствующих разрядов регистра 17. 1-й разряд в нулевом состоянии, то 1-й процессор исправен, если в единичном - неисправен. Генератор 21 предназначен для общей синхронизации работы системы и разделения вычислительного процесса на такты путем выработки сигналов пуска процессоров и сигналов управления коммутаторами.

Первый регистр 24 сдвига предназначен для определения пары проверяемых процессоров (если i-й разряд регистра в единичном состоянии, то это значит, что в текущем такте проверяются процессоры 1-й и (I + 1)-й (J f. m), если в единичном состоянии (т + 1)-й разряд, то проверяются (т + 1}-й и первый процессоры для управления коммутатором 9 сравнения. Для получения выдачей сигнала Блокировка записи на тот процессор из пары проверяемых, который контролировался в первом такте из двух смежных тактов контроля, содержит информацию о номере процессора, контролировавшегося в двух тактах подряд (соответствующий разряд регистра в единичном состоянии).

Второй регистр 25 сдвига предназначен для управления коммутаторами 2t вывода и 6i ввода информации (I 1, т) на основе состояния соответствующих разрядов. Если 1-й разряд второго регистра 25 в нулевом состоянии, то коммутаторы 2i и 6i подключают (I + 1)-й процессор к,i-му модулю памяти, единичное состояние 1-го разряда обеспечивает подключение (i + 1)-го процессора к (i + 1)-му модулю памяти (1 1, ггГ- 1), единичное состояние m-ro разряда - подключение (т + 1)-го процессора к первому модулю памяти. Второй регистр 25 сдвига может быть выполнен на основе реверсивного регистра сдвига, при этом коммутацию информационных и управляющих входов данного регистра необходимо осуществлять таким образом, чтобы при сдвиге вниз в старший разряд регистра (DO) записывалась Г, а при сдвиге вверх в младший разряд (D3) записывался О.

Шифратор 26 согласования предназначен для формирования кода установки второго регистра 26 сдвига в случае поступления на один из входов 51 5т. 5т-н контроля

устройства сигнала от средств контроля соответствующего процессора, т.е. сигнала, свидетельствующего об отказе процессоров, Необходимость использования шифратора 26 согласования вызвана требуемым распределением, с целью сохранения производительности системы, оставшихся m исправных процессоров на работу с m модулями памяти, так как отказавший процессор, выявленный средствами внутреннего контроля, исключается из конфигурации для восстановления, и модуль памяти, если в текущем такте его информация не обрабатывалась параллельно двумя процессорами, остается без процессора обработки. На

временных диаграммах (фиг. .3 и 4) сигналам

присвоены позиции одноименных выходов.

Принцип функционирования ВС состоит

в следующем.

Каждый резервируемый процессор через соответствующие коммутаторы ввода и вывода в каждом такте подключается к одному из модулей памяти. В исходном состоянии все процессоры исправны, при этом в каждом

такте назначается пара проверяемых процессоров, которые подключаются к одному модулю памяти и выполняют одни и те же инструкции над одинаковыми исходными данными. Результаты работы пары процессоров сравниваются.

В следующем такте назначается новая пара проверяемых процессоров. Если в текущем такте контроля произошло несравнение результатов работы пары проверяемых процессоров, то в устройстве управления информация об этом сохраняется на один такт, а на следующий такт контроля назначается новая пара проверяемых процессоров. В случае несравнения результатов работы и в новой паре проверяемых процессоров принимается решение об отказе процессора, который контролировался в обеих парах, иначе система переводится в предыдущую конфигурацию. Если по окончании очередного такта работы результаты в паре контролируемых процессоров совпали - это значит, что имевшее место несравнение результатов работы в этой паре было вызвано однократным сбоем. Если же по окончании очередного такта работы произошло несравнение результатов, то принимается решение об отказе процессора, контролировавшегося в двух последних тактах.

8 дальнейшем до момента восстановления отказавшего процессора и включения его

в конфигурацию контроль работоспособности системы осуществляется только встроенными средствами контроля процессоров. После восстановления отказавшего процессора система вновь функционирует в режиме резервирования.

Резервированная В С работает следующим образом.

В исходном состоянии, когда все про- цессоры Ь,... 1т, 1т-и исправны, во всех разрядах регистра 17 готовности процессоров записаны нули. Сигналы высокого уровня с инверсных выходов регистра 17 разрешают прохождение через соответст- вующие элементы И 19i,..., 19m, 19т+| на выходы 7i,..., 7m,7m-n управления процессорами устройства управления сигналов пуска соответствующих процессоров от генерэто- ра21.

Управление коммутацией процессоров к определенным модулям памяти технически осуществляется с помощью второго регистра 25 сдвига, состояния разрядов которого определяют уровни сигналов на соответствующих выходах 8i,... 8m управления коммутацией устройства управления.

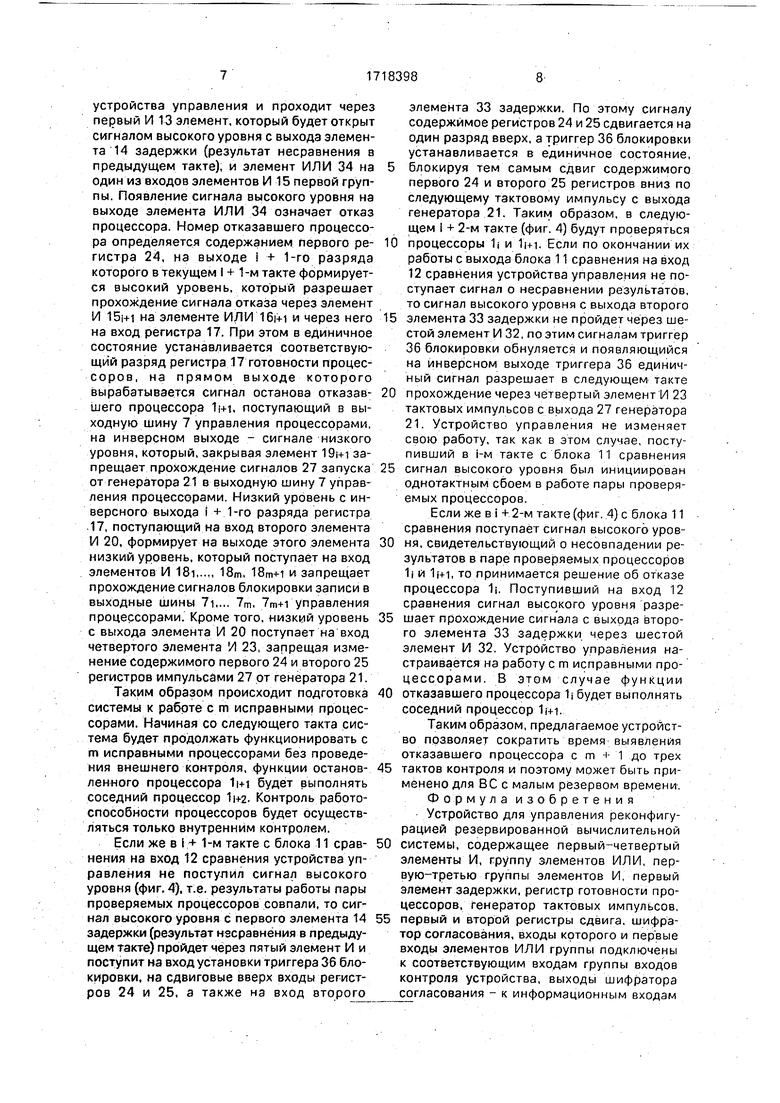

В исходном состоянии во второй регистр 25 записан код 000...00. Порядок подключения процессоров к модулям памяти при данном коде указан в табл. 1.

Таким образом, в первом такте будут контролироваться процессоры Ни 12. обрабатывающие информацию первого модуля 3 памяти. Об этом свидетельствует содержи- мое первого регистра 24 сдвига, в котором в исходном состоянии записан код 1000...00. Соответствие кодов первого регистра 24 парам проверяемых процессоров показано в табл.2.

После выполнения счета результаты с информационных выходов всех процессоров поступают на информационные входы коммутаторов 9 сравнения. С выхода 10 управления сравнением устройства на управ- ,ий вход коммутатора 9 поступает код, шает коммутацию информа- хддйв эдары проверяемых процессоров на входы блока TV Сравнения. В первом такте это выходы процессоров, 1i и

12. Выходная информация пары проверяемых процессоров сравнивается в блоке 11 сравнения, на выходе которого при положительном результате сравнения вырабатыва- ется сигнал низкого уровня., который, поступая на вход 12 сравнения устройства управления, запрещает работу элемента И

13.После этого результаты счета с информационных выходов непроверяемых и одного из пары, проверяемых процессоров через коммутаторы 2 вывода информации поступают на входы модулей 3 памяти и записываются в них. В модуль памяти будет записываться выходная информация того

ционных4

процессора из пары проверяемых, который контролировался в данном и предыдущих тактах (табл. 2).

Это достигается путем блокировки записи выходной информации другого проверяемого процессора, т.е. процессора, который контролирован в первом такте из двух смежных тактов контроля. Для этого из разрядов 1,2 т, т + 1 первого регистра

24передается на входы 182. 18з 18т+1

третьей группы элементов И и при разрешающем уровне на вторых входах элементов 19 высокий уровень на выходе одного определенного элемента 19 передается в соответствующую выходную шину 7 управления процессорами устройства. В первом такте это выход 292 Блокировка записи.

По следующему тактовому импульсу осуществляется сдвиг содержимого первого регистра 24 и регистра 25, при этом в них будут записаны коды 010...00 и 110...00 соответственно и во втором такте будут контролироваться процессоры 12 и 1з- В (т + 1)-м такте содержимое первого регистра 24 будет следующее: 000...01. а второго регистра

25соответственно 111...1.1. После этого по следующему тактовому импульсу, первый регистр 24 сдвига и второй регистр 25 сдвига устанавливаются в исходное состояние: 100...00 и 000...00 соответственно.

Отказ процессора фиксируется внешним контролем, а также средствами встроенного контроля, если они позволяют обнаружить этот отказ.

Пусть идет i-й такт работы системы (фиг. 3). В этом такте парой проверяемых процессоров назначаются процессоры 1i и 1j+i. Предположим, что результаты их работы не совпали и на выходе блока 11 выработался сигнал несравнения высокого уровня. Этот сигнал поступит на вход 12 сравнения устройства и далее на входы первого элемента И 13 первого элемента 14 задержки, элемента НЕ 35 и шестого элемента И 32. Элемент 11 (D-триггер) задерживает поступающий на его вход сигнал на один такт. Поэтому низкий уровень сигнала с выхода элемента 14 задержки запрещает прохождение сигнала несравнения через элемент И 13. Так как на выход второго элемента 33 задержки также низкий уровень сигнала, то прохождение сигнала несравнения через шестой элемент 1/1 32 также запрещено. Устройство управления не изменяет свою работу.

В.следующем i+1 такте (фиг. 3) параллельно работают процессоры 1i+i и Пусть и в этом такте произошло несравнение результатов работы пары проверяемых процессоров. Сигнал несравнения с выхода блока 11 поступает на вход 12 сравнения

устройства управления и проходит через первый И 13 элемент, который будет открыт сигналом высокого уровня с выхода элемента 14 задержки (результат несравнения в предыдущем такте), и элемент ИЛИ 34 на один из Входов элементов И 15 первой группы. Появление сигнала высокого уровня на выходе элемента ИЛИ 34 означает отказ процессора/Номер отказавшего процессора определяется содержанием первого регистра 24, на выходе i + 1-го разряда которого в текущем I + 1-мтакте формируется высокий уровень, который разрешает прохождение сигнала отказа через элемент И 15ц-1 на элементе ИЛИ 16н-1 и через него на вход регистра 17. При этом в единичное состояние устанавливается соответствующий разряд регистра 17 готовности процессоров, на прямом выходе которого вырабатывается сигнал останова отказавшего процессора 1|-н. поступающий в выходную шину 7 управления процессорами, на инверсном выходе .- сигнале низкого уровня, который, закрывая элемент 19i+i запрещает прохождение сигналов 27 запуска от генератора 2.1 в выходную шину 7 управления процессорами. Низкий уровень с инверсного выхода i + 1-го разряда регистра 17, поступающий на вход второго элемента И 20, формирует на выходе этого элемента низкий уровень, который поступает на вход элементов И 18i,..,, 18m, 18т-и и запрещает прохождение сигналов блокировки записи в выходные шины 7i,... 7m, 7m+i управления процессорами. Кроме того, низкий уровень с выхода элемента И 20 поступает на вход четвертого элемента И 23, запрещая изменение содержимого первого 24 и второго 25 регистров импульсами 27 от генератора 21.

Таким образом происходит подготовка системы к работе с m исправными процессорами. Начиная со следующего такта система будет продолжать функционировать с m исправными процессорами без проведения внешнего контроля, функции остановленного процессора 1i+i будет выполнять соседний процессор 1i+2. Контроль работоспособности процессоров будет осуществляться только внутренним контролем.

Если же в Г.-+ 1-м такте с блока 11 сравнения на вход 12 сравнения устройства управления не поступил сигнал высокого уровня (фиг. 4). т.е. результаты работы пары проверяемых процессоров совпали, то сигнал высокого уровня с первого элемента 14 задержки (результат нгсравнёния в предыдущем такте) пройдет через пятый элемент И и поступит на вход установки триггера 36 блокировки, на сдвиговые вверх входы регистров 24 и 25, а также на вход второго

элемента 33 задержки. По этому сигналу содержимое регистров 24 и 25 сдвигается на один разряд вверх, а триггер 36 блокировки устанавливается в единичное состояние, 5 блокируя тем самым сдвиг содержимого первого 24 и второго 25 регистров вниз по следующему тактовому импульсу с выхода генератора .21. Таким образом, в следующем I + 2-м такте (фиг. 4) будут проверяться

0 процессоры 1j и 1i+i. Если по окончании их работы с выхода блока 11 сравнения на вход 12 сравнения устройства управления не поступает сигнал о несравнении результатов, то сигнал высокого уровня с выхода второго

5 элемента 33 задержки не пройдет через шестой элемент И 32, по этим сигналам триггер 36 блокировки обнуляется и появляющийся на инверсном выходе триггера 36 единичный сигнал разрешает в следующем такте

0 прохождение через четвертый элемент И 23 тактовых импульсов с выхода 27 генератора 21. Устройство управления не изменяет свою работу, так как в этом случае, поступивший в i-м такте с блока 11 сравнения

5 сигнал высокого уровня был инициирован однотактным сбоем в работе пары проверяемых процессоров.

Если же в i + 2-м такте (фиг. 4) с блока 11 сравнения поступает сигнал высокого уров0 ня, свидетельствующий о несовпадении результатов в паре проверяемых процессоров 1i и 1j+i, то принимается решение об отказе процессора 1i. Поступивший на вход 12 сравнения сигнал высокого уровня разре5 шает прохождение сигнала с выхода второго элемента 33 задержки через шестой элемент И 32. Устройство управления настраивается на работу с m исправными процессорами. В этом случае функции

0 отказавшего процессора 1| будет выполнять соседний процессор 1й-1.

Таким образом, предлагаемое устройство позволяет сократить время выявления отказавшего процессора с m + 1 до трех

5 тактов контроля и поэтому может быть применено для ВС с малым резервом времени.

Формула изобретения Устройство для управления реконфигурацией резервированной вычислительной

0 системы, содержащее первый-четвертый элементы И, группу элементов ИЛИ, пер- вую-третью группы элементов И, первый элемент задержки, регистр готовности процессоров, генератор тактовых импульсов,

5 первый и второй регистры сдвига, шифратор согласования, входы которого и первые входы элементов ИЛИ группы подключены к соответствующим входам группы входов контроля устройства, выходы шифратора согласования - к информационным входам

второго регистра сдвига, вход сброса которого подключен к выходу первого разряда первого регистра сдвига, входы синхронизации и сдвига второго регистра сдвига соединены с выходами третьего и четвертого элементов И соответственно, выходы второго регистра сдвига - с группой выходов уп- равления коммутацией устройства, выходы первого регистра сдвига подключены к выходу управления сравнением устройства и первым входом соответствующих элементов И первой группы, выходы которых подключены к вторым входам соответствующих элементов ИЛИ группы, вход сравнения устройства - к первому входу первого элемента И и через первый элемент задержки к второму входу лервого элемента И, выходы элементов ИЛИ группы подключены к информационным входам регистра готовности процессоров, прямые выходы регистра № товности процессоров второй и третьей групп элементов И соединены с соответствующими выходами группы выходов управления процессорами устройства, инверсные выходы регистра готовности процессоров соединены с первыми входами соответствующих элементов И третьей группы и с входами второго элемента И, прямой и инверсный выходы которого соединены с первыми входами четвертого и

третьего элементов И соответственно, к вторым входам которых и к вторым входам элементов И третьей группы подключен выход генератора тактовых импульсов, первые

входы элементов И второй группы подключены к соответствующим выходам первого регистра сдвига, а вторые входы- к прямому выходу второго элемента И, выход четвертого элемента И - к входу сдвига первого регистра сдвига, о т л и ч а ю щ е ее я тем, что, с целью повышения оперативности диагностирования, в устройство управления введены пятый и шестой элементы И. второй элемент задержки, элемент ИЛИ, элемент

НЕ и триггер блокировки, выход которого подключен к третьему входу четвертого элемента И, выходы первого и шестого элементов И - к первому и второму входам элемента ИЛИ, выход которого соединен с вторыми

входами элементов И первой группы, вход сравнения устройства подключен к первому входу шестого элемента И и через элемент НЕ с первым входом пятого элемента И. второй вход которого соединен с выходом первого

элемента задержки, а вйход подключен к входам стробирования первого и второго сдвиговых регистров, к входу установки триггера блокировки и через второй элемент задержки к второму входу шестого элемента И и входу

сброса триггера блокировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Резервированная вычислительная система | 1989 |

|

SU1691991A1 |

| Спиральная однородная вычислительная структура | 1990 |

|

SU1741165A2 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1128267A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Устройство для контроля схем сравнения | 1984 |

|

SU1218386A1 |

| Устройство для обнаружения ошибок в блоках контроля процессора | 1980 |

|

SU903886A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении параллельных вычислительных систем повышенной надежности. Цель изобретения - повышение оперативности диагностирования вычислительных систем с малым резервом времени за счет сокращения времени выявления отказавшего процессора. Устройство для управления реконфигурацией содержит шесть элементов И, два элемента задержки, три группы элементов И, группу элементов ИЛИ, генератор тактовых импульсов, регистр готовности процессоров, первый и второй регистры сдвига, шифратор согласования, элемент ИЛИ, элемент НЕ и триггер блокировки. Устройство позволяет сократить время выявления отказавшего процессора с m , до трех тактов контроля. 4 ил., 2 табл. & Ё

о1I1 ...1Р1 3

пгН ...J . j . 1 2J

ш+2 0 .. ОО. ....6- 61 12

ОО

0О

1О

Of О

о о t

О00

Табли ца

Таблица 2

т - 1(1111 «„м- if

. -

-0| Ol l 0| H

i,«i

- I I I I I

Ј

-E

- E Ј:

IVjiG T-Hvrg

c

CO

Й

Фиг 5

Фиг: 4

| Авторское свидетельство СССР №1526454 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-03-07—Публикация

1989-12-11—Подача