Изобретение относится к радиотехнике и может быть использовано при проектировании устройств отображения информации например устройств ото- j бражения самолетных MeTeo и o63Oj Hbcs радиолокационных станций (РЛС),

Целью изобретения является повьр ение быстродействия.

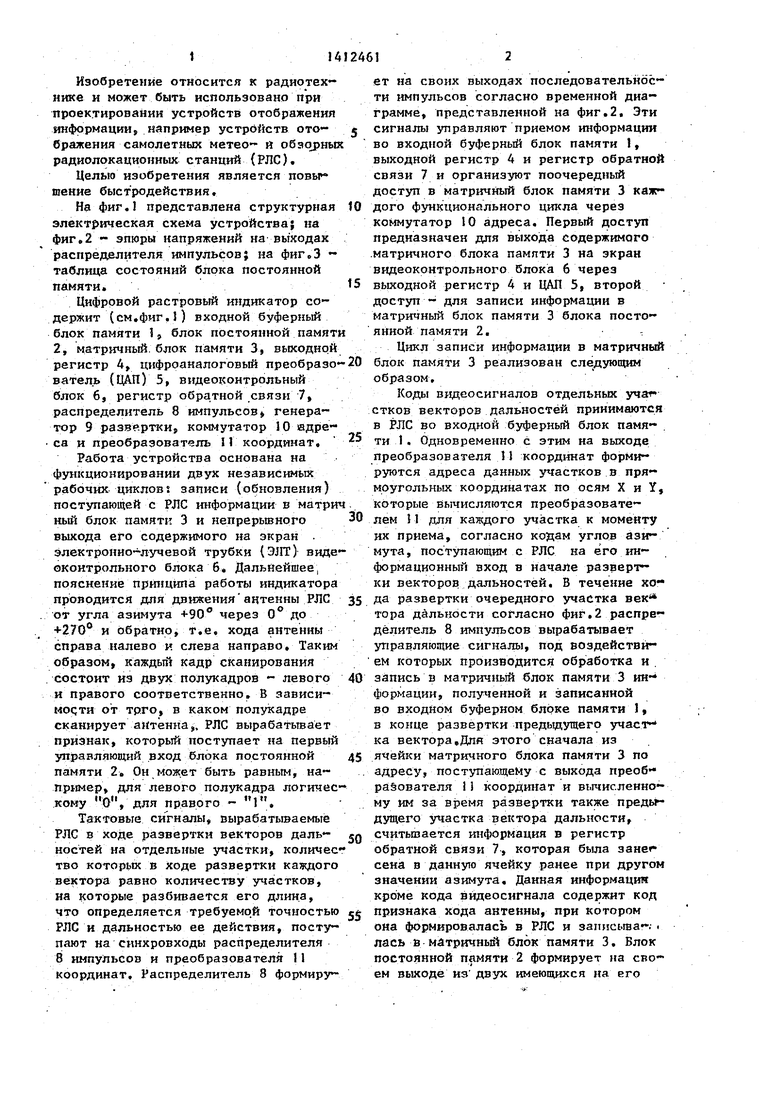

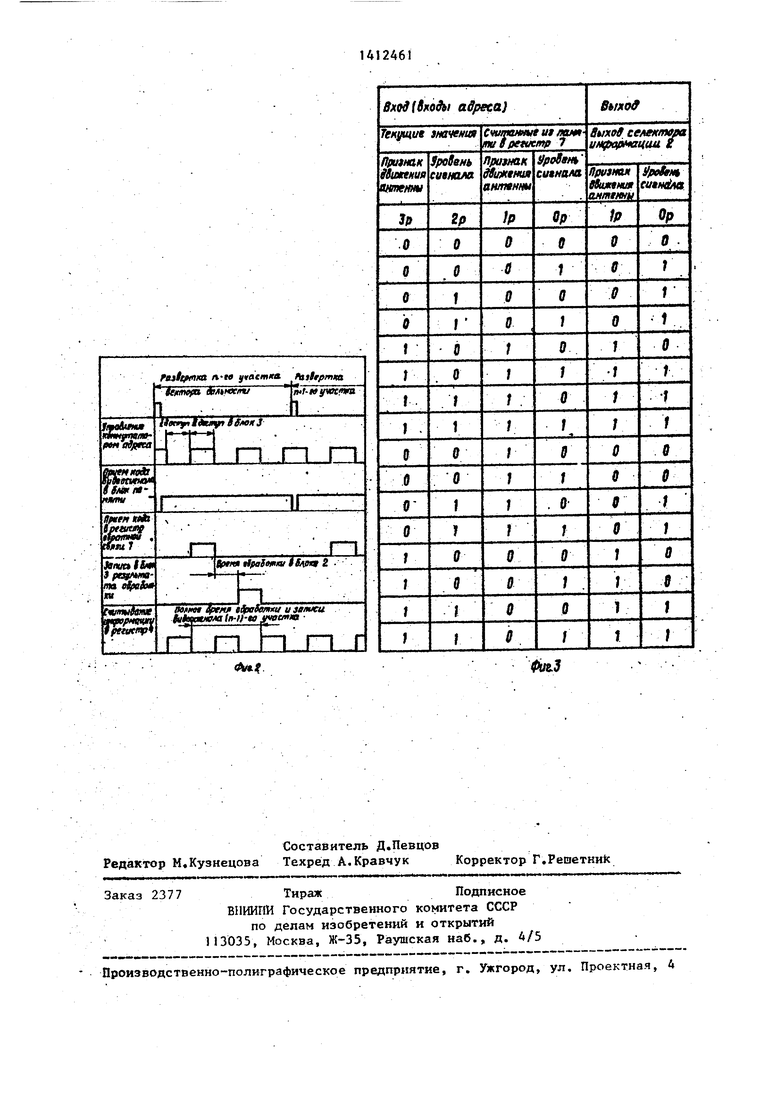

На фиг.1 представлена структурная 10 электрическая схема устройства; на фиг.2 - эпюры напряжений на выходах распределителя импульсов} на - таблица состояний блока постоянной памяти. 5

Цифровой растровый индикатор содержит (см.фиг.1) входной буферный блок памяти 1, блок постоянной памяти 2, матричный блок памяти 3, выходной регистр А, цифроаналоговый преобразо-20 ватель (ЦАП) 5, видеоконтрольный блок 6, регистр обра.тной связи 7 распределитель 8 импульсов генератор 9 коммутатор Ш ядре- са и преобразователь II координат,

Работа устройства основана на фу1жционировании двух независнмьт рабочих ЦИКЛОВ записи (обновления) поступающей с РЛС информации в матрич. ный блок памяти 3 и непрерьгоного 30 выхода его содержимого на экран . электронно-лучевой трубки (ЭЛТ) видеоконтрольного блока 6, Дальнейшее. пояснение принципа работы индикатора проводится для движения антенны РЛС 35 от угла азимута +90 через -270 и обратно, т.е. хода антенны справа налево и слева направо. Таким образом каждьп1 кадр сканирования состоит из двух полукадров - левого 40 и правого соответственно В зависи- MOQTH от трго, в каком полукадре сканирует антенна,. РЛС вырабатывает признак, который поступает на первый управляющий вход блока постоянной 45 памяти 2. Он может быть равным, например, для левого полукадра логическому О, для правого - 1,

Тактовые сигналы, вырабатываемые РЛС в ходе развертки векторов даль- JQ ностей на отдельные участки, количес тво которьк в ходе развертки каждого вектора равно количеству участков, на которые разбивается его длина, что определяется требуемой точностью jt РЛС и дальностью ее действия, поступают на синхровходы распределителя 8 импульсов и преобразователя I1 координат. Распределитель 8 формирует на своих выходах последовательности импульсов согласно временной диаграмме, представленной на фиг,2. Эти сигналы управляют приемом информация во входной буферный блок памяти , выходной регистр 4 и регистр обратной связи 7 и организуют поочередный доступ в матричный блок памяти 3 каждого функционального цикла через коммутатор 10 адреса. Первый доступ предназначен для выхода содержимого .матричного блока памяти 3 на экран видеоконтрольного блока 6 через выходной регистр 4 и ЦАП 5, второй доступ - для записи информации в матричный блок памяти 3 блока постоянной памяти 2. Цикл записи информации в матричный блок памяти 3 реализован следующим образом.

Коды В1щеосигналов отдельных уча стков векторов дальностей принимаются в РЛС во входной буферный блок памяти 1 . Одновременно с этим на выходе преобразователя 11 координат формируются адреса данных участков в прямоугольных координатах по осям X и Y, которые вычисляются преобразователем 11 для каждого участка к моменту их приема, согласно кодам углов азимута, поступающим с РЛС на его информационный вход в начале развертки векторов дальностей. В течение хода развертки очередного участка век тора дальности согласно фиг,2 распределитель 8 импульсов вырабатывает управляющие сигналы, под воздействием которых производится обработка и . запись S матричный блок памяти 3 информации, полученной и записанной во входном буферном блоке памяти 1, в конце развертки предьздущего участ ка вектора.Дпя этого сначала из ячейки матричного блока памяти 3 по адресу, поступающему с выхода преоб - ра§ователя П координат и вычисленному им за время развертки также предьН дущего участка вектора дальности, считьшается информация в регистр обратной связи 7, которая была зане сена в даннуто ячейку ранее при другом значении азимута. Данная информация кроме кода видеосигнала содержит код признака хода антенны, при котором она формировалась в РЛС и запнсыва-. лась в матричньй блок памяти 3. Блок постоянной памяти 2 формирует на своем выходе из двух имеющихся на его

входах кодов видеосигналов, поступа- юших q входного буферного блока памяти 1 и-регистра обратной связи 7, а также текущего признака направлени движения антенны РЛС информации) по следующему алгоритму: если признаки хода антенны, текугаий и считанный из матричного блока памяти 3 в регистр обратной связи 7, совпадают, т.е. обе единицы или оба нуля, то из двух кодов видеосигналов выбирает ся более приоритетный, например, имеющий максимальное значение, В про тивном случае на выход блока посто- янной памяти 2 подается значение код видеосигнала с входного буферного блока памяти I, т.е. вновь поступившее (см.фиг.З, пример алгоритма выделения максима:льного сидеосигнала с двумя уровнями градации - О и 1. В реальном случае уровней градации (интенсивнрстей) видеосигнала может быть четыре и более).

При наступлении представления очередного второго доступа информация с выхода блока постоянной памяти за- ттисьгаается в выбранную ячейку матричного блока памяти 3. Вместе с кодом видеосигнала 8 ячейку матричного блока памяти 3 заносится также текущий признак хода антенны РЛС, На это процесс обработки и записи кода видеосигнала участка вектора дальности заканчивается и распределитель 8 импульсов прекращает выдачу сигналов на входной буферный блок памяти I, выходной регистр А и регистр обратной связи 7 и ждет импульса начала нового участка. С его приходом описанный процесс повторяется. Таким образом, за время хода полукадра в матричный блок памяти 3 занесется информация всех векторов дальностей сканирования антенны РЛС в преобра- зойайных прямоугольных координатах. Причем при записи в одну и ту же ячейку матричного блока памяти 3 информации групп участков видеосигналов от одного или нескольких соседних векторов дальностей, возникающей вследствие преобразования систем координат, будет произведен отбор и запись в данную ячейку более приоритетного сигнала из данной группы. В течение следующего полукадра информация в ячейках матричного блока памяти 3 сменится.

10

5 J5 2025

J246I

Цикл вьтода информации из матричного блока памяти 3 на экран видеоконтрольного блока 6 осуществляется по строкам или столбцам, адрес которых формируется генератором 9 развертки синхронно с тактами представления первого доступа согласно фиг.2 формируемыми непрерывно распределителем 8 импульсов. Для непрерывной подачи видеосигнала на ЦАП 5, считываемого из матричного блока памяти 3, он предварительно записывается в выходной регистр 4 по сигналам с выхода распределителя 8 импульсов. Выход ЦАП 5 управляет яркоетным каналом видеоконтрольного блока 6, а .аналоговый выход сигнала развертки генератора . 9 - отклонением луча ЭЛТ.

Таким образом, на прямоугольном растре ЭЛТ видеоконтрольного блока 6 формируется изображение, аналогичное изображению на экране индикаторе, кругового обзора в пределах азимуталь ного угла +90 - 0° - +270°.

Таким образом, в предлагаемом индикаторе прием информации с РЛС осуществляется непрерывно, по мере .Сканирования антенны, с непосредст венной записью ее в матричный блок памяти 3 вне зависимости от работы генератора 9 развертки.

30

5

0

5

0

5

Формула изобретения

Цифровой растровый индикатор, содержащий матричный блок памяти, коммутатор адреса, преобразователь координат, видеоконтрольный блок, генератор развертки и цифроаналоговый преобразователь, выход которого соединен с информационным входом виде оконтрольного блока, вход отклоняющей системы которого соединен с аналоговым выходом сигнала развертки генератора развертки, информационный вход преобразователя координат является входом кода азимута индикатора, а выход соединен с первым информационным входом коммутатора адреса, второй информационный вход которого соединен с цифровым адресным выходом генератора развертки, а выход - с адресным входом матричного блока памяти, отличающийся тем, что, с целью повышения быстродействия, введены входной буферный блок памяти, блок постоянной памяти, выходной регистр, регистр обратнЬй

связи и распределитель импульсов, сннхровход которого соединен с синх- ровходом преобразователя координат и является входом тактового сигнала развертки индикатора, выход.сигнала управления считьюанием информации распределителя импульсов соединен с сянхровходом входного буферного блока памяти выход сигнала считывания - с сиихровходон выходного регистра, выход сигнала уЛравлення ripu- . ема кодов связан с синхровходом регистра обратной связи, выход сигнала управления записью - с соответствующим входом матричного блока памя:ти, а выход сигнала управления адресами - с входом управления коммутатора ад- ресл и с синхровходом генерагора

1A12A6I6

развертки, первый управляюошй вход блока постоя-нной является входом сигнала направления движения антенны индикатора, второй управляющий вход

: со|гдинен с выходом ;входного буферного блока памяти, третий управляющий вход подключен к выходу регистра обратной связи, а выход - к информа10 ционному входу матричного блока памяти, выход которого соединен с И1 фо1 1ационными входами регистра .об ратной связи и выходного регистре, ; выход которого свяэан С входом цифроfS аналогового преобразователя, инфо1Я4аг ционный вход входного буферного блока памяти является входом кода видео- сигнала индикатора

Л.

Фat

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| Цифровой растровый индикатор | 1983 |

|

SU1111111A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1988 |

|

SU1562954A1 |

| Формирователь кодов радиально-круговой развертки для индикатора кругового обзора | 1986 |

|

SU1401422A2 |

| ГЕНЕРАТОР ФЛЮКТУИРУЮЩИХ СИГНАЛОВ ЦЕЛЕЙ | 2002 |

|

RU2253129C2 |

| Телевизионный индикатор радиолокатора | 1985 |

|

SU1617662A2 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Телевизионный индикатор радиолокатора | 1985 |

|

SU1617663A2 |

| Устройство для отображения информации | 1984 |

|

SU1236541A1 |

Изобретение относится к радио технике. Цель изобретения - повьшение быстродействия. содержит матричный.блок 3 памяти,ЦАП 5,видеоконтрольный блок 6,генератор 9 развертки, коммутатор 10 адреса и пре образователь 11 координат. Введены входной буферный блок 1 памяти, блок 2 постоянной памяти, выходной регистр 4, регистр 7 обратной связи И распределитель 8 импульсов. Работа устр-ва основана на функционировании двух независимых рабочих циклов: записи поступающей с РЛС информации в блок 3 и непрерывного выхода его содержимого на зкран блока 6. Движение антенны РЛС от угла азимута +90° через 0° до - -270 и обратно, В зависимости от того, в каком полу кадре сканирует антенна, РЛС выраба- тывает признак, к-рый поступает на 1-й управляющий вход блока 2. Он м.б. равным, например, для левого полукадра логич. О, для правого - 1. Тактовые сигналь;, выр абатьюае- мые P. flC, поступают на синх ров ходы . распределителя 8 и преобразователя 11. Распределитель 8 формирует последовательности импульсов,, Эти налы, управляют приемом инфо рмацни в блок 1, регистр 4 и регистр 7 и орга- поочередный доступ в блок 3 каждого .функционального цик.па через коммутатор 10. l -й доступ предназначен для вывода содержимого 3 на экран блока 6 через регис;тр 4 и ЦАП 5, - для записи 1шформации в блок 3. Цикл вьшода информации из блока 3 на экран блока 6 осуществляется, по строкам или столбцам, адрес гс-рых формируется генератором 9 син- нронно с тактами представления I то доступа. 3 ил. СЛ

| Устройство для укладки листов | 1970 |

|

SU410602A1 |

| Питательное приспособление к трепальной машине для лубовых растений | 1923 |

|

SU343A1 |

| Авторское свидетельство СССР inilU, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-06-23—Публикация

1986-09-04—Подача