Од

;о

00

ю

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи и обработки информации, а также при построении анализаторов и синтезаторов сигналов.

Цель изобретения - повышение быстродействия устройства.

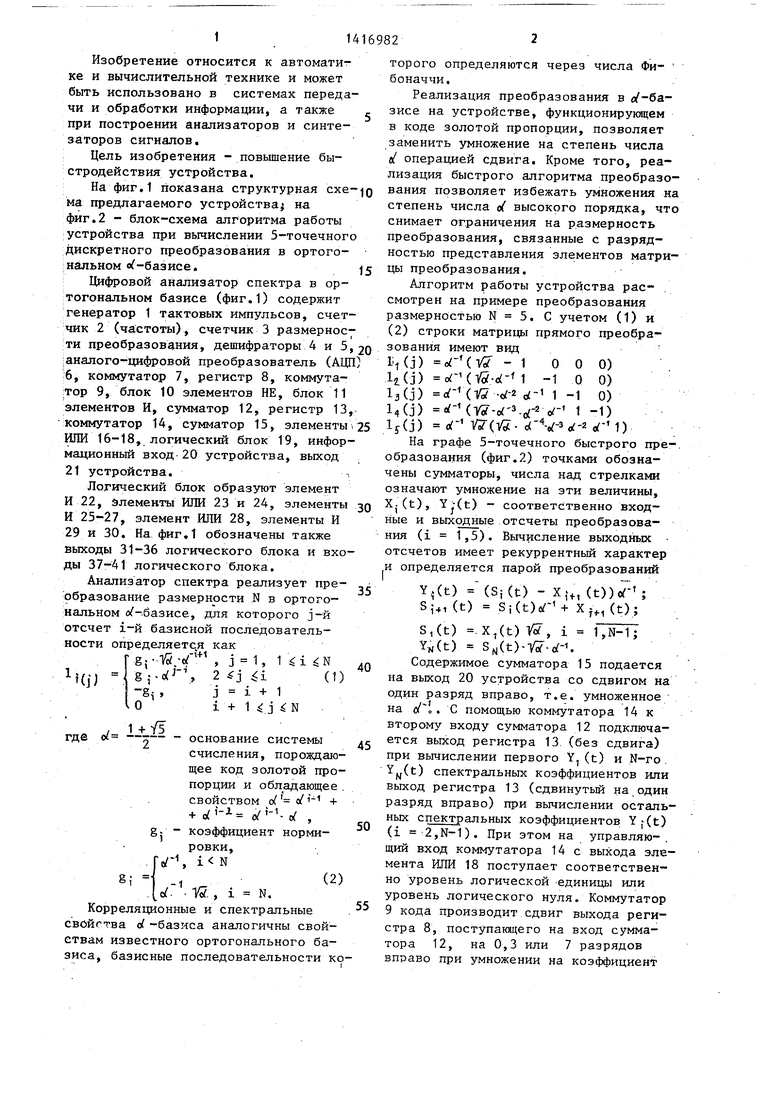

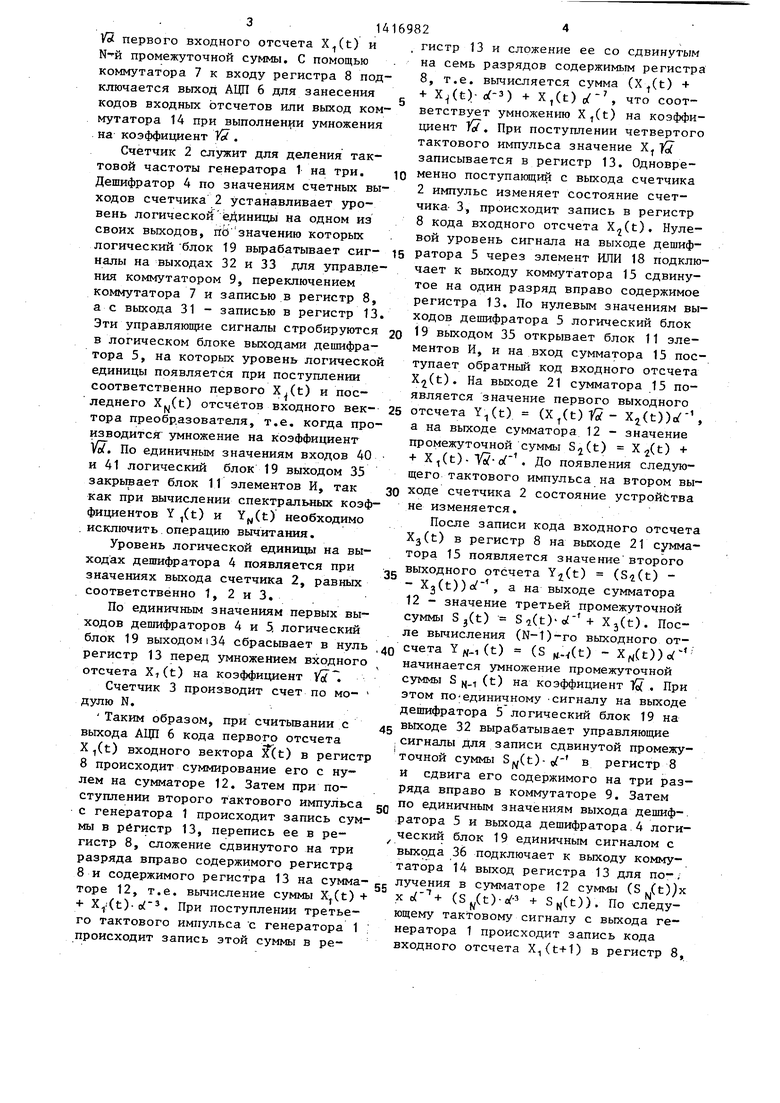

На фиг.1 показана структурная cxeма предлагаемого устройства; на фиг.2 - блок-схема алгоритма работы устройства при вычислении 5-точечного дискретного преобразования в ортогональном о -базисе. : Цифровой анализатор спектра в ортогональном базисе (фиг,1) содержит генератор 1 тактовых импульсов, счетчик 2 (частоты), счетчик 3 размерности преобразования, дешифраторы 4 и 5, ;аналого-цифровой преобразователь (АЦП :6, коммутатор 7, регистр 8, коммутатор 9, блок 10 элементов НЕ, блок 11 элементов И, сзгмматор 12, регистр 13, коммутатор 14, сумматор 15, элементы ИЛИ 16-18, логический блок 19, информационный вход 20 устройства, выход 21 устройства.

Логический блок образуют элемент И 22, элементы ИЛИ 23 и 24, элементы И 25-27, элемент ИЛИ 28, элементы И 29 и 30. На фиг,1 обозначены также выходы 31-36 логического блока и входы 37-41 логического блока.

Анализатор спектра реализует преобразование размерности N в ортогональном .базисе, для которого j-й отсчет -й базисной последовательности определяется как

( , j 1, 1 i N

-

1

UjJ

где У

1 +/5

1, 1 i N 2 j i (I) j i + 1 i + 1 j N

основание системы счисления, порождающее код золотой пропорции и обл адающее . свойством о( +

1-1

+ о( -- о/ g. - коэффициент нормировки, -

8i 1 -1 (2)

.о, . -И., i N.

Корреляционные и спектральные свойства d -базиса аналогичны свойствам известного ортогонального базиса, базисные последовательности ко

Q 5 0 5

о

5

торого определяются через числа Фи- боначчи.

Реализация преобразования в зисе на устройстве, функционирующем в коде золотой пропорции, позволяет заменить умножение на степень числа (i операцией сдвига. Кроме того, реализация быстрого алгоритма преобразования позволяет избежать умножения на степень числа / высокого порядка, что снимает ограничения на размерность преобразования, связанные с разрядностью представления элементов матрицы преобразования.

Алгоритм работы устройства рас- . смотрен на примере преобразования размерностью N 5. С учетом (1) и (2) строки матрицы прямого преобразования имеют вид l l(J)

ll(j) bCJ)

(1 - 1 о -1

00)

о 0)

/-(V -«/-г о(- 1-10) l4(J) « -4vy-o(( 1 -1) lj(j) /- V7( c( V of-2 )

Ha графе 5-точечного быстрого преобразования (фиг.2) точками обозначены сумматоры, числа над стрелками означают умножение на эти величины, Xj(t), Y.-(t) - соответственно входные и выходные отсчеты преобразования (i 1,5). Вычисление выходных отсчетов имеет рекуррентный характер и определяется парой преобразований

Y,(t) (Si(t) - Х,ч, (t)) S,-4i (t) Si(t) X., (t);

0

5

0

5

Si(t) .X,(t) T, i 1,N-1;

) S(t)-Yrf-of- . Содержимое сумматора 15 подается на выход 20 устройства со сдвигом на один разряд вправо, т.е. умноженное на (/,. С помощью коммутатора 14 к второму входу сумматора 12 подключается выход регистра 13, (без сдвига) при вычислении первого Y,(t) и N-ro . Yn(t) спектральных коэффициентов или выход регистра 13 (сдвинутьй на один разряд вправо) при вычислении остальных спектральных коэффициентов Yf(t) (i 2,N-1). При этом на управляю-, щий вход коммутатора 14 с выхода элемента ВДИ 18 поступает соответственно уровень логической -единицы или уровень логического нуля. Коммутатор 9 кода производит сдвиг выхода регистра 8, поступамцего на вход сумматора 12, на 0,3 или 7 разрядов вправо при умножении на коэффициент

31416982

V2 первого входного отсчета X(t) и , гистр 13 и сложение ее со сдвинутым N- ft промежуточной суммы. С помощью . на семь разрядов содержимым регистра коммутатора 7 к входу регистра 8 под- 8, т.е. вычисляется сумма ((t) + ключается выход АЦП 6 для занесения + X(t)- cf-) + X,(t) (/ , что соот- кодов входных отсчетов или выход ком- ветствует yмнoжeн пo X,(t) на коэффи- мутатора 14 при выполнении умножения циент Т. При поступлении четвертого .на коэффициент 1.тактового импульса значение Х 1

Счетчик 2 служит для деления так- записывается в регистр 13. Одновре- товой частоты генератора 1 на три. Q менно поступаклций с выхода счетчика Дешифратор 4 по значениям счетных выходов счетчика 2 устанавливает уровень логической ёДиницы на одном из своих выходов, по значению которых логический блок 19 вырабатьшает сиг- is ратора 5 через элемент ИЛИ 18 подклю- налы на выходах 32 и 33 для управле- чает к выходу коммутатора 15 сдвину- ния коммутатором 9, переключением коммутатора 7 и записью в регистр 8, ас выхода 31 - записью в регистр 13. Эти управляющие сигналы стробируются 20 выходом 35 открывает блок 11 эле- в логическом блоке выходами дешифра- ментов И, и на вход сумматора 15 пос2 импульс изменяет состояние счетчика 3, происходит запись в регистр 8 кода входного отсчета ). Нулевой уровень сигнала на выходе дешифтое на один разряд вправо содержимое регистра 13. По нулевым значениям выходов дешифратора 5 логический блок

записывается в регистр 13. Одновре- менно поступаклций с выхода счетчика ратора 5 через элемент ИЛИ 18 подклю- чает к выходу коммутатора 15 сдвину- выходом 35 открывает блок 11 эле- ментов И, и на вход сумматора 15 пос2 импульс изменяет состояние счетчика 3, происходит запись в регистр 8 кода входного отсчета ). Нулевой уровень сигнала на выходе дешифзаписывается в регистр 13. Одновре- менно поступаклций с выхода счетчика ратора 5 через элемент ИЛИ 18 подклю- чает к выходу коммутатора 15 сдвину- выходом 35 открывает блок 11 эле- ментов И, и на вход сумматора 15 постое на один разряд вправо содержимое регистра 13. По нулевым значениям выходов дешифратора 5 логический блок

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра в ортогональном базисе | 1989 |

|

SU1615740A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1429125A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки /ЭЛТ/ | 1989 |

|

SU1633387A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Спектроанализатор | 1985 |

|

SU1302294A1 |

| Устройство для выполнения быстрого преобразования Уолша-Адамара | 1988 |

|

SU1605254A1 |

| Генератор систем базисных функций аристова | 1990 |

|

SU1753465A2 |

| Устройство для быстрого ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1989 |

|

SU1615742A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1988 |

|

SU1533006A1 |

Изобретение относится к автома- . тике и вычислительной технике и может быть использовано в системах передачи и обработки информации, при построении анализаторов и синтезаторов сигналов. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что в состав анализатора входят генератор тактовых импульсов 1, счетчики 2, 3, дешифраторы 4, 5, аналого-цифровой преобразователь 6, коммутатор 7, регистр 8, коммутатор 9, блок элементов НЕ 10, блок элементов И 11, сумматор 12, регистр 13, коммутатор 14, сумматор 15, элементы ИЛИ 16, 17, 18, логический блок 19, информационный вход 20 анализатора, вывод 21 анализатора, логический блок содержит элемент И 22, элементы ИЛИ 23, 24, 28, элементы И 25, 26, 27, 29, 30. 2 ил. , i (Л

тупает обратный код входного отсчета ). На выходе 21 сумматора 15 появляется значение первого выходного

. -1

тора 5, на которых уровень логической единицы появляется при поступлении соответственно первого X ,(t) и последнего Xj(t) отсчетов входного век- 25 отсчета Y:,(t) (X(t)yrf- Xj(t))o( , тора преобразователя, т.е. когда про- а на выходе сумматора 12 - значение изводится умножение на коэффициент промежуточной суммы Sj(t) ) + VoT. По единичным значениям входов 40 + X(t)- Vel-о( До появления следзпо- и 41 логический блок 19 выходом 35 щего тактового импульса на втором вы- закрывает блок 11 элементов И, так зо ходе счетчика 2 состояние устройства как при вычислении спектральных коэф- не изменяется, фициентов Y(t) и Y(t) необходимо

35

После записи кода входного отсчета XjCt) в регистр 8 на выходе 21 сумматора 15 появляется значение второго выходного отсчета YjCt) () - - )) ol , a на выходе сумматора 12 - значение третьей промежуточной суммьг Sj(t) - Sa(t) XjCt). После вычисления (N-1)-го выходного от- блок 19 выходом 134 сбрасывает в нуль .Q счета Yy.i(t) (S .(t) - X(t)) регистр 13 перед умножением входного начинается умножение промежуточной отсчета X, (t) на коэффициент УоГ суммы S i., (t) на коэффициент )о( . При

этом по единичному Сигналу на выходе дешифратора 5 логический блок 19 на jg выходе 32 вьфабатывает управляющие :сигналы для записи сдвинутой промежу- точной суммы S(t)-(/- в регистр 8 и сдвига его содержимого на три разряда вправо в коммутаторе 9. Затем gg по единичным значениям выхода дешиф-. с генератора 1 происходит запись сум- ратора 5 и выхода дешифратора.4 логи- мы в регистр 13, перепись ее в ре- ческий блок 19 единичным сигналом с гистр 8, сложение сдвинутого на три выхода 36 подключает к выходу комму- разряда вправо содержимого регистра татора 14 выход регистра 13 для по-; 8 и содержимого регистра 13 на сумма-д лучения в сумматоре 12 суммы (S .,(t))x торе 12, т.е. вычисление суммы Xj(t) + х о(+ (S.(t) + )). По следу- + X.(t). При поступлении третье- ющему тактовому сигналу с выхода ге го тактового импульса с генератора 1 ; нератора 1 происходит запись кода происходит запись этой суммы в ре- входного отсчета ) в регистр 8,

исключить операцию вычитания.

Уровень логической единицы на выходах дешифратора 4 появляется при значениях выхода счетчика 2, равных соответственно 1, 2 и 3,

По единичным значениям первых выходов дешифраторов 4 и 5 логический

Счетчик 3 производит счет по мо- дулю N.

Таким образом, при считьшании с выхода АЦП 6 кода первого отсчета X ,(t) входного вектора X(t) в регистр 8 происходит суммирование его с нулем на сумматоре 12. Затем при поступлении второго тактового импульса

тупает обратный код входного отсчета ). На выходе 21 сумматора 15 появляется значение первого выходного

. -1

отсчета Y:,(t) (X(t)yrf- Xj(t))o( , а на выходе сумматора 12 - значение промежуточной суммы Sj(t) ) + + X(t)- Vel-о( До появления следзпо- щего тактового импульса на втором вы- ходе счетчика 2 состояние устройства не изменяется,

35

.Q

считывание выходного отсчета Yj(t) (S(t)-46 ) о(- с выхода 21 устройства, начинается ш.1числение отсчетов йьпсодного вектора Y(t+1) аналогично описанному алгоритму вычисления выходного вектора (t).

формулаизобретения

Анализатор спектра в ортогональном базисе, содержащий блок элементов НЕ, блок элементов И, аналого-цифровой Преобразователь, информационный вход

Которого является информационным вхо- is элемента ИЛИ, выход которого подклюдом анализатора, первый и второй регистры, первый и второй сумматоры, генератор тактовых импульсов, выход которого подключен к счетному входу {первого счетчика, а вход переноса второго сумматора является входом логической единицы анализатора, отличающийся тем, что, с це- члью повьшения быстродействия, в него введень1 первьш, второй и третий ком- таторы, первый и второй дешифрато- :ры, второй счетчик, шесть элементов ИЛИ, пять элементов И элемент НЕ, выход которого подключен к первому блока элементов И, выход которого подключен к первому входу второго сумматора, выход которого являет- ся выходом анализатора, выход переноса первого счетчика подключен к счетному входу второго счетчика, первым входам первого и второго элементов ИЛИ и тактовому входу аналого-цифрового, преобразователя, выход которого подключен к первому информационному входу первого коммутатора, выход которого подключен к информационному входу первого регистра, выход которого подключен к входу блока элементов НЕ и информационному входу второго

коммутатора, выход которого подключен 45 выход первого элемента И подключен к к первому входу первого сумматора, тактовому входу второго регистра, вы- выход которого подключен к информаци-: ход блока элементов НЕ подключен к .; онному входу второго регистра, выход второму входу блока элементов И, вы- которого подключен к второму входу второго сумматора и информационному входу третьего коммутатора, выход ко50

ход генератора тактовых импульсов подключен к второму входу пятого элемента И, а выход четвертого элемента ИЛИ подключен к управляющему входу третьего-коммутатора.

торого подключен к второму входу первого сумматора и второму информационов

14169826

ному входу первого коммутатора, ин

формационньй выход первого счетчика подключен к входу первого дешифратора, первьй выход которого подключен к первому управляющему входу второго коммутатора, второй выход первого дешифратора подключен к первым входам первого и второго элементов И, третий выход первого дешифратора подключен к первому входу третьего элемента И, выход которого подключен к второму управляющему входу второго коммутатора и первому входу третьего

чен к первым входам четвертого и пятого элементов И, выходы которых подключены соответственно к первому входу четвертого элемента ИЛИ и вто0 рому входу второго элемента ИЛИ, выход которого подключен к входу разрешения считывания второго регистра, информационньй выход второго счетчика подключен к входу второго дешифра5 тора, первьй выход которого подключен |с второму входу четвертого элемента ИЛИ, второму входу первого, элемента И, первому входу пятого элемента ИЛИ и первому входу шестого элемента ИЛИ,

0 выход которого подключен к входу элемента НЕ, второй выход второго дешифратора подключён к второму входу шестого элемента ИЛИ,:второму входу четвертого элемента И и второму входу

35 пятого элемента ИЛИ, вькод которого

. подключен к вторым входам второго и

третьего элементов И, выход второго

элемента И подключен к второму входу

третьего элемента ИЛИ, третьему уп0 равлякяцему входу второго коммутатора, управлякнцему входу первого коммутатора и второму входу первого элемен- та ИЛИ, выход которого подключен к установочному входу первого регистра.

выход первого элемента И подключен к тактовому входу второго регистра, вы- ход блока элементов НЕ подключен к .; второму входу блока элементов И, вы-

ход генератора тактовых импульсов подключен к второму входу пятого элемента И, а выход четвертого элемента ИЛИ подключен к управляющему входу третьего-коммутатора.

vu

fus.Z

| Устройство для снятия герметика с кабелей | 1982 |

|

SU1116485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1986-06-23—Подача