(21)4204257/24-24

(22)02.02.87

(46) 07.10.88. Бюл. № 37

(71)Институт электроники и вычислительной техники АН ЛатвССР

(72)И.Я. Билинский, Я.Р, Виксна, И.Б. Медниекс и Р.Ф, Немировский (53) 681.32(088,8)

(56)Авторское свидетельство СССР № 571762, кл. G 0| R 23/165, 1977.

.Авторское сввдетельство СССР 928363, кл. G 06 F 1/332, 1982. .(54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ

(57)Изобретение относится к автоматике, и вычислительной технике и может быть использовано для определения коэффициентов преобразования Фурье непрерьгоных сигналов в реальном масштабе времени. Цель изобретения - уп- рощенир устройства. Поставленная

цель достигается за счет того, что в состав устройства входят генератор

0-

1 псевдослучайной последовательности, аналого-цифровой преобразователь 2, коммутаторы 3,6,9,12, 11, блоки 4 и 5 памяти, адресные счетчики 7,8, генератор 10 тактовых импульсов, элемент ИЛИ 13, счетчик 14 циклов,блок 15 постоянной памяти, триггеры 16, Т7 при этом в устройства входят два блока цифровой обработки, каждый из которых содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 18, накапливающие сумматоры 19, регистры 20 и узел 21 решения системы линейных уравнений. Устройство для выполнения преобразования Фурье основано на использовании кусочно-постоянных функций базиса и их стохастической дискретизации одновременно с обрабатьшаемым сигналом. Использование кусочно-постоянных функций R(t), принимающих значения +1, позво-- ляет вычислить свертку без выполнения операций умножения многоразрядных чисел, 1 ил.

SS

(Л

с

4;

to

CD

to ел

Изобретение относится к автоматике

В1..1числитбльной технике и может бы7ь использовано для определения коэ ициентов преобразования Фурье непрерьшных сигналов в реальном масштабе времени,

; Цель изобретения - упрощение устройства.

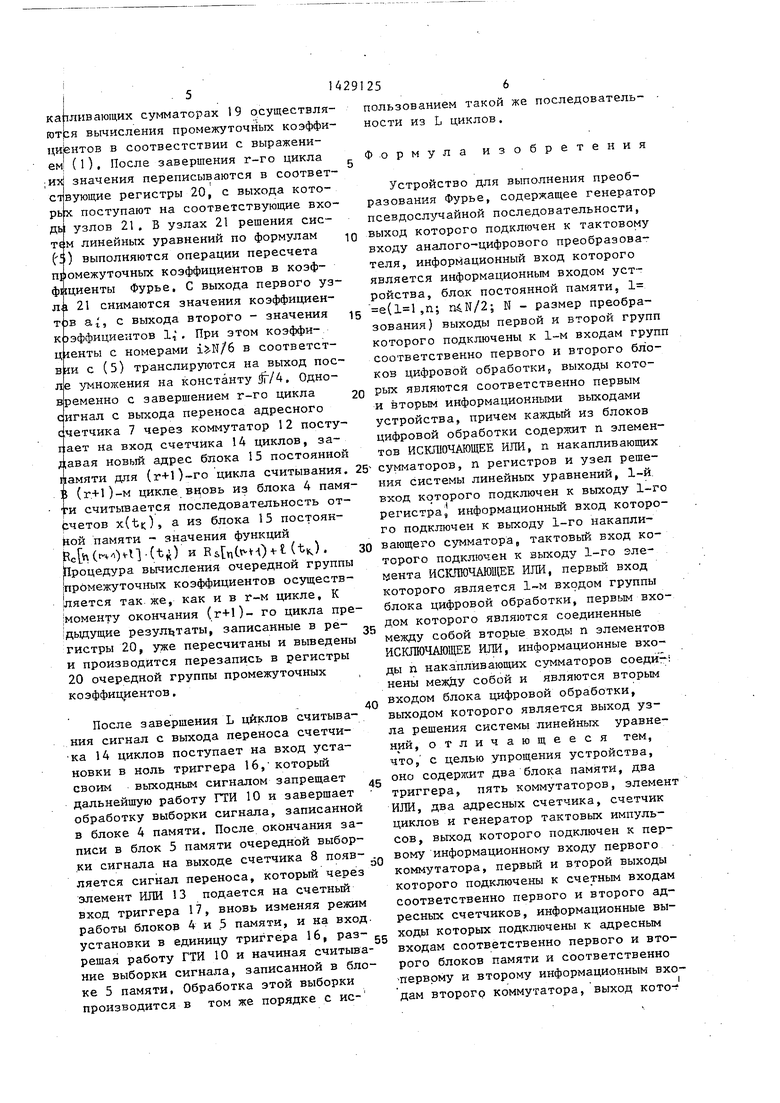

На чертеже приведена структурная устройства для выполнения пре- оСразования Фурье.

Устройство содержит генератор псевдослучайной импульсной последовательности, аналого-цифровой преоб- р зователь 2, коммутатор 3 блоки 4 и. 5 )мяти, коммутатор 6, адресные счет- 4biKH 7 и 8, коммутатор 9, генератор

тактовых импулъсоБ, коммутаторы 11

12, элемент ШШ 13, счетчик 14, б|пок 15 постоянной памяти, тригге- ,1 16 и 17,

Кроме того, в устройство входят акже два идентичных п-канальнык бло- а цифровой обработки. Каждьй блок ключает элементы ИСКЛЮЧАЮЩЕЕ И.ПИ 18, акапливагащие сумматоры 19 и регист- ы 20, узел 21 решения системы линей- ых уравнений.

Устройство работает следующим об- |разом.

I Устройство для выполнения преобра- 13ования Фурье основано на использовании кусочно-постоянных функций базиса и их стохаст1-1Ческой дискретизации одновременно с обрабатываемым сигналом I Использование кусочно-постоянных функций R(t), принимающих значения ±.1 , позгволяет вычислить свертку без выполнения операций умножения много- разрядных чисел. Операция умножения отсчета сигнала x(tn) на значение, функции R{tj) сводится к присвоению знака а свертка S. x{t)R(t,;,) - к операциям сложения и вычитания.

В тех случаях, когда базис функций R(t) является ортогональным (функции Уолша, Хаара и другие), результаты свертки являются коэффициентами соответствующего ортогонального преобразования сигнала. Если необходимо иметь результаты в базисе гармонических функций (классическое ДПФ), то полезно применять неортогональньй промежуточный базис кусочно-постоянных функций, а затем вьтолнять пе- сложньй пересчет промежуточных коэффициентов в коэффициенты Фурье,

Рассмотрим применение в предлагаемом изобретении функций Rc(t) и Bs(t) типа меандр (знаковых функций соответственно сигналов cosZ iTft и .sin25rft).

Промежуточные коэффициенты в.{ и Ъ{ для соответствующих функций RcCt) HRs(t), (,2.,. ,И/2) при дискретном преобразовании вычисляются по формулам свертки

N Z x(tORcL(t); .i(tj,

2 - x(tjR jj(1)

4t

5

0

0

5 0

где ,2,,..N; N - длина выборки отсчетов сигнала. Каждую из функций Rc(t) и Ri(t) можно разложить в ряд Фурье, который содержит составляющие с нечетными частотами. 4

Ксг() cosC2j-l)i4ff,

л)(2)

RM(t) sin(2j-i)iAf,

где uf l/NAtcp ;(З)

Atcp - средний интервал дискрети . зации,

. f . Промежуточные коэффициенты а и

Ъ| и коэффициенты Фурье а -J. и Ъ в соответствии с (О и (2) связьгаает система линейных уравнений

- (-1) - VT Ь 23ГГ

1 , .

bj ,

(А)

ъ. - fr;

Рещая систему уравнений (4), приходим к следующим окончательным выражениям для коэффициентов Фурье преобразуемого сигнала di.

(5)

5

0

5

Г ( (-1) а 4 i- ()Г IT г I 1

i i L TjTT JН)г.

™-. .

- целая часть выражения в скобках.

Из (5) следует, что все коэффициенты Фурье с номерами непосредственно равны соответствующим промежуточным коэффициентам, умноженным на константу 7Г/4.

Как известно, стохастическая дискретизация позволяет снять ограничения, налагаемые теоремой Котельникова на верхнюю границу спектра преобразуемого сигнала, и обрабатывать без эффекта наложения сигналы с частотами большими, чем половина частоты дискретизации, В предлагаемом устройстве, поскольку использованы кусочно-постоянные функции базиса, имеющие теоретически неограниченный спектр, стохастическая дискретизация обрабатьшае- мого сигнала и базисных функций в совпадающие моменты времени является принципиально необходимой, В предлагаемом устройстве последовательность Q псевдослучайных интервалов времени между моментами дискретизации t задается алгоритмом работы генератора 1 псевдослучайной импульсной последовательности (ГПСИП), Поскольку д алгоритм заДан, он может быть реали-г зован программно. Это позволяет заранее рассчитать последовательность

Rcl () значений всех функций промежуточного базиса для каждого 2о момента дискретизации ty и записать эту последовательность в блок i 5 памяти. В процессе преобразования входного сигнала АЦП 2 тактируется в моменты времени t импульсами, которые 2В

вьфабатьгеаются ГПСИП 1. Этим достигается эффект стахастической дискретизаций сигнала и функций промежуточного базиса в совпадающие моменты времени. С .выхода АЦП.2 отсчеты i:(tn) 30 сигнала в прямом коде через коммутатор 3. поступают на вход блока 14 памяти или на вход блока 5 памяти, в зависимости от того, какое из них в данный момент выполняет функцию запйси. Режим работы блоков устройства определяется состоянием триггера 17, который управляет всеми коммутаторами. Если на выходе триггера 17 - логическая единица, то блок 4 памяти о функционирует в режиме записи, а блок 5 памяти - в режиме считывания, Соответственно в режиме записи работает адресньй счетчик 7, который тактируется через коммутатор 9 той же псев- .g дослуч-айной последовательностью импульсов, что и АЦП 2. Б это время адресный счетчик 8 работает в режиме считьшания информации, записанной в блок 5 памяти, и тактируется через gp коммутатор 9 импульсной последовательностью, генерируемой ГТИ 10. После записи в блок 4 памяти последовательности из N отсчетов сигнала на выходе переноса адресного.счетчика 7 gg появляется импульс, который через элемент ИЛИ 13 поступает на счетный вход триггера 17, изменяя его выходной потенциал на логический ноль и :

35

Q д

о В

0

о g p g :

5

и.яменяя тем самым управляющий сигнал коммутаторов 3,6,951 и 12, При этом блок 4 памяти переходит в режим считывания записанной выборки сигнала, а блок 5 памяти - в режим записи следующей выборки без пр.опуска отсчетов, чем достигается обработка на соприкасающихся выборках. Импульсная последовательность от ГТИ 10 поступает теперь через коммутатор 9 на вход адресного счетчика 7, а псевдослучайная с выхода ГПСИП 1 - на вход адресного счетчика 8. Оргак;1зуется L циклов считьгоания выборки, записанной в блок 4 памяти. В ,г ,о -1 цикле отсчеты x{t), xlt) 5, , .х.( ii,,) из блока памяти последовательно поступают .на вход коммутатора 11, С первого выхода коммутатора II знаковый разряд отсчета xitк) подается на объединеннь е вторые входы эпеменгов ИСКЛЮЧАЮЩЕЕ VJU l 18 обоих блоков цифровой обработки. . абсолютного зкачения отсчета х{ UK. ) снима :.тся с BTopoiTi вьтхода коммутатора Пи подаетс.я на объедике.н- ные вторые входы и.;сачливающих сумматоров 10 блоков цифровой об ра.ботки, Одно.х:ре:-;енно с адресацией блока 4 памяти счетч иком 7 через коммутатор 6 и счетчиком 14 циклов за- .дается код адрзса блока 15 постоян- ной памят.И|| обеспечивается счить ванке функций R,(t,,) и Rs(t|.) промежуточного базиса,

В кахсдом г-м и.икле из блока 5 постоянной памяти, имеющего 2п выхо о .

дов f считываются значення п фз нкций Rc nr+lJ (t) н п функций (tv;), где ,,..() - десятичный код числа записанного в двоичном счет.чи- ке 14 числа циклон считывания; 1 1,2...п. Бинарные отсчеты функций Rcl tn) снимаемые с п выходов блока 15 постоянной памяти, подаются на первые входы соответствующих элементов ИСКЛЮЧАЮЩЕЕ Ш1И 18 первого блока цифровой обработки, бинарные отсчеты фукнций RsCti), Сгшмаемые с других п выходов блока 15 постоянной памяти, подаются на первые входы соответствующих элементов ИСЮ ВОЧАЮЩЕЕ ИЛИ 18 второго блока цифровой обработки. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 18 выполкя- ют операции перемножения знаков, сигналы с их выходов подаются на знаковые входы соответствующих накапливающих сумматоров 19, задавая код операции - сложение или вычитание. В наI.51429125

карливающих сумматорах 19 осуществля- гот|ся вычисления промежуточных коэффи- ци|еитов в соотвестствии с выражением (1), После завершения г-го цикла

пол нос

Фо

;И1 значения переписываются в соответствующие регистры 20, с выхода кото- рьх поступают на соответствующие входы узлов 21. В узлах 21 решения систем линейных уравнений по формулам Q () выполняются операции пересчета П11омежуточных коэффициентов в коэффициенты Фурье, С выхода первого узла 21 снимаются значения коэффициентов ai, с выхода второго - значения К Ээффициеитов 1. При зтом коэффи- -1енты с номерами i5.N/6 в соответст и с

(5)

транслируются на выход пос- е умножения на константу 1г/4. ОдноУстройство для выполнения преобразования Фурье, содержащее генератор псевдослучайной последовательности, выход которого подключен к тактовому входу аналого-цифрового преобразователя, информационный вход которого является информационным входом устройства, блок постоянной памяти, 1 15 е(,п; n4N/2; N - размер преобразования) выходы первой и второй групп которого подключены к входам груп соответственно первого и второго блоков цифровой обработкир выходы которых являются соответственно первым и вторьм информационными выходами устройства, причем каждый из блоков цифровой обработки содержит п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, п накапливающих

20

ц в л

временно с завершением г-го цикла сигнал с выхода переноса адресного счетчика 7 через коммутатор 12 посту- гает на вход счетчика 14 циклов, задавая новьй адрес блока 15 постоянной

памяти для (г+О-го цикла считывания. 25 сум1 1аторов, п регистров и узел реше- В (r+l)-M цикле вновь из блока 4 памя- ния системы линейных уравнений, 1-й

пользованием такой же последовательности из L циклов.

Формула изобретения

Устройство для выполнения преобразования Фурье, содержащее генератор псевдослучайной последовательности, выход которого подключен к тактовому входу аналого-цифрового преобразователя, информационный вход которого является информационным входом устройства, блок постоянной памяти, 1 е(,п; n4N/2; N - размер преобразования) выходы первой и второй групп которого подключены к входам групп соответственно первого и второго блоков цифровой обработкир выходы которых являются соответственно первым и вторьм информационными выходами устройства, причем каждый из блоков цифровой обработки содержит п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, п накапливающих

сум1 1аторов, п регистров и узел реше- ния системы линейных уравнений, 1-й

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения преобразования Фурье | 1980 |

|

SU928363A1 |

| Устройство для выполнения преобразования Фурье | 1985 |

|

SU1278887A1 |

| Устройство для определения спектра | 1981 |

|

SU972519A1 |

| Устройство для выполнения преобразования Фурье | 1986 |

|

SU1325509A1 |

| Устройство для выполнения преобразования фурье | 1984 |

|

SU1177822A1 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1418747A1 |

| Устройство для вычисления коэффициентов Фурье | 1983 |

|

SU1096655A1 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1424027A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

Ти считывается последовательность от- Ьчетов x(t), а из блока 15 постоянной памяти - значения функций ()Ч-(А) и R&tnCt-t-l). (tt). Процедура вычисления очередной группы |промежуточных коэффициентов осуществляется так. же, как и в г-м цикле, К ;моменту окончания (r+l)- го цикла предыдущие резул1 таты, записанные в ре

гистры 20, уже пересчитаны и вьтедены и производится перезапись в регистры 20 очередной группы промежуточных

коэффициентов,

После завершения L циклов считывания сигнал с выхода переноса счетчи- ка 14 циклов поступает на вход установки в ноль триггера 16, который своим выходным сигналом запрещает дальнейшую работу ГТИ 10 и завершает обработку выборки сигнала, записанной в блоке 4 памяти. После окончания записи в блок 5 памяти очередной выборки сигнала на выходе счетчика 8 появ- ляется сигнал переноса, который через элемент ИЛИ 13 подается на счетный вход триггера 17, вновь изменяя режим работы блоков 4 и 5 памяти, и на вход установки в единицу триггера 16, раз- решая работу ГТИ 10 и начиная считывание выборки сигнала, записанной в блоке 5 памяти, Обработка этой выборки производится в том же порядке с ис

вход которого подключен к выходу 1-го

0

Б

5

-

регистра, информационный вход которого подключен к выходу 1-го накапливающего сумматора, тактовый вход которого подключен к выходу 1-го зле- , мента ИСКЛЮЧАЮЩЕЕ ИЖ, первый вход которого является входом группы блока цифровой обработки, первым входом которого являются соединенные между собой вторые входы п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные входы п накапливающих сумматоров соеди г; нены между собой и являются вторым Q входом блока цифровой обработки, выходом которого является выход узла решения системы линейных уравнений, отличающееся тем, что, с целью упрощения устройства, оно содержит два блока памяти, два триггера, пять коммутаторов, элемент ИЛИ, два адресных счетчика, счетчик циклов и генератор тактовых импульсов, выход которого подключен к первому информационному входу первого коммутатора, первый и второй выходы которого подключены к счетным входам соответственно первого и второго адресных счетчиков, информационные выходы которых подключены к адресным входам соответственно первого и второго блоков памяти и соответственно первому и второму информационным входам второго коммутатора, выход кото-

рого подключен к первому адресному входу блока постоянной памяти, второй адресный вход которого подключен к информационному выходу счетчика циклов, счетный вход которого подключен к выходу третьего коммутатора, первый и второй информационные входы которого соединены соответственно с первым и вторым входами элемента ИЛИ и под- ключены к выходам переноса соответственно первого и второго адресных счетчиков, выход элемента ИЛИ подключен к входу установки в 1 первого триггера и тактовому входу второго триггера, выход которого подключен к управляющим входам первого второго, третьего, четвертого и пятого коммутаторов, выход аналого-цифрового преобразователя подключен к информа-

ционному входу четвертого коммутатора первьш и второй выходы которого подключены к информационным входам соответственно первого и второго блоков памяти, выходы которых подключены соответственно к первому и второму информационным входам пятого коммутатора, первый и второй выходы которого подключены соответственно к первому и второму входам первого и второго блоков цифровой обработки, выход переноса счетчика циклов подключен к входу установки в О первого триггера, выход которого подключен к входу останова Генератора тактовых импульсов, а выход генератора псевдослучайной последовательности подключен к второму информационному входу первого коммутатора.

Авторы

Даты

1988-10-07—Публикация

1987-02-02—Подача