2/

(Л

16157

Изобретение относится к авто-мат

М ОТ-ГТГГ / пч ч.

../у-г1и,л л автомати ке и вычислительной технике и может быть использовано в системах передачи и обработки многоканальной информации„ с Цель изобретения - расширение об- ласти применения за счет многоканаль- НОИ обработки данных.

Многоканальный анализатор спектра по кавдому каналу реализует преобразование размерности N в ортогональном Сб-базисе, для которого отсчет j-й базисной последовательности описьюает-1 ся выражением

10

(5

g; -|7. i 1, 1 8; , .

ё, i j+1; 0, J + liieN,

(1)

, 20

(5

где oi

1 +

-4

N; ,j-основание системы счисления, порож- дающей код золо- | той пропорции; .- коэффициент нормировки.

-. А лисуффИЦИ

.фнтов в канале имеет рекуррентньА ха- актер: -

In 1/ Дешифр торы 14 и 15, элемент НЕ 16, RS-тр геры 17 и 18, элемент ИЛИ 19, инфор ционныи вход 20 анализатора, вькод анализатора, тактовый вход 22 анали затора, вход 23 начальной установки анализатора, входы 24-28 и выход 29 умножителя 4.

Умножитель 4 на константу (фиг.

.вРЖИТ nv fMam/-i-r.T О/т00

25

Вь числеРгие спектральньпс 30 содер Г атор зПГТ ов в канале имеет рекуррентньА х : 33-%. я. Регистры

.ЧА и i; регистры

33-36, блоки 37-39 элементов И, инФормационньй вход 24 умножител, вх второГ. умножителя, первьй второй 27 и третий 28 входы управле .ния умножителя и вьпсод 29 умн ; ::: разом Работает следующим об

(а, 1,Х

х;

t+iK

S.,,4,

о.к-ЧоГ О, МН; k

) Ос ti ;

(2)

(3):

(4)

1, М-1),

це М

число обрабатываемьк каналов ().

Реализация преобразования Boi-бат исе на устройстве, функционирующем а коде золотой пропорции, позволяет заменить умножение на коэффициент операцией сдвига. Константа л|оГ в ви- де суммы степеней числа ьг имеет ввд

OC%oi-4oi- -i4o :- 4o6 24 .

Для 24-разрядного представления коэффиодента - в коде золотой пропорции (соответствующего 16-двоичным разрядам) получают

В начале работы на вход 23 началь НОИ установки анализатора сигнал УРОВНЯ Лог. 1, которьГпода ется на входы установки первого 12 и второго 13 счетчиков и устанавли их в нулевое состояние. Кроме того сигнал уровня Лог. 1 с вхптт;, 9 45 -ьной установки анализ т Гп д аеТ ся на вход элемента ШЖ 19, что ПРИВОДИТ к формированию на выводе последнего сигнала уровня Лог. 1 пп ступающего на S-вход К-8.-три;гер; 18 Это устанавливает его выгкод в состояние высокого потенциала. Коды нуля с выходов первого 12 и второго 13 счет чиков поступают на входы соответств но первого 14 и второго 15 дешифра оров. что ППч-аг.гтгг,г, j.

)«- (o,..c.-«,,,..f,vt5) РОЗ. -о-„оз,„;„;-ё „т,

- - с„™а.ьГ

Таким образом, для умножения на Т/й необходимо выполнить всего три елоЖ0НИЯ.

уровня Лог. Г ,

Сигнал уровня Лог. 1 с выхода первого дешифратора 14 поступает на

„ с

10

20

Режим многоканальной обработки не требует дополнительных арифметических узлов и реализуется только благо даря использованию блока регистров задержки, в которьй заносятся значения промежуточных сумм S. всех каналов. Входные отсчеты поступают последовательно - сначала все первые отсчеты, затем все вторые и т„д.

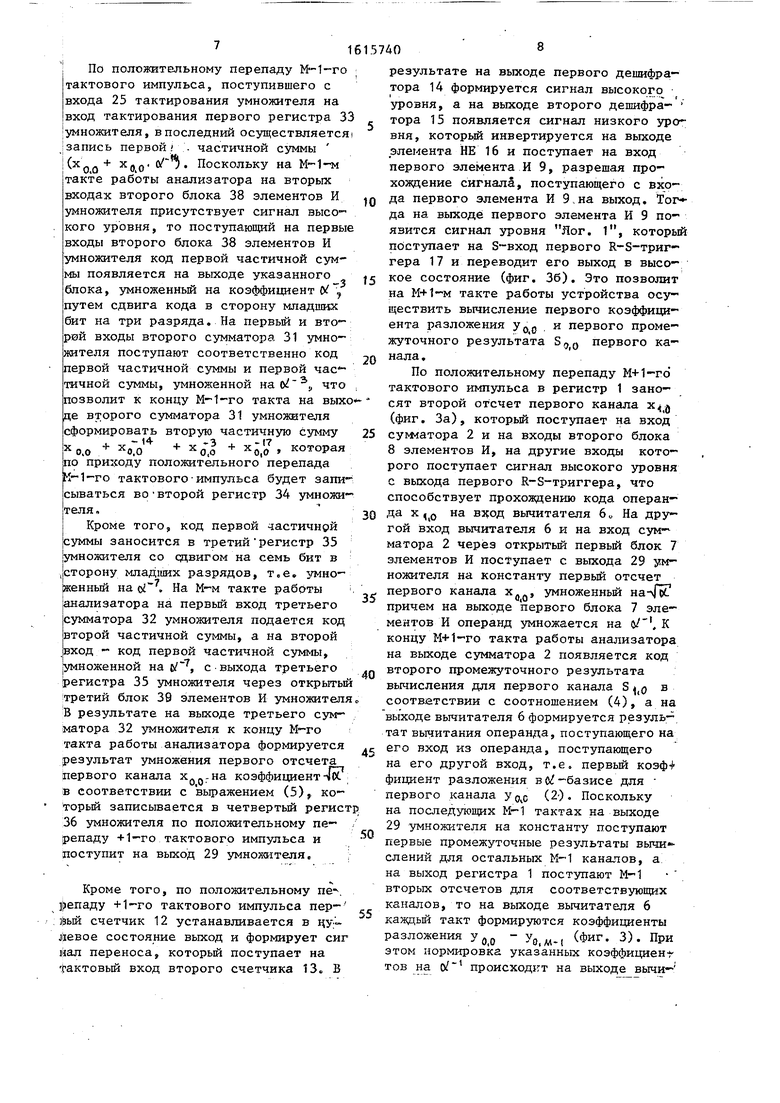

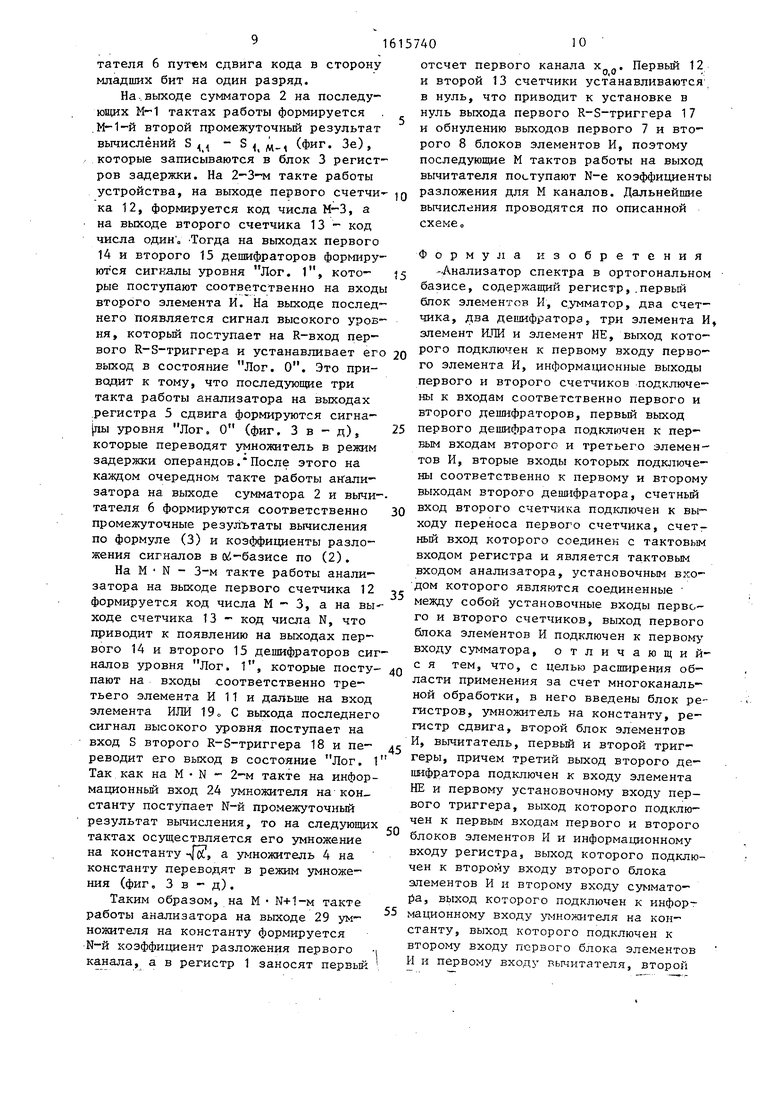

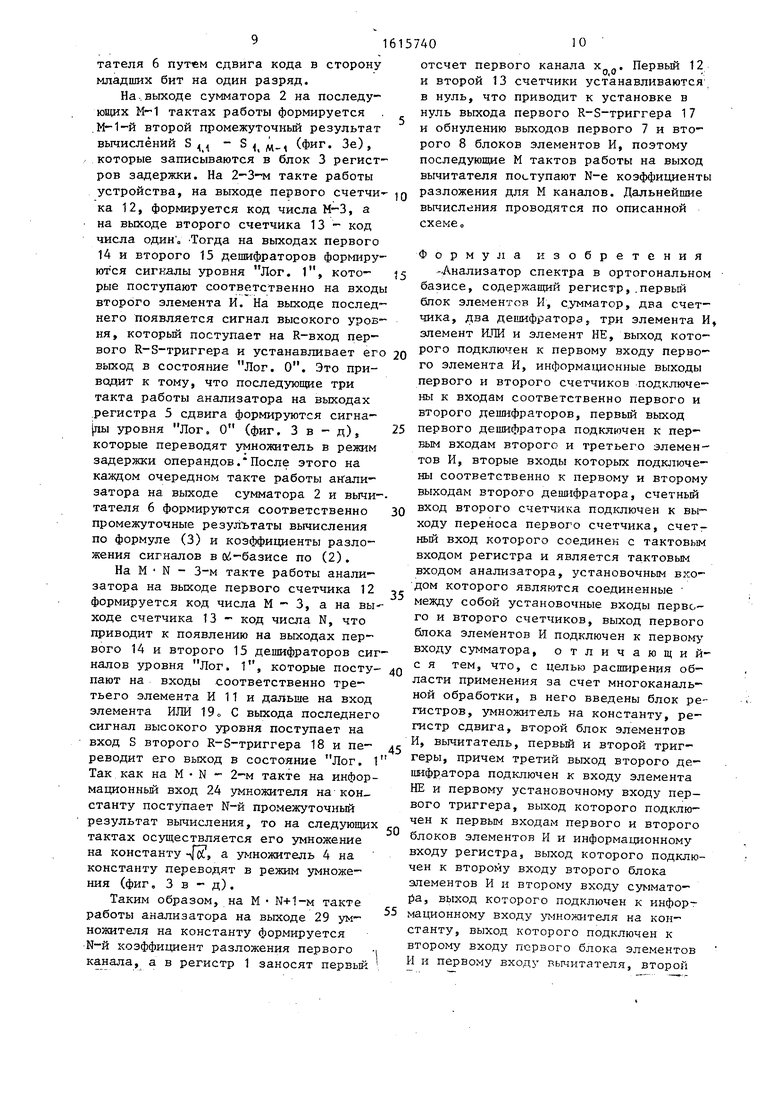

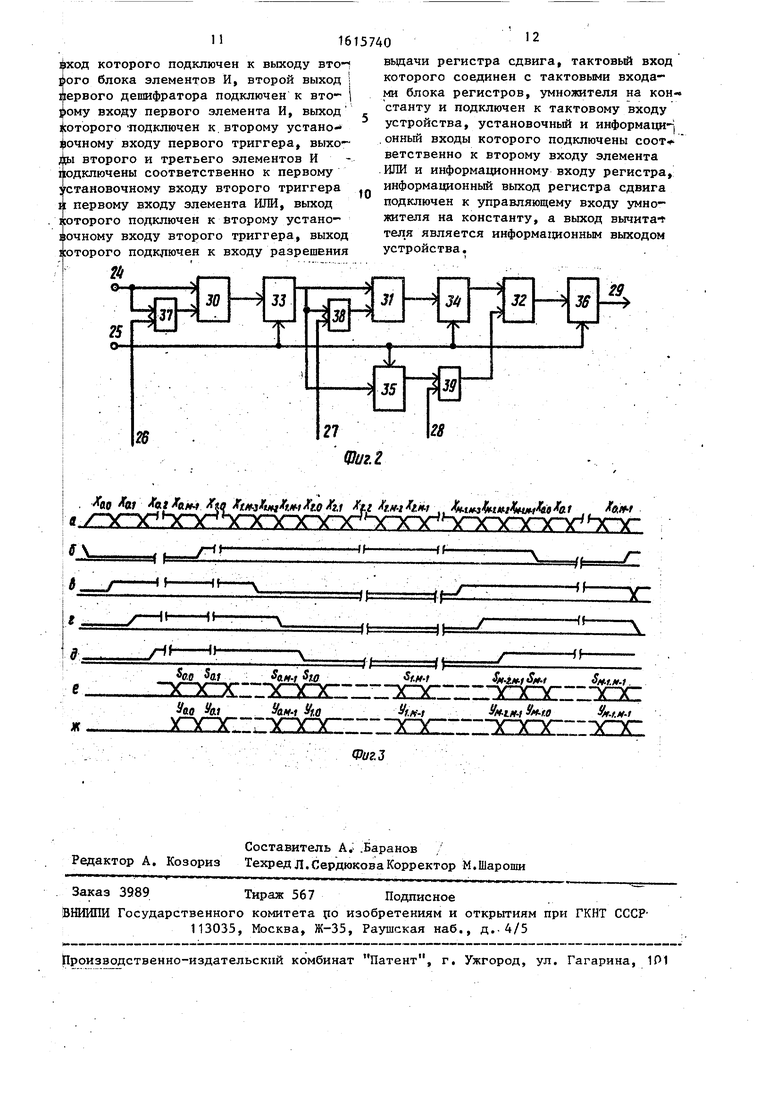

На фиг. 1 представлена структурная схема предлагаемого анализатора; на Фиг. 2 - структурная схема умножителя на константу; на фиг. 3 - временные (5 диаграммы работы анализатора

Анализатор (фиг. 1) содер;шт регистр 1, cj-MMaTop 2, блок 3 регистров (задержки), умножитель 4 на константу, регистр 5 сдвига, вычитатель 6, олоки 7 и 8 элементов И, элементы

In 1/ Дешифра--. торы 14 и 15, элемент НЕ 16, RS-триг- геры 17 и 18, элемент ИЛИ 19, информаг- ционныи вход 20 анализатора, вькод 21 анализатора, тактовый вход 22 анализатора, вход 23 начальной установки анализатора, входы 24-28 и выход 29 умножителя 4.

Умножитель 4 на константу (фиг. 2)

.вРЖИТ nv fMam/-i-r.T О/т00

5

0 содер Г атор зПГТ 33-%. я. Регистры

30 содер Г атор зПГТ 33-%. я. Регистры

35

0

.ЧА и i; регистры

33-36, блоки 37-39 элементов И, ин Формационньй вход 24 умножител, вход второГ. умножителя, первьй 2 второй 27 и третий 28 входы управле- .ния умножителя и вьпсод 29 умн ; :::,. разом Работает следующим об-

В начале работы на вход 23 началь- НОИ установки анализатора сигнал УРОВНЯ Лог. 1, которьГпода- ется на входы установки первого 12 и второго 13 счетчиков и устанавли их в нулевое состояние. Кроме того сигнал уровня Лог. 1 с вхптт;, 9 5 -ьной установки анализ т Гп д аеТ- ся на вход элемента ШЖ 19, что ПРИВОДИТ к формированию на выводе последнего сигнала уровня Лог. 1 пп ступающего на S-вход К-8.-три;гер; 18 Это устанавливает его выгкод в состояние высокого потенциала. Коды нуля с выходов первого 12 и второго 13 счет чиков поступают на входы соответств но первого 14 и второго 15 дешифра оров. что ППч-аг.гтгг,г, j.

0

РОЗ. -о-„оз,„;„;-ё „т,

- - с„™а.ьГ

уровня Лог. Г ,

Сигнал уровня Лог. 1 с выхода первого дешифратора 14 поступает на

вход первого элемента И 9, на другой вход которого подается сигнал с выхода элемента НЕ 16, Поскольку на вход :элемента НЕ 16 подан высокий потенциал с выхода второго дешифратора- 15, то на выходе элемента НЕ 16 фop fflpyeт ся сигнал уровня Лог. О, который приведен к появлению на выходе первого элемента И 9 низкого потенциала. Сигнал уровня Лог. I,,- поступающий с выхода второго дешифратора 18 на вход R R-S-триггера 12, приводит к установке последнего в нулевое состояние (фиг, 36). При этом на вход S первого R-S-триггера 12 поступает сигнал уровня Лог. О с выхода первого элемента И 9. Сигнал уровня Лог, О с выхода первого R-S-триггера 17 поступает на входы первого 7 и второго 8 блоков элементов И что приводит к формированию на выходах указанных блоков кодов нуля.

В момент прихода сигнала установки на вход 23 начальной -установки анализатора на информационный вход 20 анализатора поступает первый отсчет первого канала входных данных (фиг. За), который по положительному перепаду тактового импульса, nocTj пающего с входа 22 ..анализатора на . вход тактирования регистра 1., записывается в последний Это позволяет на первом такте работы анализатора подат на вход сумматора. 2 первый отсчет первого канала Хд. Поскольку на вход сумматора 2 поступает код нуля с выхода первого блока 7 элементов И, то операнд Xgg в конце первого такта поступает на информационный вход блока 3 регистров .задержки. По положительному перепаду второго тактового импульса в блок 3 регистров задержки записывае :еся первьй отсчет первого канала х , а в регистр 1 - первьй отсчет второго канала XQ, (фиг. За). Таким образок, через М-2 тактов с момента начала работы анализатора в блоке 3 регист1/ов задержки накапливается М-3 первых отсчетов М-2-х каналов, причем на выходе блока 3 регистров задержки появляется пер- вьш отсчет первого канала х . Последний поступает на информационный вход 24 умножителя, на первом, втором и третьем управляю дих входах которого, начиная с второго такта работы анализатора, формируются сигналы уровня : Лог. 1.

1

ь

615740

Формирование указанных сигналов ос тцествляется следующим образом. скольку на первом такте работы анали-) затора на выходе второго К-8-триггера| 13 появляется сигнал уровня Лог. 1, то на втором такте по положительному перепаду тактового импульса этот сигнал переписывается с информационного 10 входа регистра 5 сдвига в первьй его разряд, что приводит к появлению на первом его выходе сигнала уровня Лог, 1 (фкг, Зв),, который поступает на первьй вход 26 управления умножи- t5 те-пя. На третьем такте-работы анализа тора сигнал уровня Лог, 1 вновь за- гсноывается в первьй разряд регистра 5 сдвига с выхода второго R-S-триггера 18, а во второй разряд регистра 5 С сдвига переписывается сигнал уровня Лог 1 с первого его разряда. Это позволит сформировать на третьем такте на втором выходе регистра 5 сдвига уровня Лог. 1, которьй поступает на 25 второй вход 27 управления умножителя (фиг„ Зг).

Aнaлoгичны образом на. четвертом такте работы устройства на третьем выходе регистра 5 сдвига формируется 30 сигнал высокого уровня, которьй подается на третий вход 28 управления умножителя (фиг, Зд)о Такнм образом, к моменту появления на К-2-м такте ра- боты анализатора на выходе блока 3 ре- j гистров задержки: первого отсчета первого канала , которьй подается на информационньй вход 24 умножителя, первьй блок 37 элементов И умножителя открыт для прохождения операщ ов 40 благодаря присутствию на его втором входе сигнала высокого уровня, поступающего с первого входа 26 управления у1 ножителя.

Умножение первого отсчета первого 45 канала х на коэффициент vfoi осуществляется в соо7зетствии с разложением (5), при этом первая частичная сумма

0,0 , формируется на М- 2м

такте на выходе первого сумматора 30 50 множителя. На первьй вход первого сумматора 30 умножителя поступает код операнда х с информационного входа 24 умн.олм /еля, а на второй вход первого сумматора 30 умножителя по- . 55 -ступает код операнда, умноженньй на коэффиилент o -i -, путем монтажного сдвига разрядов на 14 бит в сторону. Njnaflmnx разрядов с выхода первого, блока 30 элементов И умножителя.

По положительному перепаду M-l-ro тактового импульса, поступившего с входа 25 тактирования умножителя на вход тактирования первого регистра 3 ;умножитепя, в последний осуществляетс 1запись первой/ . частичной суммы (xgg+ Поскольку на М-1-м |такте работы анализатора на вторых входах второго блока 38 элементов И умножителя присутствует сигнал высокого уровня, то поступающий на первы входы второго блока 38 элементов И умножителя код первой частичной суммы появляется на выходе указанного блока, умноженньй на коэффициент (V путем сдвига кода в сторону младших бит на три разряда. На первьй и вто- р0й входы второго сумматора 31 умножителя поступают соответственно код первой частичной суммы и первой час тичной суммы, умноженной ,, что позволит к концу М-1-го такта на вых це второго сумматора 31 умножителя

г-З

сформировать вторую частичную сумму

0.0 + М которая по приходу положительного перепада М-1-го тактового-импульса будет запи сываться вовторой регистр 34 умножи

|теля,

i;

j Кроме того, код первой частичной суммы заносится в третий регистр 35 Множителя со одвигом на семь бит в сторону младних разрядов, т.е. лгмно- 1женный на oi На М-м такте работы анализатора на первый вход третьего сумматора 32 умножителя подается код второй частичной суммы, а на второй рход - код первой частичной суммы, умноженной на ъ1, с выхода третьего регистра 35 зп ножителя через открытьй третий блок 39 элементов И умножителя В результате на выходе третьего сумматора 32 умножителя к концу М-го такта работы анализатора формируется результат умножения первого отсчета первого канала коэффициент-w ; в соответствии с вьфажением (5), который записывается в четвертый регистр 36 умножителя по положительному перепаду +1-го тактового импульса и поступит на выход 29 умнол ителя.

Кроме того, по положительному пе-. епаду +1-ГО тактового импульса пер- : }йый счетчик 12 устанавливается в цу; jleBoe состояние выход и формирует сиг иал переноса, которьй поступает на (актовьш вход второго счетчика 13. В

8

результате на выходе первого дешифратора 14 формируется сигнал высокого уровня, а на выходе второго дешифра- тора 15 появляется сигнал низкого урсг- вня, которьй инвертируется на выходе

0

0

5

элемента НЕ 16 и поступает на вход первого элемента И 9, разрешая прохождение сигнала, поступающего с входа первого элемента И 9.на выход. Тог да на выходе первого элемента И 9 появится сигнал уровня Лог. 1, который поступает на первого R-S-триг- гера 17 и переводит его выход в высо5 кое состояние (фиг. 36). Это позволит на М+1-м такте работы устройства осуществить вычисление первого коэффициента разложения УО,О первого промежуточного результата Б,, первого канала.

По положительному перепаду М+1-го тактового импульса в регистр 1 заносят второй отсчет первого канала (фиг. За), которьй поступает на вход сумматора 2 и на входы второго блока 8 элементов И, на другие входы которого поступает сигнал высокого уровня с выхода первого R-S-триггера, что способствует прохождению кода операн-

0 да X ,0 на вычитателя 6„ На другой вход вычитателя 6 и на вход сумматора 2 через открытьй первьй блок 7 элементов И поступает с выхода 29 умножителя на константу первьй отсчет

первого канала , умноженньй причем на выходе первого блока 7 элементов И операнд умножается на . К концу М+1-го такта работы анализатора на выходе сумматора 2 появляется код второго промежуточного результата вычисления для первого канала S Q в соответствии с соотношением (4), а на выходе вычитателя 6 формируется результат вычитания операнда, поступающего на его вход из операнда, поступающего на его другой вход, т.е. первьй коэф-f фициент разложения в uJ -базисе для первого канала (2). Поскольку на последующих М-1 тактах на выходе 29 зшножителя на константу поступают первые промежуточные результаты слений для остальных М-1 каналов, а на выход регистра 1 поступают М-1 вторых отсчетов для соответствующих

0

5

0

каналов, то на выходе вычитателя 6 каждьй такт формируются коэффициенты разложения у - ., (фиг. 3). При этом нормировка указанных коэффициент тов на происходит на выходе вычи-

тателя 6 путем сдвига кода в сторону младших бит на один разряд.

На..выходе сумматора 2 на последующих М- тактах работы формируется .М-1-й второй промежуточньй результат вычислений S ;(д - S , (фиг. Зе) , которые записываются в блок 3 регистров задержки. На 2-3-w такте работы

отсчет первого канала х . Первый 12 и второй 13 счетчики устанавливаются в нуль, что приводит к установке в нуль выхода первого R-S-триггера 17 и обнулению выходов первого 7 и второго 8 блоков элементов И, поэтому последующие М тактов работы на выход вычитателя поступают N-e коэффициенты

устройства, на выходе первого счетчи- JQ разложения для М каналов. Дальнейшие ка 12, формируется код числа М-3, а вычисления проводятся по описанной на выходе второго счетчика 13 - код числа один о Тогда на выходах первого 14 и второго 15 дешифраторов формируются сигналы уровня Лог. 1, кото- t5 рые поступают соответственно на входы второго элемента И. На выходе последнего появляется сигнал высокого уровсхене

Формула изобретения

-Анализатор спектра в ортогональном базисе, содержащий регистр,.первый блок элементов И, с.умматор, два счетчика, два дешифратора 5 три элемента И ня, который поступает на R-вход пер- элемент ИЛИ и элемент НЕ, выход кото- вого R-S-триггера и устанавливает его 20 подключен к первому входу перво35

выход в состояние Лог. О. Это привадит к тому, что последующие три такта работы анализатора на выходах .регистра 5 сдвига формируются сигна- лы уровня Лог. О (фиг. 3 в - д), 25 которые переводят умножитель в режим задержки операндов. После этого на кавдом очередном такте работы анализатора на выходе сумматора 2 и вычи-. тателя 6 формируются соответственно 30 промежуточные результаты вычисления по формуле (3) и коэффициенты разложения сигналов в (У -базисе по (2) .

На М N - 3-м такте работы анализатора на выходе первого счетчика 12 формируется код числа М-3, а на вы ходе счетчика 13 - код числа N, что приводит к появлению на выходах первого 14 и второго 15 дешифраторов сигналов уровня Лог. 1, которые посту- до пают на входы соответственно третьего элемента И 11 и дальше на вход элемента ИЛИ 19о С выхода последнего сигнал высокого уровня поступает на вход S второго R-S-триггера 18 и пе- 45 реводит его выход в состояние Лог. 1 Так как на М N - 2-м такте на инфор- мационньй вход 24 умножителя на константу поступает N-й промежуточный результат вычисления, то на следующих тактах осуществляется его умножение на константу -,о, а умножитель 4 на константу переводят в режим умножения (фиг, 3 в - д).

Таким образом, на М N+1-м такте работы анализатора на выходе 29 ум- ножителя на константу формируется N-й коэффициент разложения первого -, канала, а в регистр 1 заносят первьй .

го элемента И, информационные выходы первого и второго счетчиков подключены к входам соответственно первого и второго дешифраторов, первый выход первого дешифратора подключен к первым входам второго и третьего элементов И, вторые входы которых подключены соответственно к первому и второму выходам второго дешифратора, счетный вход второго счетчика подключен к выходу переноса первого счетчика, счет- ньй вход которого соединен с тактовым входом регистра и является тактовым входом анализатора, з становочным входом которого являются соединенные между собой установочные входы первого и второго счетчиков, выход первого блока элементов И подключен к первому входу сумматора, отличающий- с я тем, что, с целью расширения области применения за счет многоканальной обработки, в него введены блок регистров, умножитель на константу, регистр сдвига, второй блок элементов И, вычитатель, первьй и второй триггеры, причем третий выход второго дешифратора подключен к входу элемента НЕ и первому установочному входу первого триггера, выход которого подключен к первым входам первого и второго блоков элементов И и информационному входу регистра, выход которого подключен к второму входу второго блока элементов И и второму входу сумматора, выход которого подключен к информационному входу т жожителя на константу, выход которого подключен к второму входу первого блока элементов И и первому входу вычитателя, второй

отсчет первого канала х . Первый 12 и второй 13 счетчики устанавливаются в нуль, что приводит к установке в нуль выхода первого R-S-триггера 17 и обнулению выходов первого 7 и второго 8 блоков элементов И, поэтому последующие М тактов работы на выход вычитателя поступают N-e коэффициенты

разложения для М каналов. Дальнейшие вычисления проводятся по описанной

схене

Формула изобретения

-Анализатор спектра в ортогональном базисе, содержащий регистр,.первый блок элементов И, с.умматор, два счетчика, два дешифратора 5 три элемента И элемент ИЛИ и элемент НЕ, выход кото- 0 подключен к первому входу перво5

5 0

о 5

го элемента И, информационные выходы первого и второго счетчиков подключены к входам соответственно первого и второго дешифраторов, первый выход первого дешифратора подключен к первым входам второго и третьего элементов И, вторые входы которых подключены соответственно к первому и второму выходам второго дешифратора, счетный вход второго счетчика подключен к выходу переноса первого счетчика, счет- ньй вход которого соединен с тактовым входом регистра и является тактовым входом анализатора, з становочным входом которого являются соединенные между собой установочные входы первого и второго счетчиков, выход первого блока элементов И подключен к первому входу сумматора, отличающий- с я тем, что, с целью расширения области применения за счет многоканальной обработки, в него введены блок регистров, умножитель на константу, регистр сдвига, второй блок элементов И, вычитатель, первьй и второй триггеры, причем третий выход второго дешифратора подключен к входу элемента НЕ и первому установочному входу первого триггера, выход которого подключен к первым входам первого и второго блоков элементов И и информационному входу регистра, выход которого подключен к второму входу второго блока элементов И и второму входу сумматора, выход которого подключен к информационному входу т жожителя на константу, выход которого подключен к второму входу первого блока элементов И и первому входу вычитателя, второй

фход которого подключен к выходу вто-1 ого блока элементов И, второй выход i

tepeoro дешифратора подключен к вто- ому входу первого элемента И, выход КОТОРОГО Подключен к. второму устано- 1 очному входу первого триггера, выхо- ды второго и третьего элементов И подключены соответственно к первому установочному входу второго триггера It первому входу элемента ИЛИ, выход icoToporo подключен к второму устано- лочному входу второго триггера, выход которого подключен к входу разрешения

2

1615740 2

вьдачи регистра сдвига, тактовый вход которого соединен с тактовыми входами блока регистров, умножителя на константу и подключен к тактовому входу устройства, установочный и информаци-| онный входы которого подключены соот. ветственно к второму входу элемента ИЛИ и информационному входу регистра, информационный выход регистра сдвига подключен к управляющему входу умножителя на константу, а выход вычитав является информационным выходом устройства.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Цифровой генератор сигналов | 1984 |

|

SU1176442A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки многоканальной обработки. Цель изобретения - расширение области применения за счет многоканальной обработки данных. Поставленная цель достигается за счет того, что в состав устройства входят регистр 1, сумматор 2, блок регистров 3, умножитель на константу 4, регистр сдвига 5, вычитатель 6, блоки элементов И 7, 8, элементы И 9, 10, 11, счетчики 12, 13, дешифраторы 14, 15, элемент НЕ 16, триггеры 17, 18, элемент ИЛИ 19. 3 ил.

Н tH-iXiH., 41 ч41ч /4 м 4в Гвг

| Многоканальный релейный спектроанализатор | 1983 |

|

SU1140129A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Анализатор спектра в ортогональном базисе | 1986 |

|

SU1416982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-23—Публикация

1989-01-03—Подача