Изобретение относится к устрой ствам для обучения и может быть использовано для автоматизации процесса обучения иностранному языку.

Целью изобретения является увеличение эффективности обучения путем повыгаения быстродействия.

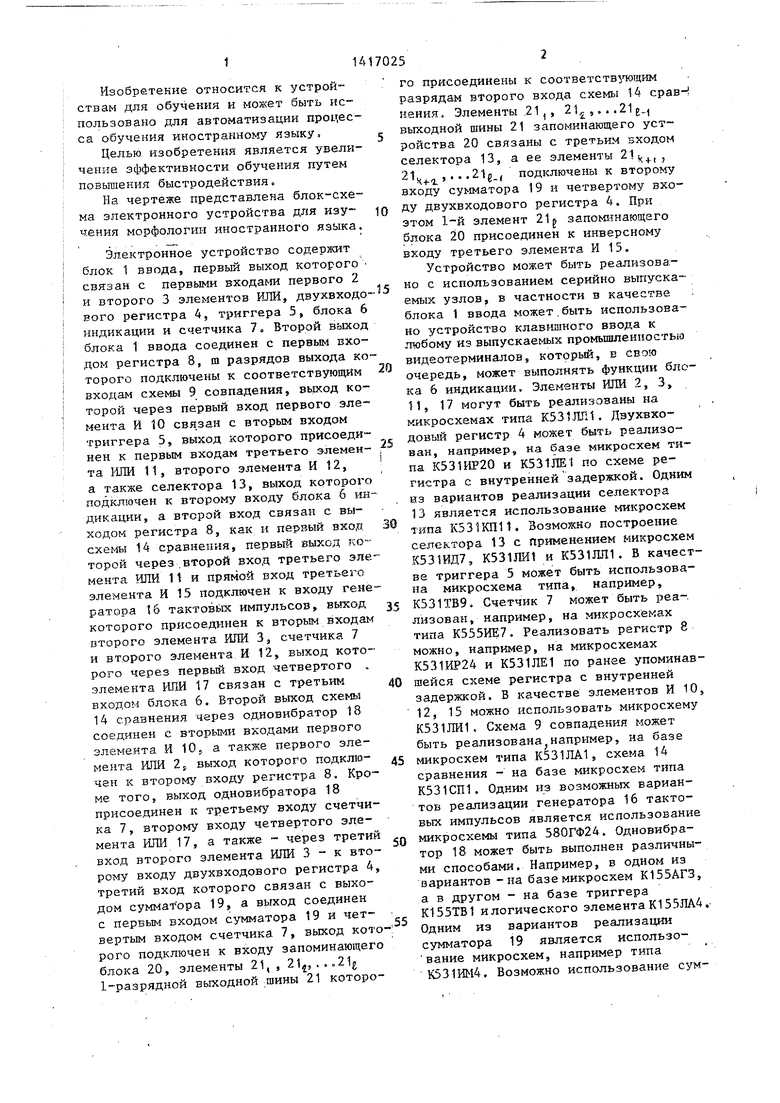

На чертеже представлена блок-схема электронного устройства для изучения морфологии иностранного языка.

Электронное устройство содержит блок 1 ввода, первьй выход которого связан с первьми входами первого 2 и второго 3 элементов ИЛИ, двухвходо вого регистра 4, триггера 5, блока 6 индикации и счетчика 7, Второй выход блока 1 ввода соединен с первым входом регистра 8, m разрядов выхода которого подключены к соответствующим входам схемы 9 совпадения, выход которой через первый вход первого элемента И 10 свя.зан с вторым входом триггера 5, выход которого присоединен к первым входам третьего элемента ИЛИ 11, второго элемента И 12, а также селектора t3, выход которого подключен к второму входу блока б индикации, а второй вход связан с выходом регистра 8, как и первый вход схемы 14 сравнения, первый выход которой через.второй вход третьего элемента ИЛИ 1t и прямой вход третьего элемента И 15 подключен к входу генератора 16 тактовьпс импульсов, вьпсод которого присоединен к вторым входам второго элемента ИЛИ 3, счетчика 7 и второго элемента И 12, выход которого через первый вход четвертого . элемента ИЛИ 17 связан с третьим входом блока 6. Второй вьпсод схемь 14 сравнения через одновибратор 18 соединен с вторыми входами первого элемента И 10, а также первого элемента ИЛИ 2f выход которого подключен к второму входу регистра 8, Кроме того, выход одновибратора 18 присоединен к третьему входу счетчика 7, второму входу четвертого элемента ИЛИ 17, а также через третий вход второго элемента ИЛИ 3 - к вто рому входу двухвходового регистра 4, третий вход которого связан с выхо дом суммат ора 19, а выход соединен с первым входом сумматора 19 и чет20

25

го присоединены к соответств:1то1ци разрядам второго входа схемь: 14 нения. Элементы ,21 , 21,...21E., - выходной шины 21 запоминающего у ройства 20 связаны с третьим вхо селектора 13, а ее элементы 21-, 21i , , . .21g( подключены к втор входу сумматора 19 и четвертому Q ду двухвходового регистра 4. При этом 1-й элемент 21 запоминающе блока 20 присоединен к инверсном входу третьего элемента И 15.

Устройство может быть реализо J5 но с использованием серийно выпу емых узлов, в частности в качест блока 1 ввода может.быть использ но устройство клавишного ввода к любому из выпускаемых промышлеииос видеотерминалов, который, в свою очередь, может выполнять функции ка 6 индикации. Элементы ИЛИ 2,

11,17 могут быть реализованы на микросхемах типа К531,Ш11. Двухвх довый регистр 4 может быть реали ван, например, на базе микросхем па К531ИР20 и К531ЛЕ1 по схеме р гистра с внутренней задержкой. О из вариантов реализации селектор

13 является использование микрос типа К531КП11. Возможно построен селектора 13 с применением микро К53ШД7, К531ЛИ1 и К531ЛЛ1 . В ка ве триггера 5 может быть использ на микросхема типа, например,

35 К531ТВ9. Счетчик 7 может быть p лизован, например, на микросхема типа К555ИЕ7. Реализовать регист можно, например, на микросхемах К531ИР24 и К531ЛЕ1 по ранее упом

40 шейся схеме регистра с внутренне

задержкой. В качестве элементов

12,15 можно использовать микрос К531ЛИ1. Схема 9 совпадения може быть реализована например, на ба

45 микросхем типа К531ЛА15 схема 14 сравнения - на базе микросхем ти К531СП1. Одним из возможных вари тов реализации генератора 16 так вых импульсов является использов

50 микросхемы типа 580ГФ24. Одновиб тор 18 может быть выполнен разли ми способами. Например, в одном вариантов -на базе микросхем К155 а в другом - на базе триггера К155ТВ1 и логического элемента К15

30

вертым входом счетчика 7, выход кото-: Одним из вариантов реализации

рого подключен к входу запоминающего блока 20, элементы 21, , 21, . 1-раэрядной выходной шины 21

.21е

которо20

25

го присоединены к соответств:1то1цим разрядам второго входа схемь: 14 сравН нения. Элементы ,21 , 21,...21E., - выходной шины 21 запоминающего устройства 20 связаны с третьим входом селектора 13, а ее элементы 21-, 21i , , . .21g( подключены к второму входу сумматора 19 и четвертому вхо- Q ду двухвходового регистра 4. При этом 1-й элемент 21 запоминающего блока 20 присоединен к инверсному входу третьего элемента И 15.

Устройство может быть реализова- 5 но с использованием серийно выпускаемых узлов, в частности в качестве блока 1 ввода может.быть использовано устройство клавишного ввода к любому из выпускаемых промышлеииостью видеотерминалов, который, в свою очередь, может выполнять функции блока 6 индикации. Элементы ИЛИ 2,3,

11,17 могут быть реализованы на микросхемах типа К531,Ш11. Двухвхо- довый регистр 4 может быть реализован, например, на базе микросхем типа К531ИР20 и К531ЛЕ1 по схеме регистра с внутренней задержкой. Одним из вариантов реализации селектора

13 является использование микросхем типа К531КП11. Возможно построение селектора 13 с применением микросхем К53ШД7, К531ЛИ1 и К531ЛЛ1 . В качестве триггера 5 может быть использована микросхема типа, например,

35 К531ТВ9. Счетчик 7 может быть pea-, лизован, например, на микросхемах типа К555ИЕ7. Реализовать регистр 8 можно, например, на микросхемах К531ИР24 и К531ЛЕ1 по ранее упоминав40 шейся схеме регистра с внутренней

задержкой. В качестве элементов И 10,

12,15 можно использовать микросхему К531ЛИ1. Схема 9 совпадения может быть реализована например, на базе

45 микросхем типа К531ЛА15 схема 14 сравнения - на базе микросхем типа К531СП1. Одним из возможных вариантов реализации генератора 16 тактовых импульсов является использование

50 микросхемы типа 580ГФ24. Одновибратор 18 может быть выполнен различными способами. Например, в одном из вариантов -на базе микросхем К155АГЗ, а в другом - на базе триггера К155ТВ1 и логического элемента К155ЛА4,

30

сумматора 19 является использо- вание микросхем, например типа К531ИМ4. Возможно использование сум; атора 19 с применением микросхем, типа К155ИП2, iv155M5, К155ЛЛ1, К155ИП2. Запоминающее устройство 20 может быть реализовано на базе стандартных микросхем типа К556РТ6.

Устройство работает след пощим образом.

При помощи блока 1 ввода обучаемый подает команду Установка. При этом на первом выходе блока 1 ввода появляется сигнал, который, поступая на первый вход блока 6 индикации, обнуляет содержимое его буферной памяти. Пройдя через элемент ИЛИ 2 на второй вход регистра 8, этот сигнал в момент спада обнуляет его содержимое. Поступая на первый вход триггера 5, сигнал сбрасывает его в О. Тот же сигнал подается на первы вход регистра 4 и - через элемент ИЛИ 3 - на второй вход того же регисра. Кроме того, данный сигнал поступает на первый вход счетчика 7, обнуляя его содержимое. Поступление кода нуля с выхода счетчика 7 на вход запоминающего блока 20 вызывает считывание из этого блока содержимого ячейки, имеющей адрес О.

Информация в запоминающем блоке 20 распределена следующим образом. Первые несколько ячеек запоминающего блока 20 представляют- собой так называемую таблицу первых букв, причем каждая 1-разрядная, ячейка является строкой данной таблицы. Первые k разрядов каждой строки этой таблицы содержат код одной буквы из числа начальных букв всех иностранных слов, изучаемых при помощи устройства. Таким образом число строк данной таблицы равно числу букв, встречаюищх- ся в начале излучаемых иностранных слоев. В разрядах с номерами от k+1 до 1-1-го каждой ячейки запоминающего блока 20 записан код, который будем называть относительным адре- сом. Пусть в одной из строк таблицы первых букв в первых k разрядах хранитс некоторая буква. Сумма относительных адресов, записанных в ячейках запоминающего блока 20 от начала таблицы первых букв и до данной фиксиро- . ванной ячейки, дает адрес начала таблицы вторых букв, относящийся к . первой букве, записанной в данной фиксированной ячейке.

Таблица вторых букв имеет структуру, сходную со структурой таблицы первых букв. Однако в первых ее разрядах записаны коды букв, встречающихся в изучаемых при помощи устройства иностранных словах на втором месте после той первой буквы, к которой относится данная таблица. Отно- сительные адреса, записанные в разрядах с номерами от k+1 до 1-1-го строк табли1и 1 вторых букв, аналогичным описан ому ранее способом осуществляют пересьшкук таблице третьих букв и т.д. Сумма относительных адресов , содержащихся в строках просматриваемой таблгахы, для последую5 щей адресации суммируется с адресом первой строки текущей таблицы. Строки буквенно-адресных таблиц заполняют таким образом, чтобы коды, записанные в k первых их разрядах, расQ полагались в порядке возрастания, т.е. в пределах одной таблшцл ячейка с большим адресом должна содержать строку с большим кодом в 1 k-M разрядах.

5 В таблицах вторых, третьих и т.д. букв может встречаться строка, в первых k разрядах которой записан код символа Конец слова (обозначим его ). Двоичный код зтого символа

Q выбран меньшим из кодов всех букв. Таким образом, строка с данным символом будет располагаться в начале бук- венно-адресной таблицы. Относительный адрес, содержащейся в ее разрядах с номерами от k+1 до 1-1-го, позволяет произвести переадресовку к началу области памяти, хранящей учебную информацию к некоторому иностранному слову, такому,что при со-: поставлении букв, входящих в его за-, пись, с буквами соответствующих бук- венно-адресных таблиц описанным способом можно получить адрес данной строки с символом ,

В каждой ячейке запоминающего бло5 ка 20 1-й разряд является маркерным. В ячейке, которая является последней строкой буквенно-адресной таблицы, или в последней ячейке области памяти, хранящей учебную информацию

0 к одному иностранному слову, данный разряд содержит 1. В остальных ; случаях маркерный разряд содержит О.

g Извлеченное из запоминающего блока 20 содержимое ячейки с адресом О представляет собой первую строку таблицы первых букв. На четвертый вход регистра 4 с элементов 21 ,

5

0

21

ц,.,2 , . . .21 g ) выходной тины 21 : запоминающего блока 20 поступает : относительный адрес записанный в нулевой ячейке. По заднему фронту сигнала, поданного на второй взсод регистра 4 через элемент ИЛИ 3 с певого выхода блока 1 ввода, этот вид относительного адреса заносится в регистр 4. С первых k элементов 2 , , . , . выходной шины 21 запоминающего блока 20 код буквы, записанной в нулевой ячейке, посту- пает на второй вход схемы 14 сравнения ,

В таком состоянии устройство находится до тех пор, пока обучаемый при помощи блока 1 ввода не введет первой буквы изучаемого слова. При этом код вводимой буквы появляется на втором выходе блока 1 ввода и записывается в регистр 8 по первому его входу. С выхода регистра 8 m разрядов этого кода поступают на соответствующие входы 9 совпадения, а через селектор 13 - на второй вход блока 6 и индикации. Кроме того., код с выхода регистра 8 подается на первый вход схемы 14 сравнения, ЕСЛИ код буквы, введенной обучаемым, равен коду, поданному на второй вход схемы 14 сравнения, на ее втором выходе появляется сигнал, поступающрш на вход одновибратора 18 и вызывающий формирование на его выходе импульса, который через элемент ИЛИ 17 проходит на третий вход блока 6 индикации. По его спаду в буферную память блока 6 индикации записывается код, поданный на второй его вход, и на экране блока 6 индикации появляется изображение введенной обучаемым буквы. Появление изображения является сигналом к вводу следующей буквы слова. Кроме того, импульс с выхода одновибратора 18 через элемент ИЛИ 2 поступает на второй вход регистра Вив момент спада обнуляет его содержимое. Сигнал с выхода од- новибратора 18 через элемент ИЛИ 3 подается также на второй вход регистра 4. Тот же сигнал проходит на третий вход счетчика 7, При этом в счетчик 7 заносится адрес, записанный в регистр 4. С выхода счетчика 7 данный адрес поступает на вход запоминающего блока 20. При этом из запоминающего блока 20 считывается содержимое ячейки, которая содержит

-

4170256

первую строку таблицы вторых букв, соответствующей первой букве, введенной обучаемым. С элементов 21,, шины 21

10

15

20

21ц.,i 2 g, шины /1 на второй вход сумматора 19 подается относительный адрес, записанный в считанной строке таблицы. На первый вход сумматора 19 с выхода регистра 4 подается код адреса считанной строки. Таким образом, с выхода сумматора 19 на третий вход регистра 4 поступает сумма этих кодов, которая записывается в регистр 4 в момент спада сигнала на выходе одновибратора 18. В таком состоянии устройство находится до тех пор, пока обучаемый не введет вторую букву иностранного слова. Устройство при этом работает в последовательности, аналогичной описанной ранее.

5

0

5

0

0

5

, Если код буквы, введенной обучае- , оказывается больше кода, записанного в k первых разрядах считанной строки букве нно-адресной таблицы, то сигнал единичного уровня формируется на первом выходе схемы 14 сравнения , Пройдя через элемент ИЛИ 11 и открытый элемент И 15, он включает генератор 16 тактовьпс импульсов. Импульсы с его выхода поступают на зторой вход счетчика 7 и через элемент ИЛИ 3 - на второй вход регистра 4, Содержимое счетчика 7 при этом увеличивается на единицу. Вследствие этого из запоминающего блока 20 считывается следующая строка просматриваемой буквенно-адресной таблицы. По заднему фронту тактового импульса, поданного на второй вход регистра 4, аналогичным рассмотренному ранее образом содержимое регистра 4 увеличивается на величину относительного адреса, записанного в считанной 5 строке буквенно-адресной таблицы.

Последующие тактовые импульсы обеспечивают последовательный просмотр буквенно-адресной таблицы до тех пор, пока из запоминающего блока 20 не будет считана строка, в k первых разрядах которой записан код буквы, совпадающей с кодом, введенным облучаемым. В этом случае сигнал на первом выходе схемы 14 сравнения исчезает и генератор 16 останавливается. Появляется сигнал на втором выходе схемы 14 сравнения. Далее устройство работает в порядке, который уже рассматривался .

В случае, если запоминающий блок 20 не содержит учебной информации к вводимому слову, в просматриваемой буквенно-адресной таблице строка с введенной обучаемым буквой отсутствует. При извлечении из запоминающего блока 20 последней строки таблицы на элементе 21 шины 21 появляется Лог, 1, которая, поступив на инвернсый вход элемента И 15, закрывает его, вследствие чего генератор 16 останавливается. Изображение вводимой обучаемым буквы на экране блока 6 индикации не появляется, что служит для обучаемого сигналом отсутствия необходимой информации .

Если код введенной обучаемым буквы оказывается меньше кода, поданного на второй бход схемы 14 сравне- .Нин, то изображение введенной обучаемым буквы на экране блока 6 индикации также не воспроизводится. Ввод изучаемого слова в, этом случае необходимо прекратить и перейти к изучению другого иностранного слова.

В случае, если на экране блока 6 индикации воспроизведено все введенное слово, обучаемый при помощи блока 1 ввода вводит символ . Если информация к данному слову в устройстве имеется, то к моменту ввода символа из запоминающего блока 20 уже считана строка с этим символом в k первых разрядах. С элементов 21,, 2,.,.2 шины 21 этот код подается на второй вход схемы 14 сравнения. Такой же код появляется на выходе регистра 8, откуда он поступает на первый вход схемы 1А сравнения и входы схемы 6 совпадения. На выходе схемы 9 совпадения при этом появляется Лог. 1, открывающая элемент И 10. Вследствие равенства кодов на входах схемы 14 сравнения на ее втором выходе появляется сигнал, формирующий на выходе одновиб- ратора 18 импульс, который проходит через элемент И 10 на второй вход триггера 5. На выходе триггера 5 устанавливается Лог. 1, которая поступает на первый вход селектора 13 и переключает его, а поступая на первый вход элемента И 12, открывает последний. Кроме того, сигнал с выхода одновибратора 18 поступает на третий вход счетчика 7 и в последний из регистра 4 заносится адрес начала области памяти, содержащей

5

0

информацию к введенному слову. Из запоминающего блока 20 считывается содержимое первой ячейки, хранящей

информацию к изучаемому слову. С элементов 21 , 2 . , , ,. шины 21 оно через селектор 13 поступает на второй вход блока 6 индикации. По спаду с тгнала, поданного на тре- тий вход блока 6 индикации через элемент ИЛИ 17 с выхода одновибратора 18, учебная информация воспроизводится на экране. Изменение кодов, подаваемых на входы схемы 14 сравнения, вызывает исчезновение сигнала на ее втором вь)ходе. Лог. 1 с выхода триггера 5 через элемент ШШ 11 и открытый элемент И 15 запускает генератор 16 тактовых импульсов. Поступление тактового импульса на второй вход счетчика 7 влечет считывание из запоминающего блока 20 следующей порции учебной информации, записанной в следующей ячейке памяти. По

- спаду тактового импульса, проходящего через открытый элемент И 12 и элемент, ИЛИ 17 на третий вход блока 6 индикации, на его экране воспроизводится данная информация. Так происходит до тех пор, пока на некотором

такте из запоминающего блока 20 не считывается содержимое последней ячейки с нужной учебной информацией. Содержащаяся в ее маркерном разряде Лог. 1 с элемента 21 шины 21 по5 ступает на инверсный вход элемента И 15, который закрывается, отключив генератор тактовых импульса.

Таким образом, предлагаемое устройство позволяет автоматизировать процесс изучения морфологии иностранного языка, причем в отличие от прототипа изучаемая информация может предъявляться обучаемому в порядке, предусмотренном учебной программой, а не в зависимости от место- Положения данной информации в запоми- нающем устройстве. Кроме того, отсутствие ограничений на объем учеб- ной информации, относящейся к одному иностранному слову, позволяет приводить изучающему несколько синонимов перевода, дополняя их при необходимости грамматическими сообщения

ми и т.п. по сравнению с прототипом устройство обладает большей надеж- . ностью благодаря упрощению его конструкции, а также более высоким

быстродействием, так как для выборки нужной информации не требуется последовательного просмотра всех ячеек запоминающего устройства.

Следовательно, по сравнению с прототипом электронное устройство обладает расширенными функциональными возможностями и областью применения, что достигнуто повьшением эффектив- ности его применения в процессе изучения языка, повышением надежности и быстродействия.

Форм у л а изобретения

Электронное устройство для изучения морфологии иностранного языка, содержащее блок ввода, регистр, счет

чик, запоминающий блок, элементы И, блок индикации и элемент ИЛИ, о т- ли чающееся тем, что, с целью увеличения эффективности обучения путем повьппения быстродействия устройства, в него введены дополнительные элементы ИЛИ, схема совпадения, схема сравнения, одновибратор триггер, селектор, генератор тактовых импульсов, двухвходовый регистр и сумматор, причем первый выход блока ввода связан с первыми входами первого и второго элементов ИЛИ, двух- входового регистра, триггера, блока индикации и счетчика, второй выход блока ввода соединен с первым входом регистра, выход которого подключен к входу схемы сравнения, первому входу селектора и соответствующим входам схемы совпадения, а выход последней через первый вход первого элемен

та И связан с вторым выходом триггера, при этом выход триггера подсоединен к первым входам третьего элемента ИЛИ, второго элемента И и к второму входу селектора, выход которого подключен к второму входу блока индикации, причем первый вход схемы сравнения через второй вход третьего элемента ИЛИ и прямой вход третьего элемента И подключен к входу генератора тактовых импульсов, выход которого присоединен к вторым входам второго элемента ИЛИ, счетчика и второго элемента И, а выход второго элемента И через первый вход четвертого элемента ИЛИ связан с третьим входом блока индикации, при этом второй выход схемы сравнения через одновибратор соединен с вторыми входами первого элемента И и первого элемента ИЛИ, выход которого подключен к второму входу регистра, а выход одно- вибратора присоединен к третьему входу счетчика, второму входу четвертого элемента ИЛИ и к третьему входу второго элемента ИЛИ, связанного выходом с вторым входом двухвходового регистра,.причем третий вход двухвходового регистра связан с выходом сумматора, а выход - с первым входом сумматора и через четвертый вход счетчика - с входом запоминающего блока, при этом соответствующие выходы запоминающего блока связаны с третьим вxoдoм селектора, вторым входом сумматора, четвертым входом двухвходового регистра, с инверсным входом третьего элемента И и вторым входом схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| Устройство для изучения лексики иностранного языка | 1987 |

|

SU1443016A1 |

| Электронный словарь для изучения иностранного языка | 1989 |

|

SU1649568A1 |

| Устройство для обучения иностранным языкам | 1989 |

|

SU1741154A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1559367A1 |

| Устройство для обучения иностранным языкам | 1987 |

|

SU1594585A1 |

| Устройство для изучения слов иностранного языка | 1987 |

|

SU1495815A1 |

| Устройство для обучения иностранным языком | 1989 |

|

SU1649591A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1532965A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1702394A1 |

Изобретение относится к устройствам для обучения, и может быть использовано для автоматизации процесса обучения иностранному языку. Целью изобретения является увеличеиле эффективности обучения путем повышения быстродействия. Электронное устройство для изучения морфологии иностранного языка содержит блок 1 ввода, первьш элемент ИЛИ 2, второй элемент ИЛИ 3, двухвходовый регистр 4, триггер 5, блок 6 индикации, счетчик 7, регистр 8, схему 9 совпадения, первый элемент И 10, третий элемент ИЛИ 11, второй элемент И 12, селектор 13, схему 14 сравнения, третий элемент И 15, генератор 16 тактовых импульсов, четвертый элемент ИЛИ 17, одновибратор 18, сумматор 19, запоминающий блок 20 с выходной шиной 21. 1 ил. (Л 4 Ч

| Патент ФРГ № 3103827, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-08-15—Публикация

1986-12-18—Подача