ю

12

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках быстро- ;|1ействую1цих вычислительных машин. Цель изобретения - расширение, функциональных возможностей за счет изменения двоичного числа на единицу й оиэвольного разряда и выявления переполнения разрядной сетки и отрица- фельного результата.

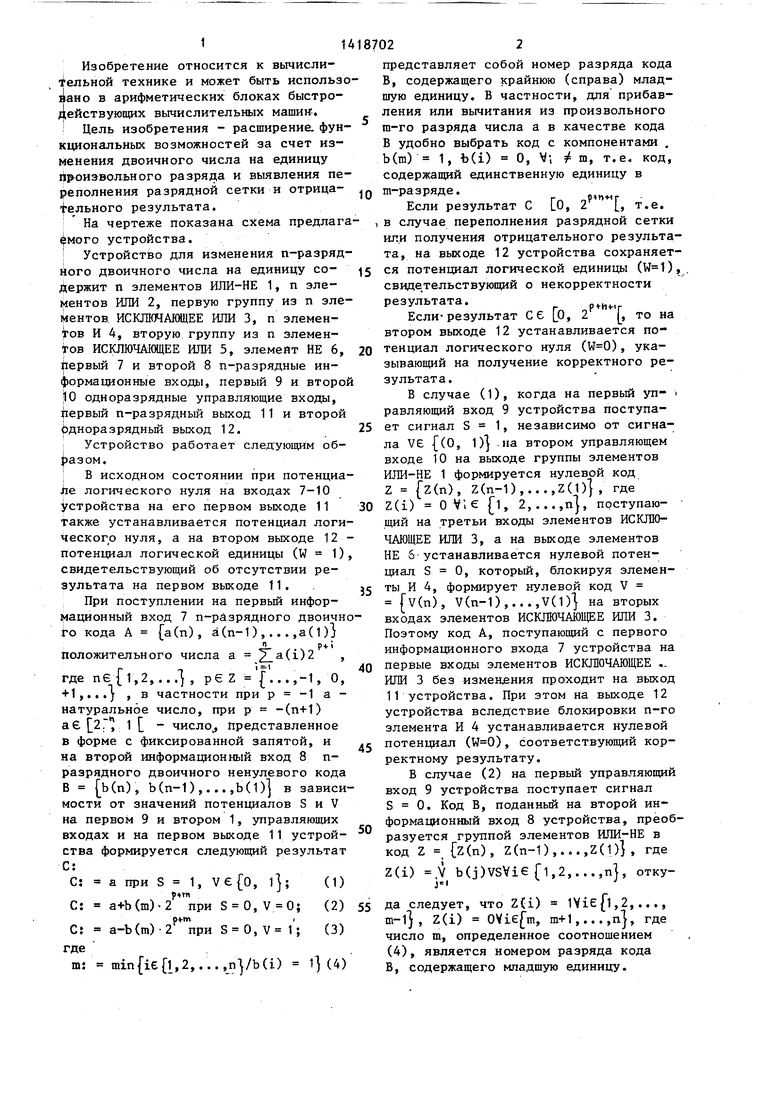

На чертеже показана схема предлага- мого устройства.

I Устройство для изменения п-разряд- його двоичного числа на единицу со- Держит п элементов ИЛИ-НЕ 1, п элементов ИЛИ 2, первую группу из п эле- iieHTOB. ИСКЛЮЧАЮЩЕЕ ИЛИ 3, п элементов И 4, вторую группу из п элеменпредставляет собой номер разряда кода В, содержащего крайнюю (справа) младшую единицу. В частности, для прибавления или вычитания из произвольного га-го разряда числа а в качестве кода В удобно выбрать код с компонентами , Ь(ш) 1, Ъ(1) О, V; т т, т.е. код, содержащий единственную единицу в

Шт-разряде. Г

Если результат С LO, 2 | т.е. в случае переполнения разрядной сетки или получения отрицательного результа та, на выходе 12 устройства сохраняет 5 ся потенциал логической единицы () свиде тельствующий о некорректности результата.

г P ht-tr

Если-результат С6 0, 2 , то на втором выходе 12 устанавливается поТов ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент НЕ 6, 20 тенциал логического нуля (), ука25

J5

первый 7 и второй 8 п-разрядные информационные входы, первый 9 и второй 10 одноразрядные управляющие входы, рервый п-разрядный выход 11 и второй одноразрядный выход 12. : Устройство работает следующим образом.

I В исходном состоянии при потенциале логического нуля на входах 7-10 устройства на его первом выходе 11 30 также устанавливается потенциал логического нуля, а на втором выходе 12 - потенциал логической единицы (W 1), свидетельствующий об отсутствии результата на первом выходе 11.

При поступлении на первый информационный вход 7 п-разрядного двоичного кода А {а(п), а(п-1),...,а(1)j

п Р положительного числа а a(i)2 ,

где п6 {l,2,... , ре Z {...,-1, О, ,...) , в частности при р -1 а - натуральное число, при р -(п+1) а 2Г 1 - число. Представленное в форме с фиксированной запятой, и на второй информационный вход 8 п- разрядного двоичного ненулевого кода В Ь(п), Ь(п-1),...,Ь(1)j в зависимости от значений потенциалов S и V на первом 9 и втором 1, управляющих входах и на первом выходе 11 устройства формируется следующий результат С:

а при S 1, Ve{0, (1)

С: С:

р4П1

a+b(m)2 при8 0,У 0;

р4-т

при S О, V 1;

(2) (3)

С; a-b(m) -2 где т: min{ieQ,2,...,nyb(i) 1 (4)

зывающий на получение корректного результата.

В случае (1), когда на первый уп- равляющий вход 9 устройства поступает сигнал , независимо от сигнала V {(О, 1)j .на втором управляющем входе 10 на выходе группы элементов ИЛИ-НЕ 1 формируется нулевой код Z Z(n), Z(n-1),...,Z(1) , где Z(i) О Vl е , 2,...,nj, поступающий на третьи входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, а на выходе элементов НЕ 6-устанавливается нулевой потенциал , который, блокируя элементы И 4, формирует нулевой код V V(n), V(n-1),...,V(1) на вторых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3. Поэтому код А, поступающий с первого информационного входа 7 устройства на

40 первые входы элементов ИСКЛЮЧАЮЩЕЕ ., ИЛИ 3 без изменения проходит на выход 11 устройства. При этом на выходе 12 устройства вследствие блокировки п-го элемента И 4 устанавливается нулевой

д5 потенциал (), соответствующий корректному результату.

В случае (2) на первый управляющий вход 9 устройства поступает сигнал . Код В, поданный на второй ин формационный вход В устройства, преоб разуется группой элементов ИЛИ-НЕ в код Z {z(n), Z(n-1),...,Z(1) , где

Z(i) ,V b(j)V8Vie Г1,2,...,п, отку- j-i - J

55 да следует, что Z(i) ,2

m-1), Z(i) OViefm, m+1,...,n, где число m, определенное соотношением (4), является номером разряда кода В, содержащего младшую единицу.

представляет собой номер разряда кода В, содержащего крайнюю (справа) младшую единицу. В частности, для прибавления или вычитания из произвольного га-го разряда числа а в качестве кода В удобно выбрать код с компонентами , Ь(ш) 1, Ъ(1) О, V; т т, т.е. код, содержащий единственную единицу в

т-разряде. Г

Если результат С LO, 2 | т.е. в случае переполнения разрядной сетки или получения отрицательного результа,- та, на выходе 12 устройства сохраняет- 5 ся потенциал логической единицы (), свиде тельствующий о некорректности результата.

г P ht-tr

Если-результат С6 0, 2 , то на втором выходе 12 устанавливается по5

5

0

зывающий на получение корректного результата.

В случае (1), когда на первый уп- равляющий вход 9 устройства поступает сигнал , независимо от сигнала V {(О, 1)j .на втором управляющем входе 10 на выходе группы элементов ИЛИ-НЕ 1 формируется нулевой код Z Z(n), Z(n-1),...,Z(1) , где Z(i) О Vl е , 2,...,nj, поступающий на третьи входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, а на выходе элементов НЕ 6-устанавливается нулевой потенциал , который, блокируя элементы И 4, формирует нулевой код V V(n), V(n-1),...,V(1) на вторых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3. Поэтому код А, поступающий с первого информационного входа 7 устройства на

0 первые входы элементов ИСКЛЮЧАЮЩЕЕ ., ИЛИ 3 без изменения проходит на выход 11 устройства. При этом на выходе 12 устройства вследствие блокировки п-го элемента И 4 устанавливается нулевой

5 потенциал (), соответствующий корректному результату.

В случае (2) на первый управляющий вход 9 устройства поступает сигнал . Код В, поданный на второй информационный вход В устройства, преобразуется группой элементов ИЛИ-НЕ в код Z {z(n), Z(n-1),...,Z(1) , где

Z(i) ,V b(j)V8Vie Г1,2,...,п, отку- j-i - J

5 да следует, что Z(i) ,2

m-1), Z(i) OViefm, m+1,...,n, где число m, определенное соотношением (4), является номером разряда кода В, содержащего младшую единицу.

3141

При наличии на втором управляющем входе 10 сигнала V О код А пер вого информационного входа 7 про- Jзycкaeтcя без изменения второй группой элементов ИСКЛЮЧАЮ Е ИЛИ 5 на вторые входы элементов ИЛИ 2. Вследствие поступления на первые входы элементов ИЛИ 2 кода Z на их выходах формируется код

и u(i)/U(i) Z(i)Va(i)Vie{l,2,

..., n.(5)

где U(i) 1 V ie l ,2,... ,m-l, U(i) a(i)V , m+1,...,n1.

Проходя через элементы И 4, n-1 мпадших разрядов кода U преобразуются в п-1 старших разрядов кода V, младший разряд которого определяется сигналом S 1 с выхода элемента НЕ 6. Код V (n), V(n-1),..., V(1), где

C(i) a(i)® V(i)ez(i)

0

702

V(1) S 1, V(i) au(j)&SVie{2, 3,...,nl, поступающий на вторые входы ; элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, содержит единицы в К младших разрядах и нули в (п-К) старших разрядах, где

К: ,m+1,... ,n}/U(i) a(i)

m(6)

представляет собой номер разряда младшего нуля кода U. Код Z, поступа- ющий на третьи входы элементов ИСКЛЮ- ЧАЩЕЕ ИЛИ 3, содержит единицы в т-1 младших разрядах и нули в п-т+1 старших разрядах. Следовательно, код А, поступающий с первого информационного входа 7 устройства на первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 преобразуется ими в код с fc(n), С(п-1), ..., C(1)j и вьщается на первый выход 11 устройства, причем для этого кода

5

«a(i)iefl, 2m-l ;

a(i), m+l,..., a(i), k+2n ;

(7)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1986 |

|

SU1381497A1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680762C1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для решения краевых задач | 1985 |

|

SU1317451A1 |

| Вероятностный коррелометр | 1986 |

|

SU1327121A1 |

| УСТРОЙСТВО КАСКАДНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ, ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА И МАКСИМАЛЬНЫХ ГРУПП | 2019 |

|

RU2701709C1 |

| Устройство для декодирования кода | 1983 |

|

SU1190525A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1233144A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1575177A1 |

| УСТРОЙСТВО ПИРАМИДАЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2703335C1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках быстродействующих вычислительных машин. Цель изобретения - расширение функциональных возможностей за счет изменения двоичного числа на единицу произвольного разряда и выявления переполнения разрядной сетки и отрицательного результата. Ус фойство содержит п элементов ИЛИ-НЕ 1, п элементов ИЛИ 2, две группы по п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 5 и элемент НЕ 6. На первый информационный вход устройства подается п-разрядное двоичное число, на второй - п-разрядный управляющий код, содержащий единственную единицу в том разряде, в котором производится ее подсуммирование или вычитание. На первый одноразрядный управляющий вход поступает сигнал, разрешения изменения исходного кода, а на второй - знак этого изменения. На п-разрядном выходе устройства формируется код выходного числа, измененного на единицу разряда, который определен управляющим кодом, или код исходного числа без изменения. На одноразрядный выход устройства поступает сигнал при наличии переполнения разрядной сетки при подсуммировании или получении отрицательного результата при вычитании. 1 ил. и

С другой стороны, в силу правила переноса при суммировании двоичных чисел, точно такие же вьфажения характеризуют разряды C(i) двоичного числа С, определенного соотношением (2), т.е. код С является искомым.

Одновременно с формированием кода V п-й элемент И 4 вьфабатывает на выходе 12 устройства.сигнал

. W а u(i))&S,

соответствующий логическому нулю, если указанное число К существует, и ло- логической единице, если такого числа не существует, т.е. имеет место переполнение разрядной сетки результата 45

В случае (3), когда на первый управляющий вход 9 устройства поступает сигнал , а на второй управляющий вход 10 сигнал V 1, код А инвертируется второй группой элементов ИС- gQ КЛЮЧАЮЩЕЕ ИЛИ 5, В результате чего на выходах элементов ИЛИ 2 формируется код.

и fu(i)/U(i) Z(i)Va(i),2,

...,nl,(9)

где U(i) 1 V ,2,...,m-l, U(i) a(i)V i-e (m,n+1,,..,n.

30

35

40

-45

gQ

55

Код V, поступающий на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, так же как и в случае (2), содержит единицы в К младших разрядах и нули (п-К) старших разрядах, где

К: . m+1,...,UJ/U(i)

i(i) (10)

i

является номером разряда младшего

нуля кода и, определенного выражением (9). Различие между соотношениями (10) и (6) заключается в замене значений a(i) на инвертированные a(i): 1-a(i). На выходе 11 устройства формируется код С, характеризуемый соотношениями (7) и отличающийся от аналогичного кода в случае (2) только тем, что число К задано сооттг ношением (10),. а не (7). В соответствии с правилами переноса при вычитании двоичных чисел соотношение (7) при условии (10) определяет разряды C(i) двоичного числа С, вычисляемого по формуле (3). Сигнал W в соответствии с (8) на выходе 12 устройства в данном случае принимает нулевое зна- чение при аЬ О и единичное при а-г-О.

Для повышения регулярности « однородности структуры устройства при его реализации в виде интегральной

схемы целесообразно (на основании закона де Моргана) заменить каждый элемент И 4 и каждый элемент ИЛИ 2 на элемент ИЛИ-НЕ с тем же числом входов

Формула изобретения

Устройство для изменения п-раз- рядного двоичного числа на единицу, ;содержащеё первую группу из п эле- |ментов ИСКЛЮЧАЮЩЕЕ ИЛИ, п-1 элементов И, вторую группу из п-1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы (Vie{l, 2,...,n-ll) соединен с i-м разрядом первого информационного входа устройства вто- вход каждого элемента ИСКЛЮЧАЮ- 1ЦЕЕ ИЛИ второй группы подключен к |второму управляющему входу устройст- |ва, выход i-ro элемента И подключен |к второму входу (i+1 )-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первый вход j-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы (VJ cfl, 2,... ,п ) сое,- динен с J-M разрядом первого ийформа- 1ЦИОННОГО входа устройства, а его выход - с J-M разрядом выхода результата устройства, отличающее- € я тем, что, с целью расширения ; функциональных возможностей за счет изменения двоичного числа на единицу

5

0

5

5 зо

0

произвольного разряда и выявления переполнения разрядной сетки и отрицательного результата, введены п элементов ШШ-НЕ, п элементов ИЛИ элемент НЕ, п-й элемент И и п-й элемент ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, причем вход элемента НЕ соединен с первым управляющим входом устройства и первым входом каждого элемента Ш1И-НЕ, выход элемента НЕ соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы и первым входом, каждого элемента И, Ос+1)-й вход j-ro элемента ИЛИ-НЕ (Vkefl ,2,..., jj) соединен с k-M разрядом второго информационного входа устройства, выход j-ro элемента ШШ-НЕ соединен с третьим входом j-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы и вторым входом j-ro элемента ИЛИ, первый вход которого соединен с выходом j-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, а выход - с (j+1)-M входом га-го элемента И (Vm6|j, j+1,..., п1), выход п-го элемента И является выходом индикации устройства, а первый и второй входы п-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы подключены соответственно к п-му разряду первого информационного входа устройства и второму управляющему входу устройства.

| Устройство для вычитания издВОичНОгО чиСлА пОСТОяННОгО КОдА,РАВНОгО дВуМ | 1979 |

|

SU800991A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для изменения @ -разрядного двоичного числа на единицу | 1981 |

|

SU995089A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-05—Подача