&0

31

о

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметичес- .ких устройствах для выполнения операции депения чисел.

Целью изобретения является сокращение количества оборудования.

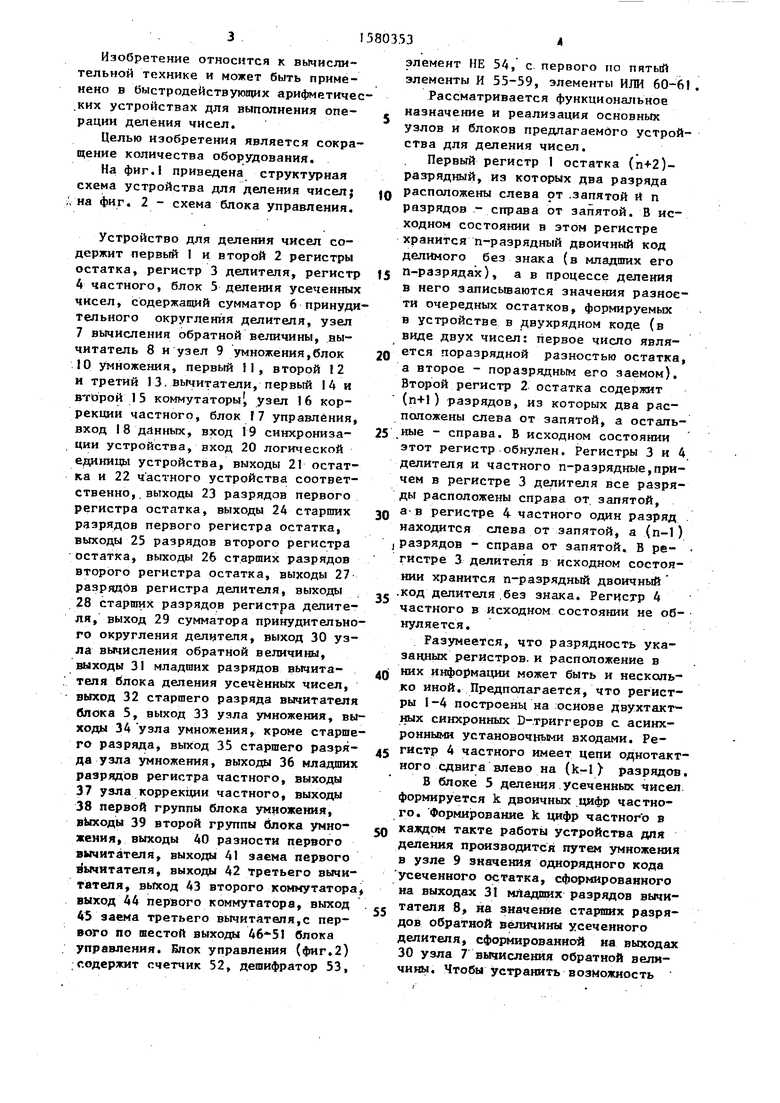

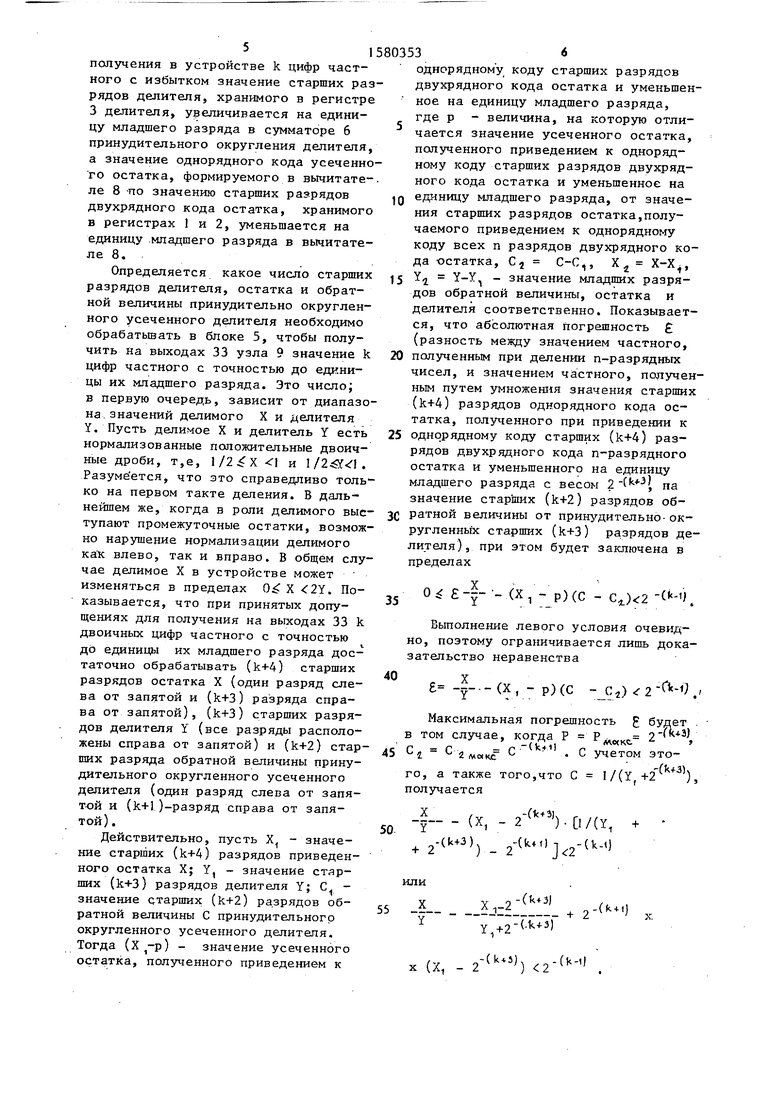

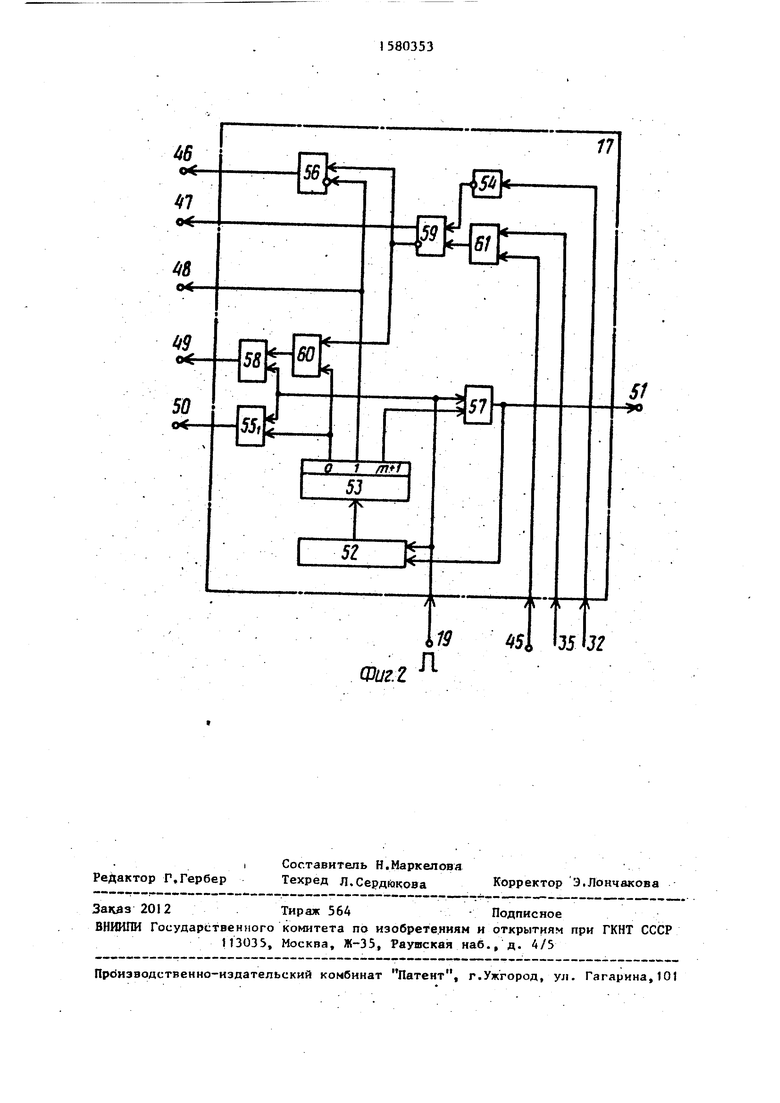

На фиг.1 приведена структурная схема устройства для деления чисел; на фиг. 2 - схема блока управления.

Устройство для деления чисел содержит первый I и второй 2 регистры остатка, регистр 3 делителя, регистр 4 частного, блок 5 деления усеченных чисел, содержащий сумматор 6 принудительного округления делителя, узел 7 вычисления обратной величины, вы- читатель 8 и узел 9 умножения,блок 10 умножения, первый 11, второй 12 и третий 13. вычитатели, первый 14 и второй 15 коммутаторы , узел 16 коррекции частного, блок Г7 управления, вход 18 данных, вход 19 синхронизации устройства, вход 20 логической единицы устройства, выходы 21 остатка и 22 частного устройства соответственно, выходы 23 разрядов первого регистра остатка, выходы 24 старших разрядов первого регистра остатка, выходы 25 разрядов второго регистра остатка, выходы 26 старших разрядов второго регистра остатка, выходы 27 разрядив регистра делителя, выходы 28 старших разрядов регистра делителя, выход 29 сумматора принудительного округления делителя, выход 30 узла вычисления обратной величины, выходы 31 младших разрядов вычита- теля блока депения усечённых чисел, выход 32 старшего разряда вычитателя блока 5, выход 33 узла умножения, выходы 34 узла умножения, кроме старшего разряда, выход 35 старшего разряде узла умножения, выходы 36 младших разрядов регистра частного, выходы

37узла коррекции частного, выходы

38первой группы блока умножения, выходы 39 второй группы блока умножения, выходы 40 разности первого вычитателя, выходы 41 заема первого вычитателя, выходы 42 третьего вычитателя, выход 43 второго коммутатора выход 44 первого коммутатора, выход 45 заема третьего вычитателя,с первого по шестой выходы блока управления. Блок управления (фиг.2) содержит счетчик 52, дешифратор 53,

элемент НЕ 54, с первого по пятый элементы И 55-59, элементы ИЛИ 60-61.

Рассматривается функциональное назначение и реализация основных узлов и блоков предлагаемого устройства для деления чисел.

Первый регистр 1 остатка (п+2)- разрядный, из которых два разряда расположены слева от .запятой и n разрядов - справа от запятой. В исходном состоянии в этом регистре хранится n-разрядный двоичный код делимого без знака (в младших его 5 n-разрядах), а в процессе деления в него записываются значения разное- ти очередных остатков, формируемых в устройстве в двухрядном коде (в виде двух чисел: первое число явля- 0 ется поразрядной разностью остатка, а второе - поразрядным его заемом). Второй регистр 2 остатка содержит (п+1 ) разрядов, из которых два расположены слева от запятой, а осталь- 5 ,ные - справа. В исходном состоянии этот регистр обнулен. Регистры 3 и 4 делителя и частного п-разрядные,причем в регистре 3 делителя все разряды расположены справа от запятой, 0 а-в регистре 4 частного один разряд находится слева от запятой, а (п-1) j разрядов - справа от запятой. В ре- гистре 3 делителя в исходном состоянии хранится n-разрядный двоичный . .код делителя без знака. Регистр 4 частного в исходном состоянии не обнуляется.

Разумеется, что разрядность указанных регистров, и расположение в 0 них информации может быть и несколько иной. Предполагается, что регистры 1-4 построены на основе двухтактных синхронных D-триггеров с асинхронными установочными входами. Ре- 45 гистр 4 частного имеет цепи однотакт- ного сдвига влево на (k-1) разрядов. В блоке 5 деления усеченных чисел формируется k двоичных цифр частного. Формирование k цифр частного в 50 каждом такте работы устройства для деления производится путем умножения в узле 9 значения однорядного кода усеченного остатка, сформированного на выходах 31 младших разрядов вычи- 55 тателя 8, на значение старших разрядов обратной величины усеченного делителя, сформированной на выходах 30 узла 7 вычисления обратной величины. Чтобы устранять возможность

получения в устройстве k цифр частного с избытком значение старших разрядов делителя, хранимого в регистре 3 делителя, увеличивается на единицу младшего разряда в сумматоре 6 принудительного округления делителя, а значение однорядного кода усеченно То остатка, формируемого в вычитателе 8 -по значению старших разрядов двухрядного кода остатка, хранимого в регистрах 1 и 2, уменьшается на единицу младшего разряда в вычитате- ле 8.

Определяется какое число старших разрядов делителя, остатка и обратной величины принудительно округленного усеченного делителя необходимо обрабатывать в блоке 5, чтобы получить на выходах 33 узла 9 значение k цифр частного с точностью до единицы их младшего разряда. Это число; в первую очередь, зависит от диапазона значений делимого X и делителя Y. Пусть делимое X и делитель Y есть нормализованные положительные двоичные дроби, т,е, Г1 и 1/2-ЙГ Г. Разумеется, что это справедливо только на первом такте деления. В дальнейшем же, когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в устройстве может изменяться в пределах 0 X 2Y. Показывается, что при принятых допущениях для получения на выходах 33 k

двоичных цифр частного с точностью

1.

до единицы их младшего разряда достаточно обрабатывать (k+4) старших разрядов остатка X (один разряд слева от запятой и (k+З) разряда справа от запятой), (k+З) старших разрядов делителя Y (все разряды расположены справа от запятой) и (k+2) старших разряда обратной величины принудительного округленного усеченного делителя (один разряд слева от запятой и (k+1)-разряд справа от запятой) .

Действительно, пусть Х( - значение старших (k+4) разрядов приведенного остатка X; Y, - значение стяр- ших (k+З) разрядов делителя Y; С1 - значение старших (k+2) разрядов обратной величины С принудительного округленного усеченного делителя. Тогда () - значение усеченного остатка, полученного приведением к

0

5

0

5

С

5

однорядному коду старших разрядов двухрядного кода остатка и уменьшенное на единицу младшего разряда, где р - величина, на которую отличается значение усеченного остатка, полученного приведением к однорядному коду старших разрядов двухрядного кода остатка и уменьшенное на единицу младшего разряда, от значения старших разрядов остатка,получаемого приведением к однорядному коду всех п разрядов двухрядного кода остатка, С2 С-С,, Х2 Х-Х, Y4 Y-Y, - значение младших разрядов обратной величины, остатка и делителя соответственно. Показывается, что абсолютная погрешность Ј (разность между значением частного, полученным при делении п-разрядных чисел, и значением частного, полученным путем умножения значения старших (k+4) разрядов однорядного кода остатка, полученного при приведении к однорядному коду старших (k+4) разрядов двухрядного кода п-разрядного остатка и уменьшенного на единицу младшего разряда с весом 2 -() па значение старших (k+2) разрядов обратной величины от принудительно-округленных старших (k+З) разрядов делителя), при этом будет заключена в пределах

0 (X, - р)(С - С4).

Выполнение левого условия очевидно, поэтому ограничивается лишь доказательство неравенства

40

Ј JL.-(X, - р)(С -C4)2-ft-tf

5

в С

Максимальная погрешность Ј будет том случае, когда Р РЛ(ХКС. 2 fc 3

С учетом это- f(fc+3)

С 2 маке С

-Ck-n

го, а также того,что С 1/(Y , получается

X

-Г - (X, + 2-(k+3))

Vo/u,

,„-и-)

2

55

+ 2

-(fc + i)

(X, 2-(-,,

Для доказательства этого неравенства достаточно доказать следующую систему неравенств:

Нетрудно видеть, что левая часть в первом неравенстве принимает максимальное значение, когда YZ О,

р Y - Y Y Y 7 -(fc + 3) т.е. I - 1,, л - л1/Цв,

- 2 ; X - Хмв(кс 2Y-2- . С учетом этого первое неравенство можно представить в виде

X(Y, + 2-(k+3)) - Y(X ,- 2-(k+j; )

-ь ,

Ј2 Y(Y , + 2 )

или

(2-(k0 -2V1+ ()2- + 25 + (,(.,+ 2-fk 3 ) Последнее неравенство будет вы, 30

полняться, если справедливо следую щее

,4Y, 2

rU+3)

V . п п 9( Mf k + 3J /

L1

2-VY((Y, + 2(k 3))

или, что

Y,

Второе неравенство, приведенной вы те системы, можно переписать в виде

X, 2 + 2(kf3).

Эти соотношения выполняются при всех значениях делителя Y, заключенного в пределах 1/2 Y 1. Таким образом, при принятых разрядностях,обрабатываемых в блоке 5, деление усеченных чисел операндов, значение k-разрядного частного, получаемого на выходах 33 узла 9 умножения, может быть либо равно значению старших k разрядов частного, получаемому при делении n-разрядных чисел, либо меньше его на единицу младшего разряда с весом 2 .

Все узлы блока 5 комбинационного типа. В сумматоре 6 осуществляется

10

15 с20

+ 25

30

35

вы-40

5 , о

о

принудительное округление делителя Y путем прибавления к значению его старших (k+З) разрядов, поступающих на входы сумматора 6 с выходов 28 регистра 3, единицы в их младший разряд (сигнал логической единицы постоянно подается на вход переноса сумматора 6 с входа 20 устройства). На выходах 29 сумматора 6 образуется (k+4)-разрядный результат (один разряд слева от запятой, остальные - справа от запятой). В узле 7 вычисляются (k+2) старших разряда обратной величины (один разряд слева от запятой, остальные - справа от запятой) принудительно округленного в сумматоре 6 делителя. Этот узел может быть синтезирован по соответствующей таблице истинности либо в виде некоторого логического шифратора, либо на ПЗУ, либо как это описано в известных источниках. В первых двух случаях возможна совместная реализация сумматора 6 и узла 7. С помощью вычитателя 8 осуществляется приведение (k+5) старших разрядов (два разряда слева от запятой, остальные - справа от запятой) двухрядного кода остатка, хранимого в регистрах 1 и 2, к однорядному коду с принудительным уменьшением этого значения на единицу его младшего разряда (для этого на вход заема вычитателя 8 через вход 20 устройства постоянно подается сигнал логической единицы). На выходах 31 вычитателя 8 формируются младшие (k+4) разряда разности (один разряд слева, остальные - справа от запятой), а на его выходе 32 образуется один самый старший разряд этой разности. Отмечается, что на входы вычитателя 8 подаются не (k+4) старших разряда двухрядного кода остатка, как это было показано выше, a (k+5) старших разрядов. Это связано с необходимостью обеспечения правильного функционирования устройства в случае, когда при нуле- 4вом значении старших разрядов остатка за счет принудительного уменьшения этого значения на единицу млад- шего разряда на выходах вычитателя 8 образуется единичный код J 1 1 ... 1.. В узле 9 осуществляется перемножение двух сомножителей: первый сомножитель поступает на входы узла 9 с выходов 30 узла 7 и содержит (k+2) разряда, а второй сомножитель подается

на входы узла 9 с выходов 31 вычи- тателя 8 и содержит (k+4) разряда. На выходы 33 узла 9 поступают только k старших разрядов произведения (один разряд слева от запятой, остальные - справа), которые и являются очередными цифрами частного. Узел 9 может быть разработан хорошо известными методами.

В блоке 10 умножения осуществляется перемножение (k-1) младших разрядов k-разрядного частного, сформированных на выходах 34 узла 9 и поступающих на входы второй группы блока 10, и n-разрядного делителя, хранимого в регистре 3 и поступающего на входы первой группы блока 10 умножения с выходов 27 разрядов регистра 3. На выходах 38 и 39 первой и второй групп блока 10 образуется произведение в двухрядном коде.

Первый вычитатель 11 комбинационного типа построен по принципу запо-

вычитателя 13 присутствует .сигнал логического нуля (разность на выходах 42 положительная). Таким образом, на выходах 43 второго коммутатора 15 формируется остаток такой, какой он получается в процессе деления по методу с восстановлением остатка при определении одной цифры частного.

Коммутатор 15 может быть реализован на элементах 2И-2ИЛИ.

С помощью первого коммутатора 14 осуществляется передача на информационные входы первого регистра 1 ос-

татка либо значения делимого с входа 18 данных устройства, когда на. третьем выходе 48 блока 17 управления присутствует сигнал логической единицы, либо значение разности с

0 выходов 40 первого вычитателя 11, когда на втором выходе 47 блока 17 управления формируется сигнал логической единицы, или же значения,образованного на выходах 43 второго

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

Изобретение относится к вычислительной технике и может быть применено в быстродействующих вычислительных устройствах для выполнения операции деления чисел. Цель изобретения является сокращение количества оборудования устройства. Устройство содержит два регистра 1-2 остатка, регистр 3 делителя, регистр 4 частного, блок 5 деления усеченных чисел, состоящий из сумматора 6 принудительного округления делителя, узла 7 вычисления обратной величины, вычислителя 8 и узла 9 умножения, блок 10 умножения, три вычитателя 11-13, два коммутатора 14-15, узел 16 коррекции частного и блок 17 управления. С помощью нововведенных в блок деления усеченных чисел узла вычисления обратной величины и узла умножения, а также за счет использования соответствующей системы связей обеспечивается положительный эффект, заклфчающийся в сокращении количества оборудования устройства. 1 з.п.ф-лы, 2 ил.

минания заема. Как и в известном уст- 25 коммутатора 15, когда на первом вьгройстве он может быть реализован на основе (п+1)-одноразрядного двоичного вычитателя. В вычитателе 1I осуществляется вычитание из разности, сформированной на выходах 43 второго коммутатора 15, произведения делителя на (k-1) младших разрядов k-разрядного частного. Результат этого вычитания получается на выходах разности 40 и заема 41 вычитателя 11 в д в у хр яд н ом к оде.

Второй 12 и третий 13 вычитатели комбинационного типа с ускоренным распространением заема. С помощью второго вычитателя 12 двухрядный код остатка, хранимый в первом 1 и втором 2 регистрах остатка в виде разности и заема, преобразуется в однорядный код, из которого далее в третьем вычитателе 13 вычитается делитель, хранимый в регистре 3.

С помощью второго коммутатора 15 осуществляется передача на входы уменьшаемого первого вычитателя 11 и на информационные входы третьей группы первого коммутатора 14 либо значения разности с выходов второго вычитателя 12, когда на выходе 45 заема старшего разряда вычитателя 13

ходе 46 блока 17 управления прис ствует сигнал логической единицы Первый коммут.атор 4 может быть лизован на элементах 2И-3 ИЛИ.

30 Узел .16 коррекции частного пр назначен как для коррекции, в сл необходимости, (k-1) младших раз дов частного, образованного в пр дущем такте работы устройства, т

зс и для коррекции k-цифр частного, сформированных в текущем такте выходах 33 узла 9. Коррекция (kмладших разрядов частного,получе го в предыдущем такте, осуществл

40 ется только тогда, когда сигнал ма на выходе 45 старшего разряда третьего вычитателя 13 соответст уровню логического нуля, а корре k-цифр частного, образованных в

45 кущем такте, производится тогда, да сигнал на втором выходе 47 бл 17 управления соответствует уров логического нуля, причем k-цифр стного, сформированных в текущем

50 такте, приводятся в результате к

рекции из вида ОХХХ...X к виду

JOQO.. .0, или из вида tXXX. ..Х

k

присутствует сигнал логической едини- , „. „ „

/ /0 ээ виду 000...О. Последнийслучаи в

цы (разность -на выходах 42 отрицатель- у v..V.. - м

ная), либо значения разности с выхо-.

дов 42 третьего вычитателя 13, когда на выходе 45 заема старшего разряда

боте устройства возможен тогда, да на выходе 32 вычитателя 8 офор

ходе 46 блока 17 управления присутствует сигнал логической единицы. Первый коммут.атор 4 может быть реализован на элементах 2И-3 ИЛИ.

Узел .16 коррекции частного предназначен как для коррекции, в случае необходимости, (k-1) младших разрядов частного, образованного в предыдущем такте работы устройства, так

и для коррекции k-цифр частного, сформированных в текущем такте на выходах 33 узла 9. Коррекция (k1) младших разрядов частного,полученного в предыдущем такте, осуществляется только тогда, когда сигнал заема на выходе 45 старшего разряда третьего вычитателя 13 соответствует уровню логического нуля, а коррекция k-цифр частного, образованных в текущем такте, производится тогда,ког- да сигнал на втором выходе 47 блока 17 управления соответствует уровню логического нуля, причем k-цифр частного, сформированных в текущем

такте, приводятся в результате корработе устройства возможен тогда, когда на выходе 32 вычитателя 8 оформировался сигнал логической единицы. Как в известном устройстве узел 16 частного может быть построен с использованием k-разрядного двоичного сумматора, k элементов И и элемента НЕ.

Блок 17 управления координирует работу всех узлов, и блоков устройства при выполнении, на нем операции делений чисел.о

Устройство для деления чисел работает следующим образом.

Пусть в исходном состоянии на входе 18 данных устройства присутствует n-разрядный двоичный код делителя без знака. Тогда по первому импульсу на входе 19 синхронизации устройства на четвертом 49 и пятом 50 выходах блока 17 управления (фиг.2) формируются управляющие импульсы, по которым осуществляется запись n-разрядного кода делителя в регистр 3 с входа 18 данных устройства и обнуление регистров 1 и 2 остатка. По истечении действия первого импульса на входе 19 синхронизации устройства появляется потенциал логической единицы на третьем выходе 48 блока 17 управления, так как по первому синхроимпульсу его счетчик 52 переключился из состояния О в состояние 1. Под действием этого управляющего потенциала первый коммутатор 14 пропускает на информационные входы регистра 1 значение п-раз- рядного кода делимого с входа 18 данных устройства (предполагается, что код делимого поступает на вход I8 сразу же после записи кода делителя в регистр 3). Далее, так как в регистрах 1 и 2 остатка хранятся нулевые коды, то на выходе 32 старшего раз-« ряда вычитателя 8 блока 5 формируется потенциал логической единицы,который, поступая в блок 17 управления через его элементы НЕ И 59 устанавливает на втором выходе 47 блока 17 потенциал логического нуля, а через элемент ИЛИ 61 подготавливает к срабатыванию по синхроимпульсу элемент И 58. Под действием потенциала логического нуля на выходе 47 блока 17 управления на выходах (k-1) младших разрядов выхода 37 узла 16 коррекции частного формируется нулевой код. С приходом второго импульса на вход 19 синхронизации устройства осуществляется запись п-разрядного

5

0

5

0

5

0

45

50

кода делимого в регистр 1 (делимое записывается в п младших разрядов регистра 1 с одновременной записью в два его старших разряда нулей), обнуление регистра 2 (так как по второму синхроимпульсу на четвертом выходе 49 блока 17 сформирован управляющий импульс) и запись в (k-1) младших разрядов регистра 4 нулевого кода (в старшие разряды регистра 4 одновременно записывается некоторая произвольная информация), а также ч переключение счетчика 52 блока 17 в состояние 2. По истечении второго импульса на входе 19 синхронизации устройства подготовительный этап, включающий два такта, заканчивается и далее выполняется собственно деление, в процессе которого за m тактов формируется Сш(k-1)+lJ двоичных цифр частного.

Рассматривается более детально работа устройства в течение одного 1-го такта собственно деления (i ). По значению старших разрядов текущего остатка, хранимого в регистрах 1 и 2 в двухрядном коде, и по значению старших разрядов делителя, хранимого в регистре 3 делителя, на выходах 33 узла 9 умножения блока 5 деления усеченных чисел формируется k очередных двоичных цифр частного с точностью до единицы их младшего разряда (это значение является либо точным, либо меньше истинного на величину ).Сформированные на выходах 34 (k-1) младших разрядов k-разрядного частного (их значение обозначается через fc-1

) поступают 16 коррекчастного и одновременно на входы второй группы блока 10 умножения, на выходах 38 и 39 которого образуется в двухрядном коде произведение

Y Z j .На выходах 43 второго коммутатора 15 образуется разность R . R Ui у - 2(. (R,-., - значение текущего остатка в однорядном коде на выходах второго вычитателя 12; - значение старшего разряда

Z i

ции

Zl«

k-разрядного частного, которое определяется по знаку разности R 55 R j сформированной на выходах 42 третьего вычитателя 13). Если сигнал на выходе 45 заема старшего разряда третьего вычитателя 13 равен логической единице, то Z 0, в

противном случае 40 и 41 первого

Zu 1 . На выходах вычитателя 11 формируется в двухрядном коде разность

R - R Y 7( R V „ К л , - I 6 ; - п - I к

X

.

Rf-, - Zj - Y.

Если разность R ,- R ,-,- Y, сформированная на выходах 42 третьего вычитателя 13, положительная (т.е. старший разряд k-разрядного частного Z ( равен единице), а старший разряд k-разрядного частного, сформированного в блоке 5 деления усеченных чисел, равен нулю (этот разряд с выхода 35 узла 9 поступает в блок 17 управления), то в i-m такте на втором выходе 47 блока I7 управления формируется потенциал логического нуля, по которому, а также по сигналу на выходе 45 вычитателя 13, в блоке 16 коррекции частного окончательно формируется k-разрядное частное в виде 100...О, а в качестве очередного осК

татка первым коммутатором 14 с разрешения потенциала логической единицы на первом выходе 46 блока 17 уп- равления выбирается разность R . .Значение этой разности записывается в первый регистр 1 остатка со сдвигом на (к-1 ) разрядов влево, а второй регистр 2 остатка при этом обнуляется (на четвертом выходе 49 блока 17 управления в этом случае присутствует потенциал логической единицы).Во всех других случаях в качестве очередного остатка выбирается разность

т,

RJ, значение которой в виде двух чисел (разности и заема) записывается соответствующим образом со сдвигом влево на (k-1) разрядов в первый и второй регистры 1 и 2 остатка.При этом в узле 16 образуется k-разрядное частное такое же, какое оно сформировано на выходах 33 блока 5 (коррекция частного не производится). Аналогичным образом устройство работает и в других тактах.

Как особый случай рассматривается ситуация, когда на выходе 32 старшего разряда вычитателя 8 формируется сигнал логической единицы. В этом случае и на выходе 45 третьего вычитателя 13 обязательно сформируется сигнал логической единицы. Под действием этих единичных сигналов, которые поступают в узел 16 и блок 17 управ

ления, в регистр 1 запишется со сдвигом влево на (k-1) разрядов разность, сформированная на выходах второго вычитателя 12, регистр 2 установится в нулевое состояние, а в узле 16 коррекции частного будет сформирован нулевой код очередного k-раярядного частного.

Формула изобретения

регистры делителя и частного, блок деления усеченных чисел, содержащий сумматор принудительного округления делителя и вычитатеЛь, блок умножения, три вычитателя, два коммутатора, узел коррекции частного и блок управления, причем вход данных устройства соединен с информационным входом регистра делителя и с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом разности первого вычитателя, вход уменьшаемого которого соединен с выходом второго коммутатора и с третьим информационным входом первого коммутатора, выход которого соединен с информационным входом первого регистра остатка, выход которого соединен с входом умньшаемого второго вычитателя, вход вычитаемого которого соединен с выходом второго регистра остатка, информационный вход которого соединен с выходом заема первого вычитателя, входы вычитаемого и заема которого соединены с первым и вторым выходами произведения блока умножения, первый информационный вход которого соединен с выходом регистра делителя и входом вычитаемого третьего вычитателя, вход уменьшаемого которого соединен с выходом второго вычитателя, первым информационным входом второго коммутатора и выходом остатка устройства, второй информационный вход второго коммутатора соединен с выходом разности третьего вычитателя, выход заема которого соединен с управляющим входом второго коммутатора и первыми управляющими

входами узла коррекции и блока управления, вход синхронизации которого соединен с входом синхронизации устройства и входами синхронизации первого и второго регистров остатка и

регистра частного, выход младших разрядов которого соединен с первым информационным входом узла коррекции частного, выход младших разрядов которого соединен с информационным входом регистра частного, выход которого соединен с выходом частного устройства, выход старших разрядов регистра делителя соединен с входом сумматора принудительного округления, вход переноса которого соединен с входом заема вычитателя блока деления усеченных чисел и входом логической единицы устройства, входы уменьшаемого и вычитаемого вычитателя блока деления усеченных чисел соединены с выходами старших разрядов первого и второго регистров остатка соответственно, первой, второй и третий выходы блока управления соединены соответственно с первым, вторым и третьим управляющими входами первого коммутатора, четвертый выход блока управления соединен с входом установки в 0м второгр регистра остатка, пятый выход б лока управ л i мя соединен с синхровходом регистра делителя и

О

с входом установки в

первого ревходом узла вычисления обратной величины, выходы старшего разряда узла умножения и заема вычитателя блока деления усеченных чисел соединены с вторым и третьим управляющими входами блока управления соответственно, второй управляющий вход узла коррекции соединен с вторым управляющим

л входом первого коммутатора,

15 Два элемента ИЛИ, причем выход счетчика соединен с входом дешифратора, первый выход которого соединен с первыми входами первых элементов И и ИЛИ, второй выход дешифратора соеди20 нен с инверсным входом второго элемента И и третьим выходом блока,третий выход дешифратора соединен с первым входом третьего элемента И,второй вход которого соединен с входом синх25 ронизации блока, с выходом синхронизации счетчика, первым входом четвертого элемента И и вторым входом первого элемента И, выход которого соединен с пятым выходом блока, первый

гистра остатка, второй информационньй 30 и второй управляющие входы блока соевход блока умножения соединен с вторым информационным входом узла коррекции частного, шестой выход блока управления соединен с выходом сигнализации окончания деления, отличаю щ е е с я тем, что, с целью сокращения количества оборудования, блок Деления усеченных чисел содержит узел вычисления обратной величины и узел умножения, первый и второй ин- формационные входы которого соединены с выходами узла вычисления -обратной величины и выходом разности вычита- . теля блока деления усеченных чисел соответственно, выходы разрядов,кроме старшего, узла умножения соединены с вторым информационным входом блока умножения, выход сумматора принудительного округления соединен с

входом узла вычисления обратной величины, выходы старшего разряда узла умножения и заема вычитателя блока деления усеченных чисел соединены с вторым и третьим управляющими входами блока управления соответственно, второй управляющий вход узла коррекции соединен с вторым управляющим

входом первого коммутатора,

5 Два элемента ИЛИ, причем выход счетчика соединен с входом дешифратора, первый выход которого соединен с первыми входами первых элементов И и ИЛИ, второй выход дешифратора соеди0 нен с инверсным входом второго элемента И и третьим выходом блока,третий выход дешифратора соединен с первым входом третьего элемента И,второй вход которого соединен с входом синх5 ронизации блока, с выходом синхронизации счетчика, первым входом четвертого элемента И и вторым входом первого элемента И, выход которого соединен с пятым выходом блока, первый

динены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого . соединен с третьим управляющим, входом блока, прямой выход пятого элемента И соединен с вторым выходом блока, инверсный выход пятого элемента И сое0 динен с вторыми входами второго элемента И, первого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с чётвер5 тым выходом блока, выход второго элемента И соединен с первым выходом блока, выход третьего элемента И соединен с входом установки в О счетчика и шестым выходом блока.

Фиг2

Л

| Патент США № 3234367, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-12-21—Подача