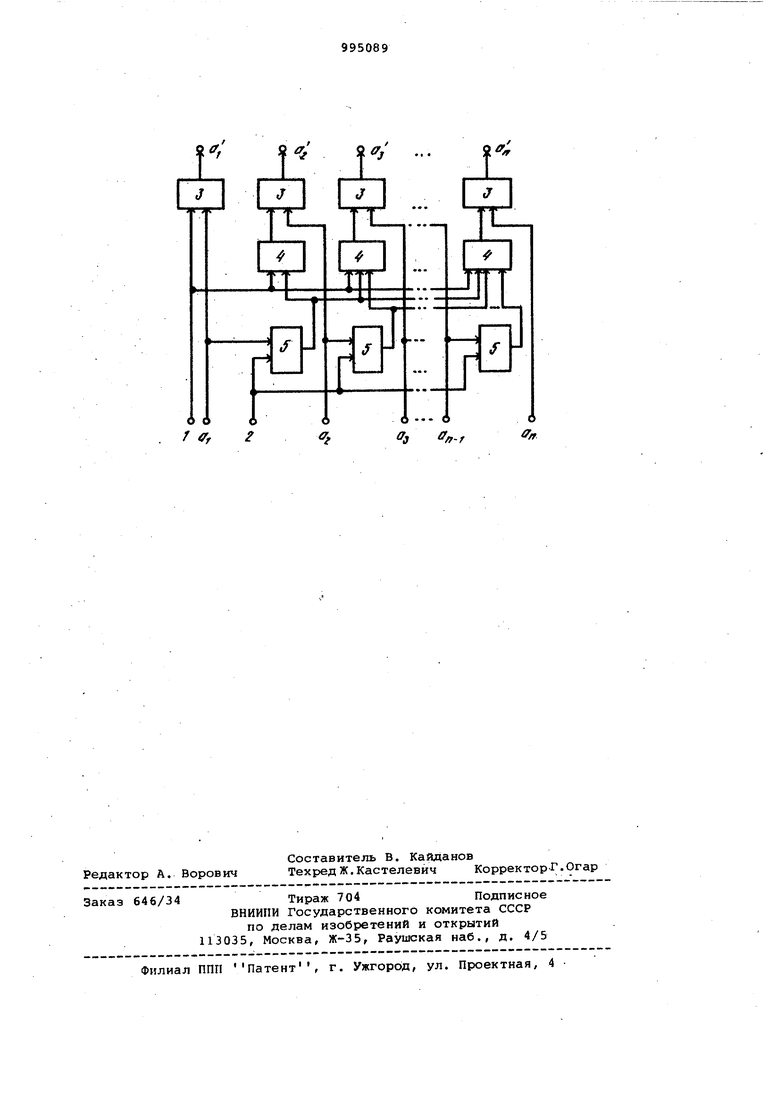

квдем входе требуется прибавлять или вычитать единицу либо передавать вхо ной код без изменения. Цель изобретения - расширение об ласти применения за счет возможности вьшода входного кода без изменения и уменьшения значения входного кода на единицу, а также повышение быстродей ствия. Г Поставленная цель достигается тем что устройство для изменения п-раз-. рядного двоичного числа на единицу, содержащее (п-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход каждого i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ ( 2,..., п-1) подключен к (1+1)-му вход ному разряду двоичного п-разрядного числа, выход каждого i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к (itl)-My выходному разряду двоичного п-разряд ного числа, устройство также содержит п дополнительныхэлементов ИСКЛЮ ЧАЩЕЕ ИЛИ и (п-1) элементов И, причем первый вход первого дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подклю чен к- первому входному разряду двоич ного п-разрядного числа, второй вход первого дополнительного элемента ИС КЛЮЧАЮЩЕЕ ИЛИ подключен К управляющему входу задания режима работьа устро ства и к первым управляющим входам элементов И, выход первого дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первому выходному разряду двоичного п-разрядного числа, первые входы J-X дополнительных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ ( j i+l) подклю чены к второму управляющему входу задания режима работы устройства, вто-рой вход J-го дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к i-му входному разряду двоичного п-ра рядного числа соответственно, выход J -го дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к i-м информационным входам Мц элементов И (К i, i+l,...,n-l, MK n-i) , -ВЫХОД i-ro элемента И подключен к второму входу i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Сущность изобретения заключается в том, что эа счет введения в известный блок изменения двоичного кода п-го элемента 2 ИСКЛЮЧАЮЩЕЕ-ИЛИ, п-1 элементов И и п-1 дополнительных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ при-нулевом потенциале на управляющем входе осуществляется передача входного кода на выходы блока без изменения, а при единичном потенциале на управляющем входе в зависимости от потенциала на входе переключения реверса блока осуществляется либо прибавление, единицы к входному числу за счет инвертирования значений кода в младших разрядах до того разряда включительно, в Котором впервые встречается ло гический ноль, либо вычитание единицы от входного числа за счет инвертирования значений кода в младших разрядах до того разряда включительно, в котором впервые встречается логическая единица. При этом максимальная задержка прохождения сигналов во всех разрядах одинакова и равна времени прохождения сигнала через два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и через один элемент И. На чертеже представлена принципиальная схема устройства для изменения п-разрядного двоичного числа на единицу. Устройство содержит управляющий шход 1, вход 2 переключения реверса, п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, п-1 элементов И 4, п-1 дополнительных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Первые входы каждого j( j i+1) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и каждого 1 (i 1-n-l) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 соединены с j разрядом dj входного числа; второй вход первого элемента ИСКЛЮЧАЮ- . ЩЕЕ ИЛИ 3 соединен с первыми входами 1 п-1 элементов И 4 и подключен к управляющему входу 1, а вход 2 переключения реверса соединен с вторыми входами 1 п-1 дополнительных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Выход каждого дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 соединен с i+1 входами i-n-1 элементов И 4, выход каждого i элемента И 4 соединен с вторым входом К (К i+1) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, а выход каждого j элемента ИСКЛЮЧАЩЕЕ ИЛИ 3 является выходом j разряда выходного числа. Устройство работает следующим образом. На входы устройства поступает число, заданное п-разрядным двоичнУМ КО дом d , aj,..., ctp. При наличии нуле- вого потенциала, на управляющем входе. 1 на первых входах, а следовательно, и на выходах элементов И 4 имеет месгто нулевой потенциал, поэтому входной код а , q ,..., «f, передается через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3 на выход блока без изменения. При наличии единичного потенциала на управляющем входе 1 в зависимости от потенциала на входе 2 переключение реверса осуществляется изменением входного числа на единицу. Если на входе 2 имеет место нулевой потенциал, то потенциал на выходе каждого i дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 соответствует погтенциалу на j входе устройства. При этом, если младший разряд « входного числа является нулевым, то на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 формируется сигнал о(-а, а на выходах остальных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 формируются сигналы с«. ..OJ ... .«п соответствующие входному коду 0(2 ... с(.... Of г, . Если младший разряд р-, входного числа является единичным, то элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3 осуществляют инвертирование входных сигналов от первого рауряда «1 до того разряда включительно, в котором впервые встречается логический ноль. Остальные разряды входг ного кода подаются на выход без изменения. Это эквивалентно прибавлению к входному числу логической единицы.

Если на входе 2 имеет место единич ный потенциал, то сигнал на вькоде каждого i элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 соответствует инвертированному сигнаглу на j входе а блока. При этом/ если младший разряд « входного числа является единичным, то на выходе первого элемента ИСКЛЮЧАКВДЕЕ ИЛИ 3 формируется сигнал al, 6i , а на выходах остальных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 формируются сигналы aj... dj ... df,/ соответствующие входному коду q . .. Oj- . . . «f, . Если младший разряд входного числа является нулевым, то элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3 осуществляют инвертирование входных сигналов от первого разряда до того разряда включительно, в котором впервые встречается логическая единица. Остальные разряды входного кода передаются на выход без изменения. Это эквивалентно вычитанию от входного числа Эу , ,... an логической единицы.

Таким образом, введение в известный блок изменения двоичного п-разрядного числа на единицу п-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, а также п-1 элементов И 4 и п-1 дополнительных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5 позволяет производить -прибавление или вычитание единицы от входного числа,, заданного двоичным кодом, или передавать входное число без изменения и тем самым расширить область примене-ния известного устрюйства, а такдее сократить время обработки информации Формула изобретения

Устройство для изменения п-разрядяого двоичного числа на единицу, содержащее (п-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход каждого i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (i 1,2.,,, п-1) подключен к (1+1)-му входному разряду двоичного п-разрядного числа, выход каждого i-ro- элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к (i+1)-му выходному разряду двоичного п-разрядного числа, о т лич а юще е с.я тем, что, с целью расширения области его применения за счет обеспечения возможности вывода входного кода без изменения и уменьшения значения входного кода на единицу, а также повышения его быстродействия, устройство содержит п дополнительных элементов ИСКЛЮЧАКНЦЕЕ ИЛИ И (п-1) элементов И, причем первый вход первого дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первому входному разряду двоичного п-разрядного числа, второй вход первого дополнительного элемента ИСКЛЮЧАЩЕЕ ИЛИ подключен к управляющему входу задания режима работы устройства и к первым управляющим входам элементов И, выход -первого дополнительного элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ подключен к первому выходному разряду двоичного п-разрядного числа, первые входы J-X дополнительных элементов ИСКЛЮЧАЮЩЕЕ или (у i+i) подключены к второму управляющему входу задания режима работы устройства, второй вход j-ro дополнительного элемента ИСКЛЮЧАЩЕЕ ИЛИ подключен к i-му входному разряду двоичного п-разрядносо числа, соответственно, выход дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к i-м информационнБМ входам ti элементов И (.К i, i+1, ..., n-1 М ti n-i) , выход i-ro элемента И подключен к второму входу 1--го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 800991, кл. G Об F 7/50, 1979,

2.Патент Японии № 53-7349,

кл. G 06 Р 7/385, опублик. 1978 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для подключения абонентов к общей магистрали | 1983 |

|

SU1109754A1 |

| Устройство для изменения @ -разрядного двоичного числа на единицу | 1987 |

|

SU1418702A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Устройство для деления | 1989 |

|

SU1667077A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Генератор систем базисных функций Аристова | 1988 |

|

SU1599850A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Устройство для определения экстремальных чисел | 1983 |

|

SU1239709A1 |

| Устройство для определения старшего значащего разряда | 1983 |

|

SU1164707A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

Авторы

Даты

1983-02-07—Публикация

1981-08-17—Подача