Изобретение относится к цифровой вычислительной технике и может быть использовано как узловой элемент цифровой сетки при разработке специализированных процессоров для решения краевых задач математической физики.

Целью изобретения является повьппе- ние быстродействия устройства.

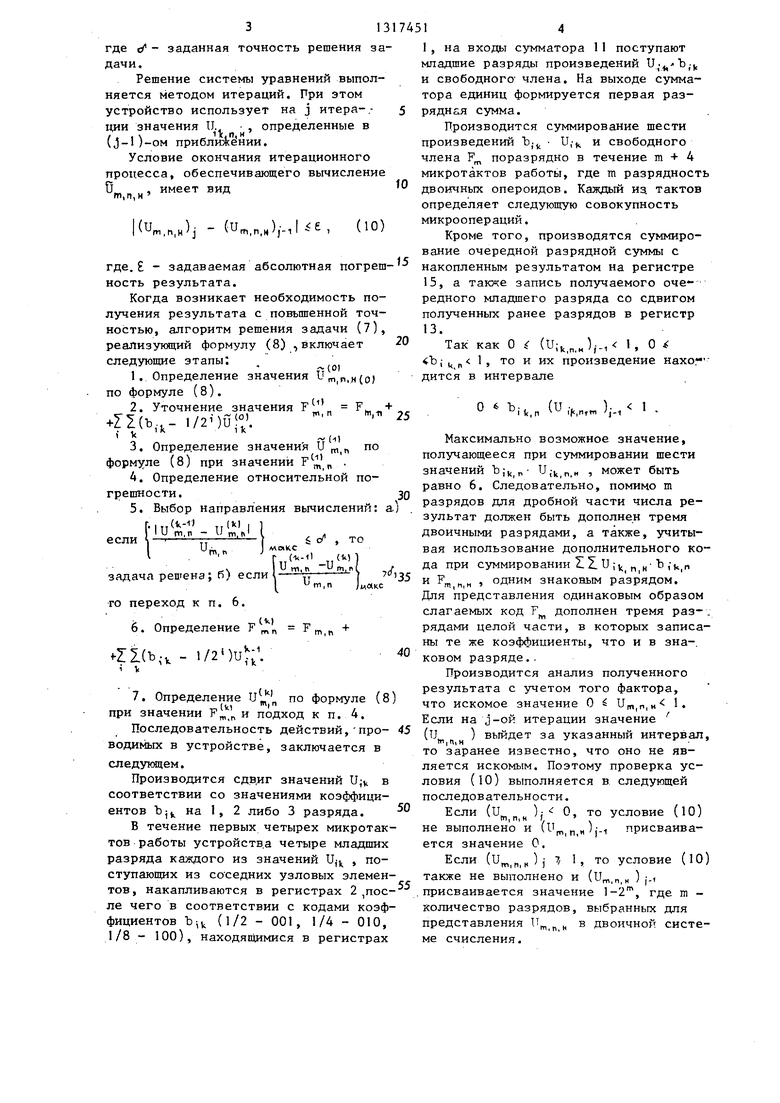

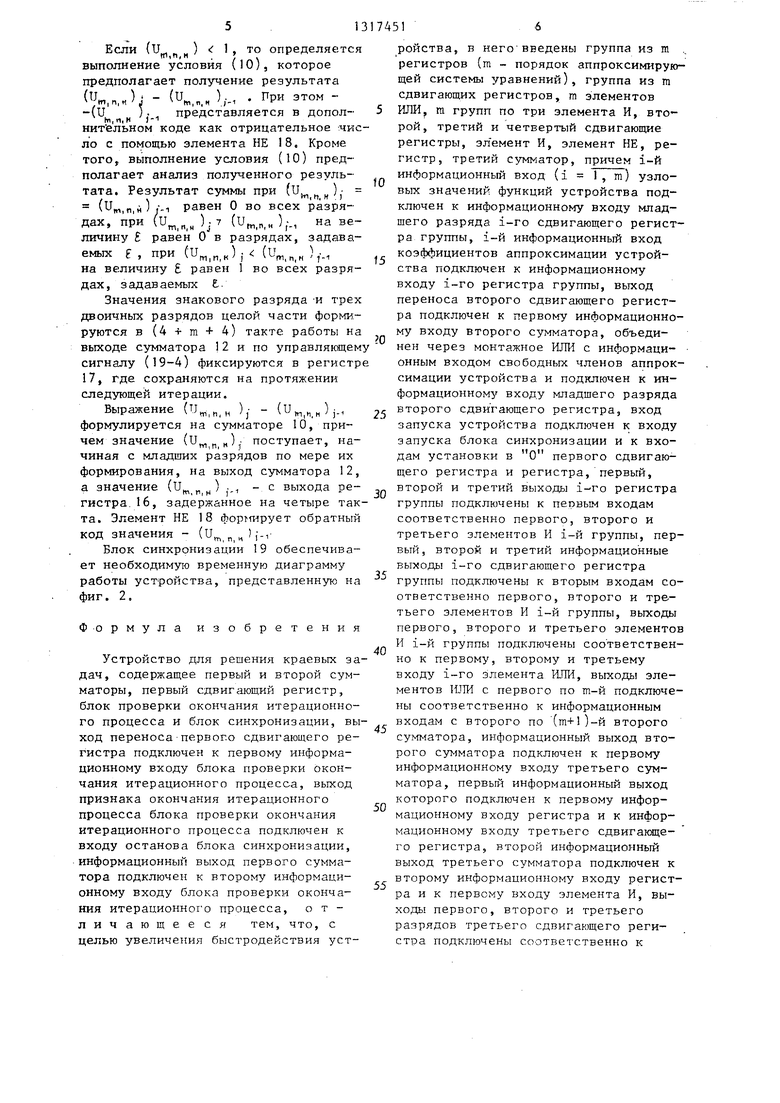

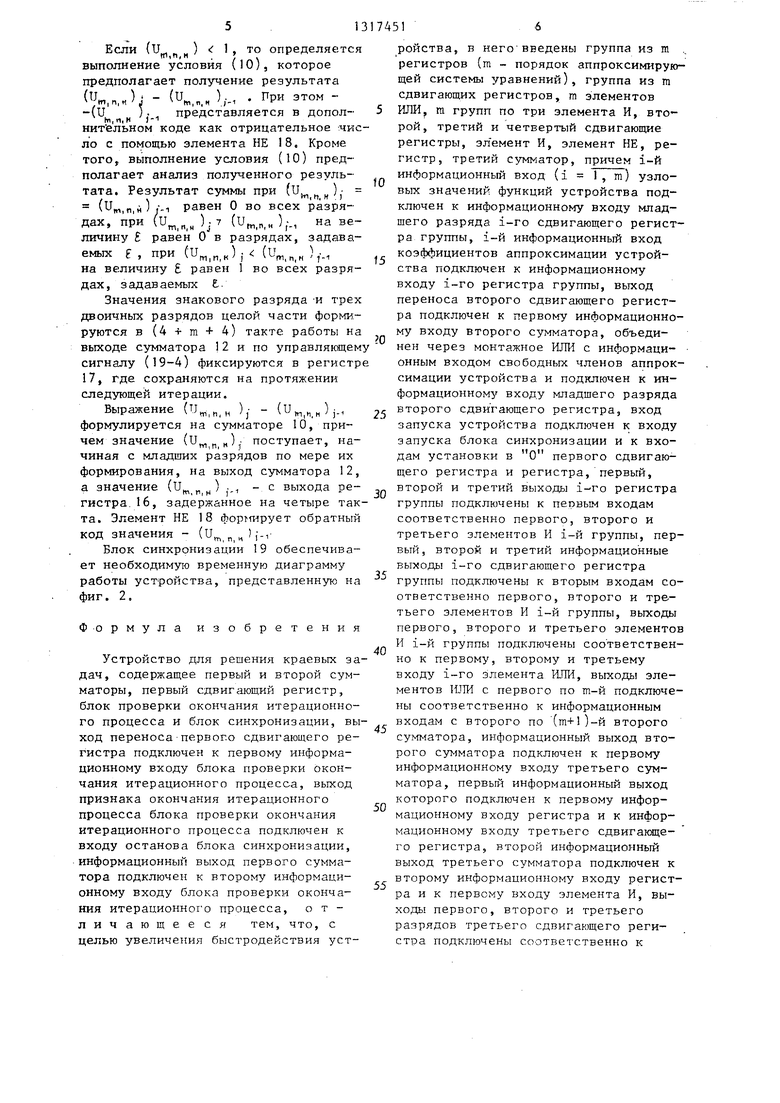

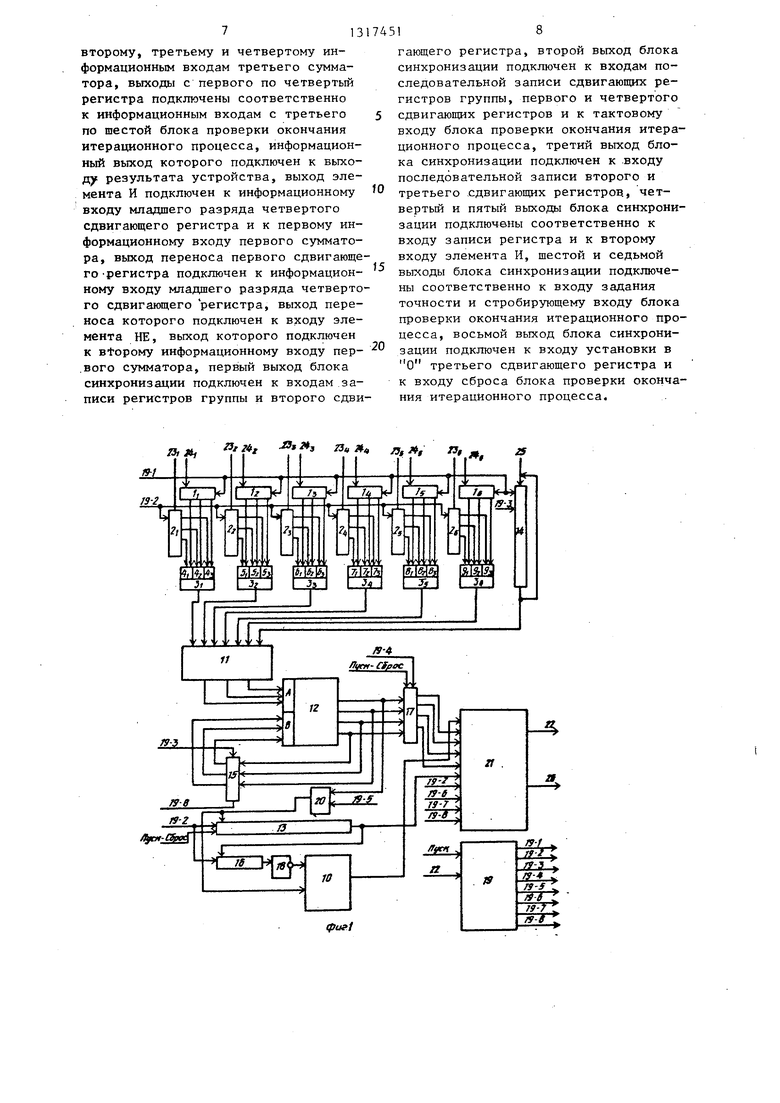

На фиг. 1 схематически показано устройство; на фиг. 2 - временная диаграмма его работы.

Устройство содержит группу регистров , группу сдвигающих регистров , с первого по шестой элементы ИЛИ , первую группу элементов И 4, 4, 4 , вторую группу элементов И 5, 5 , fL , третью группу элементов И 6, 6, 6, четвертую группу элементов И 7 , 7, 7 , пятую группу элементов И 8,,, 8, 8,, шестую группу элементов И 9 , 9, , 9 , с первого .по третий сумматоры 10-12,с первого по четвертый сдвигаюпще регистры 13-16, регистр 17, элемент НЕ 18, блок 19 синхронизации, с первого по восьмой выходы блока синхронизации, элемент И 20, блок 21 проверки окончания итерационного процесса, выход 22 признака окончания итерационного процесса устройства, входы 23 узловых значений функций, входы 24 коэффициентов аппроксимации, вход 25 свободного члена аппроксимации, выход 26 устройства. . ,

Устройство предназначено для решения краевых задач вида

Л.. Т Vx,

d T

.) () rfx fx

о

t/T

ЗсГх

-) +ш (х , X, , X, , Г)

с/Т

(1)

Т );

Лф -, s jiK J

(3)

0(S,C) Тс(5, Г) -. T,(S,

Ь 1

r INjJ

(4)

( -(мжЧ;

т f(x,, X , X ) при (,4. (6)

to

Для решения уравнения (|) - (6) преобразуются к системе уравнений

вида

JniVAKkV,

i:b.,u,.-f р,)

где i 1, 2, 3; k 1, 2;j n - момент времени, для котор ого

производится расчет U „. Индекс m указывает на масштабное представление индексированных переменных, которые всегда сводятся к следующим численным интервалам:

О и,

О - и,-к,п,

-I Fm,n,

О . Ъ, 1

и заведомо представлены в дополнительном коде,,

Устройство- обеспечивает решение одного уравнения системы, для чего использует и известные значения ко- э(| фициентов Ъ- - 1/2, 1/4 либо 1/8

и свободного члена F , а также значения искомой функции U , полу- чаемые в соседних узловьгх элементах. Приближенное значение и „„ определяется по формуле

и

in, n, н

Z Z 1/2 -U;, „. + „. (8)

il;, n.H

т,П|Н

Максимально возможная относитель-- ная погрешность, обусловленная заменой формулы (7) на формулу (8) определяется

О

0,5

(9)

мякс

где t/ - заданная точность решения задачи .

Решение системы уравнений выполняется методом итераций. При этом устройство использует на j итера-.- 1;ии значения U. , определенные в ()OM прибли:}(ёнии.

Условие окончания итерационного процесса, обеспечивающего вычисление 0„ .., имеет вид

т,п,н

|(U,.,H)J - (u,,,,),.,

fo

1, на входы сумматора 11 поступают младшие разряды произведений ,. и свободного члена. На выходе сумматора единиц формируется первая разрядная сумма.

Производится суммирование шести произведений Ъ; U; и свободного члена F поразрядно в течение m + 4 микротактов работы, где m разрядность двоичных опероидов. Каждый иа тактов определяет следующую совокупность микроопераций.

Кроме того, производятся суммирование очередной разрядной суммы с

где. - задаваемая абсолютная погрет- накопленным результатом на регистре кость результата.

Когда возникает необходимость получения результата с повьшгенной точностью, алгоритм решения задачи (7), реализующий формулу (8) ,включает следующие этапы;

(10)

20

15, а также запись получаемого очередного младшего разряда со сдвигом полученных ранее разрядов в регистр 13.

Так как О (U;,,);-, , О

;(01

1 . Определение значения V ,(о} по формуле (8).

Ъ; ц „ 1 , то и их произведение нахог дится в интервале

2. Уточнение значения F. + 11(Ъ,,- 1/21)0;° . - .- 25

1 V IX

: (11

ПО

3.Определение значения U ,,, формуле (8) при значении F. .

4.Определение относительной погрешности.30

5.Выбор направления вычислений: а)

.( ,, ., .

с/

если

I ТТ I

I и |п,п - ц т,г

и

ГЛ, п

ТО

задача решена; б) если го переход к п. 6.

МПКС

г (к-11 W

и 1-п. h и

т. п

и

т.п

( 7/,

макс

О 4 Ъ;, (и ,,„,„),.., 1 .

Максимально возможное значение, получающееся при суммировании шести значений U,- , может быть равно 6. Следовательно, помимо m разрядов для дробной части числа результат должен быть дополнен тремя двоичными разрядами, а также, учитывая использование дополнительного кода при суммировании ZZ. и,- .n 5 и F , одним знаковым разрядом.

Для представления одинаковым образом слагаемых код F дополнен тремя раз-. рядами целой части, в которых записаны те же коэффициенты, что и в зна-. ковом разряде.

6. Определение F „„ F

т,и

У.-1

11(ъ., - 1/2)

7. Определение по формуле (8) при значении и подход к п. 4.

Последовательность действий, про- 45 водимых в устройстве, заключается в следзпедем.

Производится сдв.иг значений Uj в соответствии со значениями коэффици50

ентов Ъ на 1, 2 либо 3 разряда.

В течение первых четырех микротактов работы устройств.а четыре младших разряда каждого из значений Uj , поступающих из со седних узловых элементов, накапливаются в регистрах 2 ,после чего в соответствии с кодами коэффициентов bit (1/2-001, 1/4 - 010, 1/8 - 100), находящимися в регистрах

fo

(10)

накопленным результатом на регистре

15, а также запись получаемого очередного младшего разряда со сдвигом полученных ранее разрядов в регистр 13.

Так как О (U;,,);-, , О

Ъ; ц „ 1 , то и их произведение нахог дится в интервале

25

30

)

/,

О 4 Ъ;, (и ,,„,„),.., 1 .

Максимально возможное значение, получающееся при суммировании шести значений U,- , может быть равно 6. Следовательно, помимо m разрядов для дробной части числа результат должен быть дополнен тремя двоичными разрядами, а также, учитывая использование дополнительного кода при суммировании ZZ. и,- .n 5 и F , одним знаковым разрядом.

0

5

0

Для представления одинаковым образом слагаемых код F дополнен тремя раз-. рядами целой части, в которых записаны те же коэффициенты, что и в зна-. ковом разряде.Производится анализ полученного результата с учетом того фактора, что искомое значение О ,„ 1. Если на j-ой итерации значение (и ) выйдет за указанный интервал,

W I t, Н

то заранее известно, что оно не является искомым. Поэтому проверка условия (Ю) выполняется в следующей последовательности.

(,;

не выполнено и (U

О, то условие (Ю)

ГП| п,и I

)и

лрисваива5

ется значение 0.

Если (U)j 7, 1, то условие (Ю) также не выполнено и (и„,п,„ ) j,, присваивается значение 1-2, где m - количество разрядов, выбранных для представления . двоичной системе счисления.

Если ( „) 1, то определяется выполнение условия (0), которое предполагает получение результата

этом - в допол- (и,,,,„ ).., . При представляется

(Ут,.,«).

-(.,и и нит ельном коде как отрицательное число с помощью элемента НЕ 18. Кроме того, выполнение условия (Ю) предполагает анализ полученного результата. Результат суммы при ( - (U|n,n, ) .-,1 равен О во всех разрядах, при ( )j7 (,„)-., на величину равен О в разрядах, емых f , при ( j ( )у., на величину равен 1 во всех разрядах, задаваемых -.

Значения знакового разряда -и трех двоичных разрядов целой части формируются в (4 4- m + 4) такте работы на выходе сумматора 12 и по управляющем сигналу (19-4) фиксируются в регистр 17, где сохраняются на протяжении следующей итерации.

Выражение (и„,,,, ) - (и.и.мЬ- формулируется на сумматоре 10, причем значение

(и

tn,n, н

поступает.

на- их

чиная с младших разрядов по мере формирования, на выход сумматора 12, а значение (U,) .,, - с выхода регистра. 16, задержанное на четыре такта. Элемент НЕ 18 фор шрует обратный код значения - (),--т

Блок синхронизации 19 обеспечивает необходимую временную диаграмму работы устройства, представленную на фиг. 2,

Ф Ормула изобретения

Устройство для решения краевых задач, содержащее первый и второй сумматоры, первый сдвигающий регистр, блок проверки окончания итерационного процесса и блок синхронизации, выход переноса-первого сдвигающего регистра подключе к первому информационному входу блока проверки окончания итерационного процесса, выход признака окончания итерационного процесса блока проверки окончания итерационного процесса подключен к входу останова блока синхронизации, информационный выход первого сумматора подключен к второму информационному входу блока проверки окончания итерационного процесса, отличающееся тем, что, с целью увеличения быстродействия уст

ройства, в него введены группа из m . регистров (т - порядок аппроксимирующей системы уравнений), группа из га сдвигающих регистров, m элементов ИЛИ, га групп по три элемента И, второй, третий и четвертый сдвигающие регистры, эл емент И, элемент НЕ, регистр, третий сумматор, причем i-й информационный вход (i 1, m) узловых значений функций устройства подключен к информационному входу млад- щего разряда i-го сдвигающего регистра группы, i-й информационный вход коэффициентов аппроксимации устройства подключен к информационному входу 1-го р€ гистра группы, выход переноса второго сдвигающего регистра подключен к первому информационному входу второго сумматора, объединен через монтажное ИЛИ с информаци- онным входом свободных членов аппроксимации устройства и подключен к информационному входу младшего разряда второго сдвигающего регистра, вход запуска устройства подключен к входу запуска блока синхронизации и к входам установки в О первого сдвигающего регистра и регистра, первый, второй и третий выходы i-ro регистра группы подключены к первым входам соответственно первого, второго и третьего элементов И i-й группы, первый, второй и третий информационные выходы i-ro сдвигающего регистра группы подключены к вторым входам соответственно первого, второго и третьего элементов И i-й группы, выходы первого, второго и третьего элементов И i-й группы подключены соответственно к первому, второму и третьему входу элемента ИЛИ, выходы элементов ИЛИ с первого по т-й подключены соответственно к информационным входам с второго по (т+)-й второго сумматора, информационный выход второго сумматора подключен к первому информационному входу третьего сумматора, первьм информационный выход которого подключен к первому информационному входу регистра и к информационному входу третьего сдвигающего регистра, второй информационный выход третьего сумматора подключен к второму информационному входу регистра и к первому входу элемента И, выходы первого, второго и третьего разрядов третьего сдвигающего регистра подключены соответственно к

второму, третьему и четвертому информационным входам третьего сумматора, выходы с первого по четвертый регистра подключены соответственно к информационным входам с третьего по шестой блока проверки окончания итерационного процесса, информационный выход которого подключен к выходу результата устройства, выход элемента И подключен к информационному входу младшего разряда четвертого сдвигающего регистра и к первому информационному входу первого сумматора, выход переноса первого сдвигающе го регистра подключен к информационному входу младшего разряда четверто го сдвигающего регистра, выход переноса которого подключен к входу элемента НЕ, выход которого подключен к BtopoMy информационному входу пер- .вого сумматора, первый выход блока синхронизации подключен к входам записи регистров группы и второго сдви

гающего регистра, второй выход блока синхронизации подключен к входам последовательной записи сдвигающих регистров группы, первого и четвертого 5 сдвигающих регистров и к тактовому входу блока проверки окончания итерационного процесса, третий выход блока синхронизации подключен к -входу последовательной записи второго и третьего .сдвигающих регистров, четвертый и пятый выходы блока синхронизации подключены соответственно к входу записи регистра и к второму входу элемента И, шестой и седьмой выходы блока синхронизации подключены соответственно к входу задания точности и стробирующему входу блока проверки окончания итерационного процесса, восьмой выход блока синхронизации подключен к входу установки в О третьего сдвигающего регистра и к входу сброса блока проверки окончания итерационного процесса.

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1367021A1 |

| Модуль одномерной вычислительной системы для решения нелинейных уравнений теплопроводности | 1986 |

|

SU1368888A1 |

| Устройство для решения дифференциальных уравнений по неявной схеме переменных направлений | 1985 |

|

SU1290347A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1174923A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Цифровой генератор функций | 1981 |

|

SU1035594A1 |

Изобретение относится к цифровой вьтчислительной технике и может быть использовано как узловой элемент цифровой сетки при разработке специализированных процессоров для решения краевых задач. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит группу регистров, группу сдвигающих регистров, шесть элементов ИЛИ, шесть групп элементов И, три сумматора, четыре сдвигающих регистра, регистр, элемент НЕ, блок синхронизации, элемент И, блок проверки окончания итерационного процесса. 2 ил. б со 4 СЛ

Составитель В. Смирнов Редактор Н. Горват Техред В.Кад;ар Корректор Л, Пилипенко

2425/44

Тираж 672 Подписное ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Ячейка цифровой сетки для решения краевых задач | 1978 |

|

SU739542A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1987-06-15—Публикация

1985-11-10—Подача