1

Изобретение относится к цифровым вычислительным машинам для программного управления и, с точки зрения конструкций вычислительного устройства, может быть использовано при пост- ;роении специализированных вычисли- тельных устройств для осуществления сформирования последовательности ко- манд применительно, например, к при- |водам станков с программным управле- |нием.

Целью изобретения является расширение области применения устройства Эа счет формирования последователь- .йости команд, которые представляют сетевую структуру.

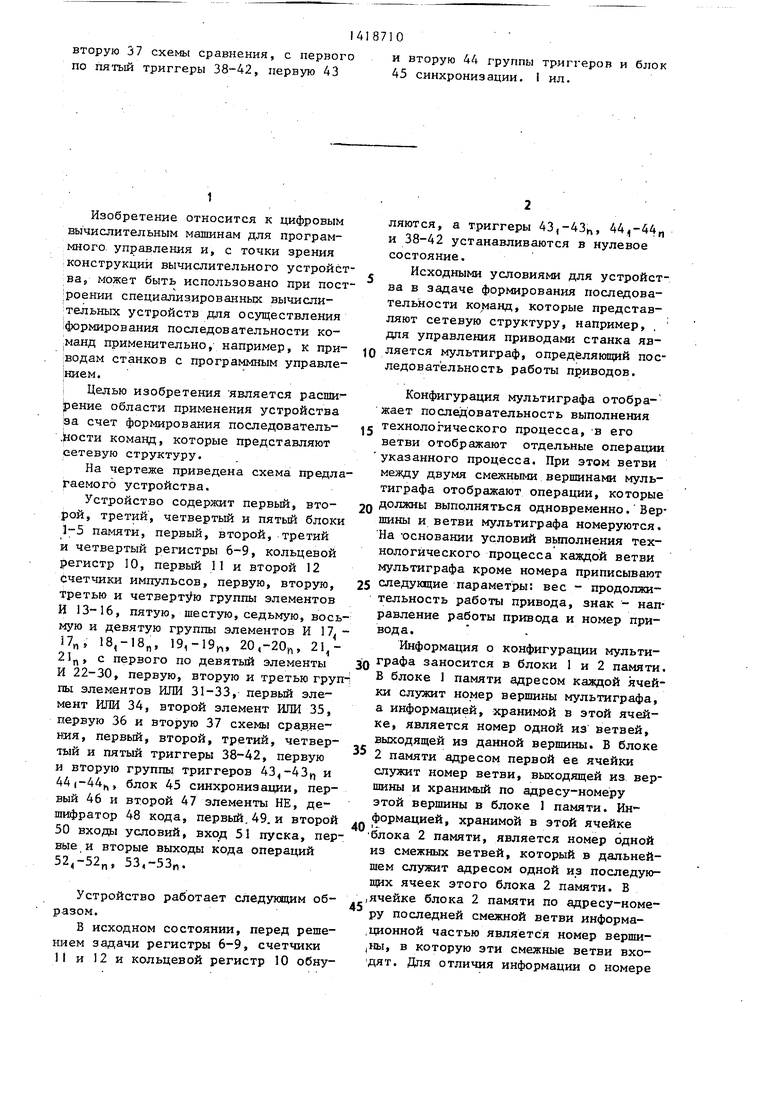

На чертеже приведена схема предлагаемого устройства.

Устройство содержит первый, второй, третий, четвертый и пятый блоки 1-5 памяти, первый, второй, третий и четвертый регистры 6-9, кольцевой регистр 10, первый П и второй 12 счетчики импульсов, первую, вторую, третью и четверТ5 ю группы элементов И 13-16, пятую, шестую,седьмую, восьмую и девятую группы элементов И 17„, 18,-18„, 19,-19, 20,-20„, 21,- 21„, с первого по девятый элементы И 22-30, первую, вторую и третью груп пы элементов ИЛИ 31-33,- первый элемент ИЛИ 34, второй элемент ИЛИ 35, первую 36 и вторую 37 схемы сра.в.не- ния, первый, второй, третий, четвертый и пятый триггеры 38-42, первую и вторую группы триггеров 43,-43ц и 44(-44, блок 45 синхронизации, первый 46 и второй 47 элементы НЕ, дешифратор 48 кода, первый. 49, и второй 50 входа условий, вход 51 пуска, пер- ные и вторые выходы кода операций 52,-52„, 53,-53«.

Устройство работает следукщим образом.

В исходном состоянии, перед решением задачи регистры 6-9, счетчики II и 2 и кольцевой регистр 10 обнуляются, а триггеры 43,-43|,, и 38-42 устанавливаются в нулевое состояние.

Исходными условиями для устройства в задаче формирования последовательности команд, которые представляют сетевую структуру, например, . дпя управления приводами станка яв- Q ляется мультиграф, определяющий последовательность работы приводов.

Конфигурация мультиграфа отображает последовательность выполнения

с технологического процесса, в его

ветви отображают отдельные операции указанного процесса. При этом ветви между двумя смежными вершинами мультиграфа отображают операции, которые

Q должны выполняться одновременно. Вершины и ветви мультиграфа номеруются. На -основании условий вьтолнения технологического процесса каждой ветви мультиграфа кроме номера приписывают

5 следующие параметры: вес - продолжительность работы привода, знак - направление работы привода и номер привода.

Информация о конфигурации мультиQ графа заносится в блоки 1 и 2 памяти. В блоке 1 памяти адресом каждой ячейки служит номер вершины мультиграфа, а информацией, хранимой в этой ячейке, является номер одной из ветвей, выходящей из данной вершины. В блоке

2 памяти адресом первой ее ячейки служит номер ветви, выходящей из вершины и хранимый по адресу-номеру этой вершины в блоке 1 памяти. Информацией, хранимой в этой ячейке блока 2 памяти, является номер одной из смежных ветвей, который в дальнейшем служит адресом одной из последующих ячеек этого блока 2 памяти. В ,ячейке блока 2 памяти по адресу-номеру последней смежной ветви информа- .ционной частью является номер верши- ,иы, в которую эти смежные ветви вхо- дят. Дпя отличия информации о номере

0

5

3I4187IO

от номера вершины в блок 2 паслч .т п

мяти введена метка - значащая единица. Эта единица или метка заносится в последний разряд, который вьщелен специально, только тех яче:ек памяти, информационная часть которых составляет номер вершины. Остальные параметры ветвей мульт играфа заносятся в блоки 3 и 4 памяти. В блоке 3 памяти адресом каждой ячейки служит но- мер ветви мультиграфа, а информационной частью - номер привода и знак, определяющий направление работы-привода. В блоке 4 памяти адресом каждой ячейки также служит номер ветви мультиграфа, а информационной частью вес, характеризующий продолжительность работы привода, номер которого :приписан данной ветви.

Перед началом решения задачи в регистры 6 и 7 через входы 49 и 50 условий заносятся соответственно номера начальной и конечной верпшн мультиграфа.

Работа устройства Начинается с момента подачи сигнала на вход 51 пуска. Вся работа устройства представляет, собой циклически повторяющиеся .и следующие друг за другом два этапа Первьй этап включает загрузку блока 5 памяти информацией о продоллситель- ности работы того или иного привода. Направление работы этих приводов при этом загружается в первую 43j|-43n и вторую 44(,-44 группы триггеров. Второй этап включает слежение за продолжительностью работы каждого привода и отключение его в требуемый момент времени.

Первый этап заключается в следующем. Сигнал с полюса 51 устанавливает триггеры 38 и 39 в единичное состояние. Единичное состояние триггера 39 вьщает разрешение, которое поступает на входы элементов И 14 группы. Это обеспечивает прохождение кода - номер начальной вершины мультиграфа, ; через группы элементов И 14 и ИЛИ 33 на адресный вход блока 1 памяти.

Единичное состояние триггера 38 вьщает разрешение на элемент И 23, что позволяет импульсу ГИ 1 с блока 45 синхронизации пройти через этот элемент и установить триггер 40 в ёдиничное состояние. Причем блок 45 синхронизации вьщает на первых четырех своих выходах импульсы, сдвинутые относительно друг друга, частота

0

5

0

5

0

5

0

5

0

5

следования каждого из которых вьше, частоты импульсов, выдаваемых на пя- .том выходе, во столько раз, сколько приводов у станка.

Единичное состояние триггера 40 вьщает разрешение на входы элементов И 25, 27 и группы элементов И 16. В результате, импульс ГИ 2 от блока 45 синхронизации поступает на вход установки в единицу триггера 41 и устанавливает его в единичное состояние, а импульс ГИ 3 проходит через элемент И 27 и поступает на вход считывания блока 1 памяти. Кроме того, импульс ГИ 3 с выхода элемента И 27 поступает через элемент ЮТ- 34 на вход занесения информации в регистр 9. В результате, информация, считываемая из ячейки по адресу - номер начальной вершины с выхода блока 1 памяти, пос- тупает через группы элементов И 16. и ИШ1 31 на вход регистра 9 и записывается в него. Этой информацией будет номер первой ветви, выходящей из начальной вершины мультиграфа.

Единичное состояние триггера 41 вьщает разрешение на входы элементов И 24 и 26. Разрешение на входе элемента И 24 дает возможность импульсу ГИ 4 пройти через этот элемент и установить триггеры 40 и 39 в нулевое состояние. Нулевое состоязше триггера 40 снимает разрешение с входов элементов И 25 и 27, что не позволяет проходить очередным импульсам ГИ 2, и ГИ 3 соответственно через эти элементы, и разрешение с входа элементов И группы 16.

Разрешение, поступившее на вход элемента И 26 с прямого выхода триггера 41, дает возможность импульсу ГИ 1 пройти, через элемент И 26 на вход кольцевого регистра 10 При этом на первом разрядном вькоде кольцевого регистра 10 появляется сигнал, который поступает на вход считывания блоков 3 и 4 памяти, на вход записи блока 5 памяти и на один из входов каждого элемента И . В результате с информационного выхода блока 3 памяти через группу элементов ИЛИ 32 на адресный вход блока 5 памяти и на вход дешифратора 48 кода поступает номер привода станка. Одновременно на один из входов всех эле- ментов И 18;-18п поступает информация о направлении работы указанного привода. Причем условно принято пря

51

мое направление работы привода кодировать нулем, а обратное - единицей. Одновременно с этим с информационного выхода блока 4 памяти на информа- 1 онный вход блока 5 памяти поступа- ет продолжительность работы привода. Информация, считываемая из блоков 3 и 4 памяти, находилась в ячейке, адрес которой определяет номер ветви мультиграфа, поступаюищй из регистра 9.

Деишфрация номера привода дешифратором 48 кода позволяет выбрать Соответствующие этому приводу элемен ТЪ И из каждой группы элементов И , и И . При этом триггер из группы триггеров 43,-43„ и триггер из группы устанавливаются в соответствующее состояние. триггер из группы триггеров Устанавливается в единичное состоящие, так как сигнал с выхода выбранного дешифратором 48 кода элемента Ц 17 из группы элементов И 17(-17 поступает на вход установки единицы ооответствукядего этому элементу триггера. Триггер из группы триггеров 44,-44. устанавливается в единичное состояние, если соответствукиций ему привод имеет обратное направление работы, что обеспечивается прохождением единицы из блока 3 памяти через выбранный депшфратором 48 кода элемент И 18i на вход установки в 1 триггера 44,. В противном случае {прямое направление работы привода) Триггер 44; останется в нулевом состоянии, так как из блока 3 памяти на вход элементов И 18,-18ц 1 не поступает.

Таким образом, в результате действия сигнала, поступившего с первого разрядного выхода кольцевого регистра в блок 5 памяти, в ячейку по адре му - номер привода, будет записана продолжительность работы привода, а триггеры, соответствующие данному приводу, из группы триггеров , и 44,-44п, будут установлены в единичное или нулевое состояние.

Поступление очередного импульса ITi 1 через элемент И 26 на вход кольцевого регистра 10 снимает сигнал с его первого разрядного выхода и выдает сигнал на втором разрядном выходе Сигнал со второго разрядного выхода кольцевого регистра 10 поступает на вход считывания блока 2 памяти и

0

20

25

87

с

g

30

35

40

50

55

1 О6

вход занесения информации в регистр 8.

На адресный вход блока 2 памяти поступает номер ветви с выхода регистра 9. Из ячейки блока 2 памяти по этому адресу считывается информация, которой является номер смежной ветви и которая поступает на вход регистра 8. Считываемый из блока 2 памяти номер записывается в.регистр 8.

Поступление очередного импульса ГИ 1 через элемент И 26 на вход кольцевого регистра 10 снимет сигнал с его второго разрядного выхода и выдает сигнал на третьем разрядном выходе С третьего разрядного вьгхода регистра. 10 сигнал через элемент ИЛИ 34 поступает на вход занесения информации регистра 9. По сигналу, поступившему с . выхода элемента ИЛИ 34, информация с выхода регистра 8 через группу элементов И 15 и ИЛИ 31 поступает на вход регистра 9 и записывается в нем. Это происходит потому, что на втором входе группы элементов И 15 есть разрешение с выхода элемента НЕ 46. Разрешение на выходе элемента НЕ 46 присутствует до тех пор, пока на его вход не поступает метка, которая представляет значащую единицу в последнем разряде ячейки памяти.

Очередной импульс ГИ 1, поступивший через элемент И 26 на вход кольцевого регистра 10, снимает сигнал с его третьего разрядного выхода и выдает сигнал на первом разрядном выходе.

В дальнейшем, описанные вьш1е операции первого этапа повторяются. При этом в регистр 9 будет записана информация, которой является номер первой из снежных ветвей.

Окончание первого этапа (загрузки) определяется моментом появления метки из блока 2 памяти на выходе регистра 9. Метка свидетельствует о том, что в регистре 8 находится номер вершины мультиграфа, в которую входят смежные ветви. Эта метка снимет разрешение с входов элементов И группы 15 и поступает на входы установки в О и 1 триггеров 41 и 42 соответственно. В результате, триггер 41 устанавливается в нулевое состояние, а триггер 42 - в единичное. Нулевое состояние триггера 41 прекращает поступление импульсов ГИ 1 на

7U

вход кольцевого регистра 10 через элемент И 26.

Единичное состояние триггера 42 свидетельствует о том, что устройство перешло к выполнению второго этапа. Единичное состояние триггера 42 выдает разрешение на элементы И 28- 30 и на входы всех элементов И 20„ и 21,-21. Это разрешение подключает триггеры 43,-43К) и к приводам. Каждый привод соединяется с устройством с помощью выходов 52,- 52„ , 53,-53„. Причем каждый привод соединяется с одним выходом из группы 52,-52 и одним из группы .. Если на выходе 53 появляется положительный сигнал относительно одноименного выхода 52;, то привод работает в прямом направлении. Если на вьгходе 52; появляется положительньй сигнал относительно одноименного выхода 53:,, то привод работает в обратном направлении. Направление работы определяет ся триггером 44;. Отсутствие сигналов одновременно на обоих входах 52 и 53: свидетельствует о том, что данfl

ный привод в настоящий момент вообще не участвует в работе.

Разрешение с прямого выхода триггера 42 дает возможность.импульсам ГИ 1 от блока 45 синхронизации поступать через элемент И 28 на вход счетчика 12 импульсов. Эти импульсы накапливаются в счетчике 12 импульсов. Сле- дов-ательно, на выходе счетчика 12 меняется код, который поступает через группу элементов ИЛИ 32 на адресный вход блока 5 памяти. Этим обеспечивается смена адреса ячеек блока 5 памяти. Одновременно на вход считывания блока 5 памяти поступают -с выхода элемента И 30 импульсы ГИ 2, что обеспечивает считывание информации из ячеек блока 5 памяти. Этой информацией является продолжительность работы привода, которая поступает на первый вход схемы 37 сравнения. На второй вход схемы 37 сравнения поступает код с выхода счетчика 11 импульсов. Код, поступающий из счетчика 11 импульсов, является кодом текущего времени. Он формируется счетчиком 11 импульсов в результате накопления им импульсов, которые поступают через элемент И 29 от блока 45 синхронизации. Эти импульсы имеют частоту следования, про7108

порциоиальную единице времени (напри- . мер, секунда, минута, час и т.д.)При совпадении кодов схема 37,

сравнения выдает сигнал, который пос- тупает на входы группы элементов И 19,-19. Этот сигнал пройдет только через то т эле.мент И 19, , который вы берет дешифратор 48 кода. Такой элемент И 19; соответствует приводу, номер которого в данный момент присутствует на адресном входе блока 5 памяти и входе дешифратора 48 кода,

g Сигнал с выхода элемента И- 19| поступает на соответствующие триггеры 43; и 44 и устанавливает их в нулевое состояние. Это, в свою очередь, снимает положительный сигнал

Q с соответствующих выходов 52; и 53; и привод, соединенный с этими выходами, прекращает их работу.

Второй этап завершается в тот момент, когда на выходе элемента ИЛИ

5 35 исчезает сигнал. Это случится тогда, когда все триггеры уста- -Навливаются в нулевое состояние, что свидетельствует о -завершении работы всех приводов по заданной программе.

0 При этом все триггеры у, также будут установлены в нулевое состояние. В результате, на выходе элемента НЕ 47 появляется сигнал, который поступает на вход установки в О

триггера 42 и устанавливает этот триггер в нулевое состояние.

Нулевое состояние триггера 42 снимает разрешение с элементов И 28- 30 и вьщает разрешение на элемент

И 23. После чего устройство опять

переходит к выполнению первого этапа. Отличие будет только в том, что на адресный вход блока 1 памяти через группу элементов И 13 и ИЛИ 33 с выхода регистра 8 поступает номер вершины, в которую входят смежные ветви. Это обеспечивается тем, что триггер 43 находится в нулевом состоянии и нет разрешения на входы элементов

И группы 14. Разрешение на вход группы элементов И 13 в этом случае поступает с прямого выхода триггера 40. Описанные вьш1е этапы будут циклически повторяться до тех пор, пока.

номер вершины, записанньй в регистре 7, не совпадет с номером вершины, в которую входят смежные ветви и который поступает с выхода регистра 8. Сравнение производится следующим образом. Номер конечной вершины мульти- графа с выхода регистра 7 поступает на схему 36 сравнения, куда с выхода ре|гистра 8 через группу элементов И |13 и ИЛИ 33 поступает номер вершины, в которую входят смежные ветви. В случае совпадения номеров, схема 36: сравнения кодов выдает сигнал на первый вход элемента И 22, На второй вх|од элемента И 22 з этот момент пос- туЬает метка с выхода регистра 8. В результате, на вькоде элемента И 22 пойвляется сигнал, который поступает на вход установки в О триггера 38 и устанавливает его в нулевое состояние. Это свидетельствует об окончаний решения задачи формирования последовательности команд, которые представляют сетевую структуру, для уп- ра:рления приводами.

Ф6рму;ла изобретения

I Устройство программного управления, содержащее первый, второй, третий, четвертый и пятый блоки памяти пер|вый, второй, третий и четвертый регистры, первьй счетчик импульсов, первую группу элементов -И, первую и втс|рую группы элементов .ИЛИ, первую и в горую схемы сравнения, первый триггер и блок синхронизации, причем; информационные входы первого и вто- I рого регистров соответственно явля- . ются первым и вторым входами условий устройства, выходы второго .регистра соединены с первой труппой входов пвр|вой схемы сравнения, с первого по (п-:1)-й (где п - число управляемых устройством операционных блоков) выходы третьего регистра соединены с первыми входами элементов И первой группы, информационный вход третьего регистра соединен с выходом второго блока памяти, адресный вход которого соединен с выходом четвертого регистра и с адресными входами третьего и чет1зертого блоков памяти, информаци- входы которого соединены с выходами элементов ИЛИ первой группы, а адресные входы пятого блока памяти соединены с выходами элементов ИЛИ второй группы,.отличающее - с я тем, что, с целью расширения области применения за счет формирования последовательности команд, которые представляют сетевую структуру, в устройство введены вторая, третья, четвертая, пятая, шестая, седьмая, восьмая и девятая группы элементов

5

0

И, с первого по девятый элементы И, первый и второй элементы ИЛИ, первый и второй элементы НЕ, третья группа элементов ИЛИ, второй очетчик импульсов, дешифратор кода, кольцевой регистр, второй, третий, четвертый, пятый триггеры и первая и вторая группы триггеров, причем информационные выходы первого регистра соединены с первыми входами элементов И второй группы, вторые входы которых соединены с прямым выходом второго триггера, а выходы Ьлементов И второй группы соединены с первьми элементами ИЛИ третьей группы, вторые входы соединены с выходами элементов И первой группы, вторые входы которых соединены, с первой группой входов шестого элемента И, с прямым выходом третьего триггера, с первой группой входов четвёртого элемента И и с первыми входами элементов И четвертой rpyfifefj: вторые входы которых соединены с вы-

5 ходами первого блока памяти, а выходы элементов И четвертой группы соединены с первыми входами элементов, ШШ первой группы, вторые входы кото рых соединены с выходами элементов И

0 третьей группы, первые входы которых, соединены с первыми входами элементов И первой группы, а вторые входы элементов И третьей группы соединены

с выходом первого элемента НЕ, вход

I .

5 которого соединен с (п)-м вькодом третьего регистра, с первым входом первого элемента И, с входом установки в О четвертого триггера и с входом установки в 1 пятого триггера,

0 а второй вход первого элемента И соединен с выходом первой схемы сравнения, вторая группа входов которой соединена с выходами элементов ШШ третьей группы и с адресными входами (

5 первого, блока памяти, вход разрешения считывания которого соединен с выходом шестого элемента И и с первым входом первого элемента ИЛИ, причем счетный вход первого счетчика

0 импульсов соединен с выходом восьмого элемента И, а выход первого счетчика импульсов соединен с первым входом второй схемы сравнения, второй вход которой соединен с пято5 го блока памяти, информационный вход которого соединен с выходом четвертого блока памяти, вход разрешения считывания которого соединен с входами разрешения считывания третьего и вхо11 4

ом разрешения записи пятого блоков памяти, с первыми входами элементов пятой группы и с первым выходом кольцевого регистра, а вторые входы элементов И пятой группы соединены с первыми входами элементов И шестой и седьмой групп и с первым выходом дешифратора кода, информационные входы которого соединены с адресными входами пятого блока памяти и выходами элементов ИЛИ второй группы, первые входы которых соединены с выходами второго счетчика импульсов, счетный вход которого соединен с выходом .. седьмого элемента И, а вторые входы элементов ИЛИ второй группы соединены с (ц-1) выходами третьего блока памяти, (п)-й выход которого соединен с вторыми входами элементов И шестой группы, выходы которых соединены с входами установки в 1 триг- геров второй группы, прямые выходы которых соединены с первыми входами элементов И восьмой группы, вторые входы которых соединены с первыми входами элементов И девятой группы триггеров первой группы, прямыми вы- ходами первой группы входов второго элемента ИЛИ, выход которого соеди- нен с входом второго элемента НЕ, вы- ход которого соединен с входом уста- новки в О пятого триггера, входы установки в 1 триггеров первой группы соединены с выходами элементов И пятой группы, входы установки в О триггеров первой и второй групп соединены с выходами элементов И седьмой группы, вторые входы которых соединены с выходами второй схемы сравнения, инверсные выходы триггеров второй группы соединены с вторыми входами элементов И девятой группы, третьи входы которых соединены с третьими входами элемен- тов И восьмой группы, с первыми входами седьмого, восьмого и девятого, элементов И и прямым выходом пятого триггера, прямой выход первого триг

5

0

5

0

5

0

10 . 12

гера соединен с первым входом второго элемента И, выход которого соединен с прямым входом третьего триггера, входы установки в О второго и третьего триггеров соедине нь. с выходом третьего элемента И, первый вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом пятого и вторыми входами седьмого и второго элементов И, третий выход блока синхронизации соединен с второй группой входов четвертого и вторым входом девятого элементов И, выход которого соединен с входом разрешения считывания пятого блока памяти, а четвертый и пятый выхода блока сип хронизации соединены соответственно с вторым входом, восьмого и второй группой входов шестого элементов И, а вторые входы третьего и пят-ого элементов И соединены с прямым выходом четвертого триггера, вход установки в 1 которого соединен с выходом четвертого элемента И, а инверсный выход четвертого триггера соединен с третьим входом второго элемента И, четвертый вход которого соединен с инверсным выходом пятого триггера, выход пятого элемента И соединен с информационньм входом кольцевого регистра, третий выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с выходом разрешения записи четвертого регистра, второй выход кольцевого регистра соединен с входом разрешения записи третьего регистра и входом разрешения считывания второго блока памяти, выход первого элемента И соединен с входом установки в

5

первоIt 1 ч

1 коГО триггера, вход установки в торого соединен с входом установки S 1 второго триггера-и является входом пуска устройства, первыми и вто- рыми выходами кода операций которого являются соответственно выходы элементов И восьмой и девятой групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство программного управления | 1991 |

|

SU1781671A1 |

| Устройство для исследования графов | 1979 |

|

SU807313A2 |

| Устройство для исследования графов | 1983 |

|

SU1134946A1 |

| Устройство для решения задачи поиска длиннейшего пути | 1983 |

|

SU1206791A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для исследования графа | 1978 |

|

SU744593A1 |

| Устройство для исследования графов | 1975 |

|

SU643880A1 |

| Устройство для исследования графов | 1979 |

|

SU877552A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1242980A1 |

| Устройство для распаковки команд | 1987 |

|

SU1464157A1 |

Изобретение относится к цифровым вычислительным машинам для программного управления и может быть использовано при построении специализированных вычислительных устройств для формфованыя последовательности команд применительно к приводам станков с nporpaMNnibiM управлершем. Цель изобретения - расширение области применения. Цель достигается за счет фop шpoвaния последовательности команд, которые представляют собой сетевую структуру. Устройство содержит с первого по пятый блоки 1-5 памяти, с первог о по четвертый регистры 6-9, кольцевой регистр 10, первьй II и второй 12 счетчики импульсов, с первой по девятую группы элементов И 13-21, с первого по девятый элементы И , с первой по третью группы элементов ШШ 31-33, первый 34 и второй 35 элементы И,ПИ, первую 36 и t.

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения задачи поиска длиннейшего пути | 1983 |

|

SU1206791A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-09—Подача