Изобретение относится к цифровым вычислительным машинам для программного управления v может быть ис пользовано при построении (пециализировннных вычислительных устройств для формирования последовательно:™ команд применительно к приводам станков с программным управлением.

Известно устройство для моделирования топологии сетей, которое содержит четыре блока памяти, каждый из которых предназначен для хранения адресов начальных и конечных узлов ветвей сети, адресов, вход я щи и выходящих ветвей сети, четырех регистров каждый из которых предназначен для хранения адресов входящей и выходяшей ветви сети адресов конечного узла ветв-i и конечного узла сети, два триггера, дешифратор две линии задержки, сеть элементе ИЛИ, шесть элементов И и элемент НЕ Э ги элементы с овместно с дешифратором сравнения кодов, который выполнен на элементах И и ИЛИ, соединены в | соответствующую схему, что позволяет мб-i делировать только конфигурацию сети или графа. К недостаткам этих устройств относится то,.что для решения задач на сетях и графах они требуют привлечения моделей ветвей с определенным техническим выполнением для каждой конкретной задачи

Наиболее близким по назначению и конструктивному выполнению к заявляемому является устройство, которое содержит первый, второй блоки памяти последовательности техпроцесса, третий, четвертый и пятый блоки памяти параметров техпроцесса, с первого по четвертый регистры, пер- ч вый и второй счетчики импульсов, первую, вторую третью, четвертую, пятую шестую, седьмую, восьмую и девятую группы элементов И, первую, вторую и третью гр/ппы элементов ИЛИ, первую и вторую

00

«&

о

сравнения, с первого по девятый элементы И, первый и второй элементы ИЛИ первый и второй элементы НЕ, дешифратор кода, кольцевой регистр, с первого по пятый триггеры, первую и вторую группы триггеров и блок синхронизации, причем информационные входы первого и второго регистров соответственно являются первым и вторым входами условий устройства, выходы второго регистра соединены с первой группой входов первой схемы сравнения, с первого по (п-1)-й (где п - число элементов в перечисленных группах устройства), выходы третьего регистра соединены с первыми входами элементов И первой группы, информационный вход третьего регистра соединен с выходом второго блока памяти последовательности техпроцесса, адресный вход которого соединен с выходом четвертого регистра и с адресными входами третьего и четвертого блоков памяти, параметров техпроцесса, (п-1) информационных вхЪдов четвертого регистра соединены с выходами элементов ИЛИ первой группы, а адресные входы пятого блока параметров техпроцесса соединены с выходами элементов ИЛИ второй группы, причем информационные выходы первого регистра соединены с первыми входами элементов И второй группы, вторые входы которых соединены с прямым выходом второго триггера, а выходы элементов И второй группы соединены с первыми входами элементов ИЛИ третьей группы, вторые входы соединены с выходами элементов И первой группы, вторые входы которых соединены с первым входом шестого элемента И, с прямым выходом третьего триггера, с Первым входом четвертого элемента И и с первыми входами элементов И четвертой группы, вторые входы которых соединены с выходом первого блока памяти последовательности техпроцесса а выходы элементов И четвертой группы соединены с первыми входами элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов И третьей группы, первые входы которых соединены с первыми входами элементов Л первой группы, а вторые входы элементов И третьей группы соединены с выходом первого элемента НЕ, вход, которого соединен с (п-1)-м выходом третьего регистра, с первым входом первого элемента И, с входом установки в О четвертого триггера и с входом установки в 1 пятого триггера, а второй вход первого элемента И соединен с выходом первой схемы сравнения, вторая группа входов которой соединена с выходами элементов ИЛИ третьей группы и с адресными входами первого блока памяти последовательности техпроцесса, вход разрешения считывания которого соединен с выходом шестого элемента И и с первым входом первого элемента ИЛИ, причем счетный вход первого счетчика импульсов соединен с выходом восьмого элемента И, а выходы первого счетчика импульсов соединены с первой группой входов второй схемы сравнения,

0 вторая группа входов которой соединена с первой группой выходов пятого блока памяти параметров техпроцесса, информационный вход которого соединен с выходом третьего блока памяти, вход разрешения

5 считывания которого соединен с входами разрешения считывания четвертого и входом разрешения записи пятого блоков параметров техпроцесса, с первыми входами элементов И пятой группы и с первым выхо0 дом кольцевого регистра, а вторые входы элементов И пятой группы соединены с первыми входами элементов И шестой и седьмой групп и с выходом дешифратора кода, информационные входы которого соедине5 ны с выходами элементов ИЛИ второй группы, первые входы которых соединены с выходами второго счетчика импульсов, счетный вход которого соединен с выходом седьмого элемента И, а вторые входы эле0 ментов ИЛИ второй группы соединены с (п-1) выходами четвертого блока памяти параметров техпроцесса, а выходы элементов И шестой группы соединены с входами установки в 1 триггеров второй группы, пря5 мые выходы которых соединены с первыми входами элементов И восьмой группы, вторые входы которых соединены с первыми входами элементов И девятой группы и с прямыми выходами триггеров первой груп0 пы, с входами второго элемента ИЛИ, выход которого соединен с входом второго элемента НЕ, выход которого соединен с входом установки в О пятого триггера, а входы установки в 1 триггеров первой группы

5 соединены с выходами элементов И пятой группы, входы установки в О триггеров первой группы соединены с выходами элементов И седьмой группы, а инверсные выходы триггеров второй группы соединены с

0 вторыми входами элементов И девятой группы, третьи входы которых соединены с третьими входами элементов И восьмой группы, с первыми входами седьмого, восьмого и девятого элементов И и прямым вы5 ходом пятого триггера, прямой выход первого триггера соединен с первым входом второго элемента И, выход которого соединен с прямым входом третьего триггера, входы установки в О второго и третьего триггеров соединены с выходом третьего

элемента И, первый вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом пятого и вторыми входами седьмого и второго элементов И, третий выход блока синхронизации соединен с вторыми входами четвертого и девятого элементов И, выход последнего из которых соединен с входом разрешения считывания пятого блока памяти, а четвертый и пятый выходы блока синхронизации соединены соответственно с вторым входом восьмого и шестого элементов И, вторые входы третьего и пятого элементов И соединены с прямым выходом четвертого триггера, вход установки в 1 которого соединен с выходом четвертого элемента И, а инверсный выход четвертого триггера соединен с третьим входом второго элемента И, четвертый вход которого соединен с инверсным выходом пятого триггера, выход пятого элемента И соединен с информационным входом кольцевого регистра, третий выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом разрешения записи четвертого регистра, второй выход кольцевого регистра соединен с входом разрешения записи четвертого регистра, второй выход кольцевого регистра соединен с входом разрешения записи третьего регистра и входом разрешения считывания второго блока памяти последовательности техпроцесса, выход первого элемента И соединен с входом установки в О первого триггера, вход установки в 1 которого соединен с входом установки в 1 второго триггера и является входом пуска устройства, первыми и вторыми выходами кода операций которого являются, соответственно, выходы элементов И восьмой и девятой групп, причем первый и второй выходы синхронизации соответственно соединены с вторым входом элемента И и с вторыми входами пятого, седьмого и второго элементов И.

Недостатком известного устройства является то, что оно в процессе формирования последовательности команд, которые представляют сетевую структуру (например, команд управления приводами станка с программным управлением), контролирует только время воздействия каждой команды на исполнительный орган (механизм) и не осуществляет контроль за величиной управляющего сигнала исполнительного механизма.

Целью изобретения является повышение надежности за счет полноты контроля выполнения последовательности команд, которые представляют сетевую структуру

управления исполнительными механизмами и повышения точности РЫПОЛНРСМОГО технологического процесса.

Поставленная цель достигается тем, что

5 в устройство программного управления вне- дены коммутатор, десятая группа элементов И, третий и четвертый элементы ИЛИ, десятый, одинадцатый, и двенадцатый элементы И и третья схема сравнения, первый

0 выход которой соединен с первым входом двенадцатого элемента И, выход которого соединен с четвертым элементом ИЛИ, второй вход и выход которого соединен соответственно с (п-1)-м информационным

5 выходом четвертого блока памяти и с вторыми входами элементов И шестой группы, а второй выход третьей схемы сравнения со- единен с первым входом десятого элемента И, второй вход и выход которого соединен

0 соответственно с выходом третьего элемента ИЛИ, первый и второй вход которого соединены соответственно с первым и вторым выходом второй схемы сравнения, и с вторыми входами элементов И седьмой группы,

5 а третий вход десятого элемента И соединен с первым входом одиннадцатого элемента И, вторым входом двенадцатого элемента И и прямым выходом пятого триггера, а выход одиннадцатого элемента И соединен с перO выми входами элементов И десячтой группы, выходы которых соединены с входами уста- новки в О триггеров второй группы, а вторые входы элементов И десятой группы соединены соответственно с выходами де3 шифратора кода, причем первая группа входов третьей схемы сравнения соединена с второй группой информационных выходов пятого блока памяти параметров техпроцесса, а вторая группа входов третьей схемы

0 сравнения соединена с выходом коммутатора, входы которого являются входом изменяющихся условий управляющего сигнала устройства.

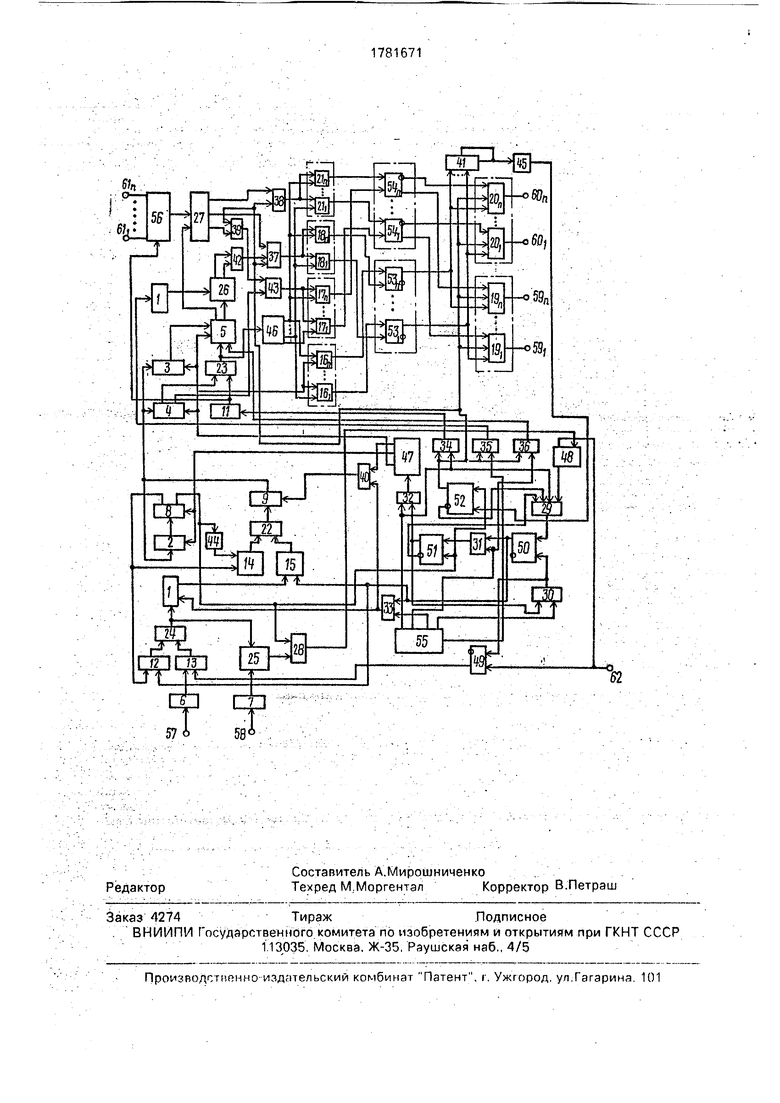

На чертеже приведена блок-схема уст5 ройства программного управления.

Устройство содержит первый, второй блоки памяти 1, 2 последовательности техпроцесса, третий, четвертый и пятый блоки 3, 4, 5 памяти параметров техпроцесса, пер0 вый, второй, третий и четвертый регистры 6-9, первый и второй счетчики импульсов 10, 11, первую, вторую, третью, четвертую, пятую, шестую, седьмую, восьмую, девятую и десятую группы элементов И 12-21, пер5 вую, вторую и третью группы элементов ИЛИ 22-24. первую, вторую и третью схемы сравнения 25-27, с первого по двенадцатый элементы И 28-39, с первого по четвертый элементы ИЛИ 40-43, первый и второй элементы НЕ 44, 45. дешифратор кода 46, кольцевой регистр 47, с первого по пятый триггеры 48-52, первую и вторую группу триггеров 53, 54, блок синхронизации 55, коммутатор 56, первый и второй входы условий 57, 58, первый и второй выходы кода операций 59i-59n. 60i-60n, вход изменяющихся условий управляющего сигнала 611- 61П, вход пуска устройства 62.

Число триггеров в первой и второй группах - 53i-53n, 54i-54n число элементов И в пятой, шестой, седьмой, восьмой, девятой и десятой группах- 16i-16n, 17i-17n, 18i-18n, 19i-19n, 20i-20n. 21i-21n равно числу приводов (исполнительных органов) станка.

Схемы сравнения 25, 26, 27 предназначены для поразрядного сравнения двух кодов и выдачи сигналов на одном из своих выходов в зависимости от знака , или . Устройство работает следующим образом.

В исходном состоянии перед решением задачи регистры 6,7,8,9, кольцевой регистр 47, счетчики 11, 10, триггеры 48, 49, 50, 51, 52 и54-|-54п устанавливаются в исходное нулевое состояние.

Исходными данными задачи формирования последовательности команд, представляющих сетевую структуру для управления системой исполнительных механизмов, является мультиграф, определяющий последовательность работы приводов.

Под мультиграфом понимают такой граф, у которого любая пара вершин может быть соединена между собой более чем одной ветвью.

Конфигурация мультиграфа отображает последовательность выполнения технологического процесса, а его ветви отображают отдельные операции указанного процесса. При этом между двумя смежными вершинами мультиграфа отображают операции, которые должны выполняться одновременно. Их число соответствует числу исполнительных Механизмов, которые участвуют в технологическом процессе одновременно. Вершины и ветви мультиграфа нумеруются. На основании условий выполнения технологического процесса каждой ветви мультиграфа, кроме номера, присваивают следующие параметры: вес - характеризует продолжительность работы исполнительного механизма, уставка - оптимальная величина, по которой осуществляется управление отдельной операции технологического процесса, знак - начальное направление работы исполнительного механизма до достижения управляемым параметром заданного значения и номер привода.

Информация о конфигурации мультиграфа заносится в блоки памяти 1,2.8 блоке

памяти 1 адресом каждой ячейки служит номер вершины мультиграфа, а информацией, хранимой в этой ячейке, является номер одной из ветвей, выходящей из данной

вершины. В блоке памяти 2 адресом первой ее ячейки служит номер ветви, выходящей из вершины и хранимый по адресу-номеру этой вершины в блоке памяти 1. Информацией, хранимой в этой ячейке блока памяти

2, является номер одной из смежных ветвей, который в дальнейшем служит адресом одной из следующих ячеек этого блока памяти 2. В ячейке блока памяти 2 по адресу-номеру последней смежной ветви информационной

частью является номер вершины, в которую эти смежные ветви входят. Для отличия информации о номере ветви от номера вершины в блок памяти 2 введена метка - значащая единица. Эта метка заносится в ,

последний разряд, специально выделенный для тех ячеек памяти, информационная часть которых составляет номер вершины мультиграфа. Остальные параметры ветвей мультиграфа заносятся в блоки памяти 4, 3.

В блоке памяти 4 адресом каждой ячейки служит номер ветви мультиграфа, а информацией - номер привода и знак, определяющий начальное направление работы исполнительного механизма. В блоке памяти 3 адресом каждой ячейки также служит номер ветви мультиграфа, а информационная часть содержит данные как о продолжи- тельности работы исполнительного механизма, номер которого приписан данной ветви, так и оптимальное значение па раметра, по которому осуществляется управление направлением работы исполнительного механизма.

Шины установки всех триггеров регистров и счетчиков устройства в исходное состояние, а также шины занесения исходных данных на чертеже не показаны,

На чертеже также условно показаны ин- формационные шины, подключенные к полюсам 58, 57, 611-61 п. Разрядность первых двух шин определяется величиной максимально возможного номера начального и конечного узлов. Например, если при реше- нии конкретной задачи управления технологическим процессом количество узлов не превышает 255, то разрядность этих шин не превышает 8 при представлении информации в двоичном коде. Разрядность инфор- мационных шин, подключенных к полюсам 611-61 п, определяется исходя из максимальных величин регулируемых параметров, значения которых в двоичном коде снимаются с выходов аналого-цифровых преобра зователей.

Разрядность блоков памяти 3 и 5 определяется величиной продолжительности работы исполнительного механизма и величиной уставок.

Перед началом решения задачи в регистры 6 и 7 через входные полюса 57. 58 заносятся соответственно номера конечной и начальной вершин мультиграфа.

Работа устройства начинается с момента подачи сигнала на вход 62. Вся работа устройства представляет циклически повторяющиеся и следующие друг за другом два этапа. Первый этап включает в себя загрузку блока памяти 5 информацией о продолжительности работы того или иного исполнительного механизма и величине соответствующего оптимальному значению регулируемого параметра. Начальное направление работы исполнительных механизмов загружается в группу триггеров 54i-54n, а продолжительность работы - в группу триггеров 53 г53п. Второй этап включает слежение за текущими значениями регулируемых параметров с соответствующим переключением направления работы. При этом слежение за продолжительностью работы каждого исполнительного механизма и отключение его в требуемый момент времени происходит при условии bi PI, где bi - текущее значение регулируемого параметра, PI - значение уставки (величина оптимального значения управляемого параметра). Если при работе устройства возникает условие bi PI то устройство сменит направление работы соответствующего исполнительного механизма. В случае, если bi PI, то время работы исполнительного механизма будет увеличено. Это будет происходить до тех пор, пока не выполняется условие bi Pi

Выполнение первого этапа заключается в следующем. Сигнал с полюса 62 устанавливает триггеры 48 и 49 в единичное состояние. Единичное состояние триггера 49 выдает разрешение, которое поступает на вход группы элементов И 13. Это обеспечивает прохождение кода - номера начальной вершины мультиграфа через группы элементов И 13 и ИЛИ 24 на адресный вход блока памяти 1. Единичное состояние триггера 48 выдает разрешение на элемент И 29, что позволяет импульсу ГИ 1 блока синхронизации 55 пройти через этот элемент и установить триггер 50 в единичное состояние. Причем блок 55 выдает на первых четырех своих выходах импульсы, сдвинутые относительно друг друга, частота следования каждого из которых выше частоты импульсов, выдаваемых на пятом выходе, во столько раз, сколько исполнительных механизмов обслуживает устройство программного управления.

Единичное состояние триггера 50 выдает разрешение на входы элементов И 31, 33

5 и группы элементов И 12. В результате импульс ГИ 2 генератора импульсов 55 поступит на единичный вход триггера 51 и установит его в единичное состояние, а импульс ГИ 3 пройдет через элемент И 33 и

0 поступит на вход считывания блока памяти 1. Кроме того, импульс ГИ 3 с выхода элемента И 33 поступит через элемент ИЛИ 40 на вход значения информации в регистр 9. В результате информация, считываемая из

5 ячейки по адресу-номеру начальной вершины, с выхода блока памяти 1 поступит через группу элементов И 15 и ИЛИ 22 на вход регистра 9 и запишется в него. Этой информацией будет номер первой ветви, исходя0 щей из начальной вершины мультиграфа.

Единичное состояние триггера 51 выдает оазрешение на входы элементов И 32,30. Разрешение на входе элемента И 30 дает возможность импульсу ГИ 4 пройти через

5 этот элемент и установить триггеры 49 и 50 в нулевое состояние. Нулевое состояние триггера 50 снимает разрешение с входа группы элементов И 13 и с входов элементов И 31 и 33, что не позволяет проходить оче0 редным импульсам ГИ 2 и ГИ 3 соответственно через эти элементы,

t

Разрешение, поступившее на вход элемента И 32 с единичного выхода триггера 51,

5 дает возможность импульсу ГИ 1 пройти через элемент и 32 на вход кольцевого регистра 47. При этом на первом разрядном выходе кольцевого регистра 47 появится сигнал, который поступает на вход считыва0 ния блоков памяти 4,3, на вход записи блока памяти 5 и на один из входов каждого элемента И 16i-16,i В результате с информационного выхода блока памяти 4 через группу элементов ИЛИ 23 на адресный вход блока

5 памяти 5 и на вход дешифратора кода 46 поступит номер исполнительного механизма. Одновременно на один из входов всех элементов И 17i-17n через элемент ИЛИ 43 поступит информация о направлении рабо0 ты указанного исполнительного механизма. Причем условно принято прямое направление работы исполнительного механизма кодировать нулем, а обратное - единицей Одновременно с этим с информационного

5 выхода блока памяти 3 на информационный вход блока памяти 5 поступают данные об оптимальной величине регулируемого параметра и продолжительности работы исполнительного механизма Следует отметить, что информация, считанная из блоков иамяти 4, 3 находилась в ячейке, адрес которой определяет номер ветви мультиграфа, поступающий из регистра 9.

Дешифрация номера исполнительного механизма дешифратором кода 46 позволяет выбрать соответствующие этому исполнительному механизму элементы И и из каждой группы элементов И 16 и 17. При этом триггер из группы триггеров разрешения работы исполнительных механизмов 53i-53n и триггер из группы направления работы приводов 54i-54n устанавливаются в соответствующее состояние, т.к. сигнал с выхода выбранного дешифратором кода 46 элемента И 1 б поступает на единичный вход соответствующего этому элементу триггера. Триггер из группы триггеров 54i-54n устанавливается в единичное состояние, если соответствующий ему привод имеет обратное начальное направление работы, что обеспечивает прохождение разрешения из блока памяти1 4 через элементы ИЛИ 43 и выбранный дешифратором кода 46 элемент И 17| на единичный вход триггера 54|. В противном случае (прямое направление работы привода) триггер 54| остается в нулевом состоянии, т.к. из блока памяти 4 на вход элемента ИЛИ 43 разрешение не поступит.

Таким образом, в результате действия сигнала, поступившего с первого разрядного выхода кольцевого регистра 47 в блок памяти 5. в ячейку по адресу-номеру исполнительного механизма будет записана информация об оптимальном значении регулируемого параметра и продолжительности работы исполнительного механизма, а триггеры, соответствующие данному исполнительному механизму из группы триггеров 53i-53n и 54i-54n будут установлены в соответствующее состояние.

Поступление очередного импульса ГИ 1 через элемент И 32 на вход кольцевого регистра 47 снимает сигна/1 с его первого и выдает сигнал на его втором разрядном входе. Сигнал со второго разрядного входа кольцевого регистра 47 поступает на вход считывания блока памяти 2 и вход занесения информации в регистр 8. При этом на адресный вход блока памяти 2 поступает номер ветви с выхода регистра 9. Из ячейки блока памяти 2 по этому адресу считывается информация, которой является номер смежной ветви и которая поступит на вход регистра 8, и записывается в этот регистр.

Поступление очередного импульса ГИ 1 через элемент И 32 на вход кольцевого регистра 47 снимет сигнал с его второго разрядного выхода и выдаст сигнал на третьем его разрядном выходе. С третьего разрядного выхода регистра 47 сигнал через элемент ИЛИ 40 поступит на вход занесения информации регистра 9. По сигналу, пришедшему с выхода элемента ИЛИ 40, информация,

поступившая с выхода регистра 8 через группу элементов И 14 и ИЛИ 22 на вход регистра 9}запишется в нем, Это происходит потому, что на втором входе группы элементов И 14 есть разрешение с выхода элемента

0 НЕ 44, которое присутствует до тех пор, пока на вход элемента НЕ 44 не поступит- метка, которая представляет значащую единицу в последнем разряде регистра 8, как было описано раньше.

5Очередной импульс ГИ1. поступивший через элемент И 32 на вход кольцевого регистра 47, снимет сигнал с его третьего разрядного выхода и выдаст сигнал на первом разрядном выходе.

0 В дальнейшем описанные выше операции первого этапа повторяются. При этом в регистр 9 будет записываться информация - номера следующих смежных ветвей.

Окончание первого этапа (загрузки) оп5 ределяется моментом проявления метки на выходе регистра 8. Метка свидетельствует о том, что в регистре 8 находится информация о номере вершины мультиграфа, в которую входят смежные ветви. Эта метка снимет

0 разрешение с выхода группы элементов И 14 и поступит на нулевой и единичный входы триггеров 51 и 52 соответственно. В результате триггер 51 установится в нулевое, а триггер 52 - в единичное состояние. Нулевое

5 состояние триггера 51 прекратит поступление импульсов ГИ 1 на вход кольцевого регистра 47 через элемент И 32.

Единичное состояние триггера 52 свидетельствует о том, что устройство перешло

0 к выполнению второго этапа работы. Единичное состояние триггера 52 выдает разрешение на элементы И 34, 35, 36, 37, 38, 39 и на входы всех элементов И 19i-l9n и 20i-20n. Это разрешение подключает триггеры 53i5 53п и 54i-54n к исполнительным механизмам, Каждый исполнительный механизм соединяется с устройством посредством полюсов 59i-59n и 60i-60n. Причем k-й исполнительный механизм подсоединен к

0 полюсам 59ic60i. Если сигнал присутствует только на полюсе 59k,. то исполнительный механизм работает в прямом направлении, если же сигнал присутствует и на полюсе 60k - то в обратном направлении. Отсутст5 вне сигнала на полюсе 59k говорит о том, что k-й привод выключен.

Разрешение с единичного выхода триггера 52 дает возможность импульсам ГИ 1 от генератора импупьсов 55 поступать через элемент 34 на вход счетчика 11. В результате этого на выходе счетчика 11 будет меняться код, который поступает на адресный вход коммутатора 56 и через группу элементов ИЛИ 23 на адресный вход блока памяти 5 и вход дешифратора кода 44, Этим обеспечит- вается смена адреса ячеек блока памяти 5. Одновременно на вход считывания блока памяти 5 поступают с выхода элемента 36 импульсы ГИ 2, что обеспечивает считывание информации из ячеек блока памяти 5, информация об оптимальном значении регулируемого параметра PI, снимаемая с вторых п информационных выходов блока памяти 5, поступает на первый вход схемы сравнения 27. Текущее значение регулируе- мого параметра bi через полюс 611. коммутатор 5$ поступает из второй вход схемы сравнения 27. Если выполняется условие:

ЬГ Pi,

то сигнал с первого выхода схемы сравне- ния через И 38 и один из группы элементов И 21, на втором входе которого присутству; ет разрешение с 1-го дешифратора кода 46, поступит на нулевой вход триггера 54 и установит его в нулевое состояние (либо под- твердит это состояние). Если же выполняется условие:

bi PI.

то сигнал со второго выхода схемы сравнения через элемент И 39, ИЛИ 43 и один из группы элементов И 17 поступит на единичный вход триггера 54 и установит его в единичное состояние (либо подтвердит это состояние). Таким образом, осуществляется управление направлением работы 1-го ис- полнительного механизма в соответствии с текущим значением параметра.

С первых п информационных выходов блока памяти 5 снимается информация о продолжительности работы привода, кото- рая поступает на вход схемы сравнения 26, На другой вход схемы сравнения 26 поступает код с выхода счетчика импульсов 10. Код, поступающий из счетчика импульсов 10, является кодом текущего времени. Он формируется счетчиком импульсов 10 в результате накопления 35 импульсов, которые поступают через элемент И 35 от генератора импульсов 55. Эти импульсы имеют частоту следования, пропорциональную единице времени (например, с, мин ч и т.д.). В случае, когда реальное время работы исполнительного механизм больше или равно заданному ему времени, то схема сравнения 26 выдаст на своих выходах сигналы. Эти сигналы через элементы ИЛИ будут поступать на вход элемента И 37. При этом - совпадение значений bi и Pi разрешает прохождение этих сигналов через элемент И 37 на входы элементов И 18. Этот сигнал пройдет только через этот элемент И 18, который выберет дешифратор кода 46. Такой элемент И 18 соответствует исполнительному механизму, номер которого в данный момент присутствует на адресном входе блока памяти 5 и входе дешифратора кода 46.

Сигнал с выхода элемента И 18i поступает на соответствующий триггер 53 и устанавливает его в нулевое состояние, что в свою очередь снимет сигнал с соответствующего полюса 59i и 1-й исполнительный механизм, соединенный с этим полюсом, прекратит работу.

Второй этап завершится в тот момент, когда на выходе многовходового элемента ИЛИ 41 исчезнет сигнал, Это случится тогда, когда все триггеры 53i-53n установятся в нулевое состояние, что свидетельствует о завершении работы всеми исполнительными механизмами по заданной программе. В результате на выходе элемента НЕ 45 появится сигнал, который поступит на нулевой вход триггера 52 и установит его в нулевое состояние.

Нулевое состояние триггера 53 снимет разрешение с элементов И 34, 35,36 и выдаст разрешение на элемент И 29, после чего устройство опять перейдет к выполнению первого этапа так, как было описано ранее. Отличие будет только в том, что на адресный вход блока памяти 1 через группу элементов И 12 и ИЛИ 24 с выхода регистра 8 поступит номер вершины, в которую входят смежные ветви. Это обеспечивается тем, что триггер 49 находится в нулевом состоянии и нет разрешения на вход группы элементов И 13. Разрешение на вход группы элементов И 12 поступает с единичного выхода триггера 50.

Описанные выше этапы будут циклически повторяться до тех пор, пока номер вершины, записанной в регистре 7 не совпадет с номером вершины, в которую входят смежные ветви и который поступает с выхода регистра 8. Сравнение производится следующим образом. Номер конечной вершины мультиграфа с выхода регистра 7 поступает на схему сравнения 25, куда с выхода регистра 8 через группу элементов И 12 и ИЛИ 24 поступает номер вершины, в которую входят смежные ветви. В случае совпадения номеров, схема сравнения кодов 25 выдает сигнал на входе элемента И 28. На второй вход элемента И 28 в этот момент поступает метка с выхода регистра 8. В результате, на выходе элемента И 28 появится сигнал, который поступит на нулевой вход триггера 48 и установит его в нулевое состояние. Это свидетельствует об окончании решения задачи формирования

последовательности команд, которые представляют сетевую структуру для управления исполнительными механизмами.

Введение в устройство новой группы элементов И, коммутатора, двух элементов ИЛИ, трех элементов И и схемы сравнения, включенных по соответствующей схеме, выгодно отличает его от ранее известных устройств тем, что позволяет по заданной технологической программе не только выбирать приводы, которые работают в каждый момент одновременно, формировать команды для их запуска, следить за продолжительностью работы приводов, но и осуществлять контроль за величиной управляющего сигнала исполнительного механизма.

Формула изобретения Устройство программного управления, содержащее первый и второй блоки памяти последовательности техпроцесса, третий, четвертый и пятый блоки памяти параметров техпроцесса, с первого по четвертый регистры, первый и второй счетчики импульсов, с первой по девятую группы элементов И, первую, вторую и третью группы элементов ИЛИ. первую и вторую схемы сравнения, с первого по девятый элементы И, первый и второй элементы ИЛИ, первый и второй элементы НЕ. дешифратор кода, кольцевой регистр - с первого по пятый триггеры, первую и вторую группы триггеров и блок синхронизации, причем информационные входы первого и второго регистров соответственно являются первым и вторым входами условий устройства, выходы второго регистра соединены с первой группой входов первой схемы сравнения, с первого по (п-1)-й (где п - число элементов в перечисленных группах устройства) выходы третьегб регистра соединены с первыми входами элементов И первой группы, информационный вход третьего регистра соединен с выходом второго блока памяти последовательности техпроцесса, адресный вход которого соединен с выходом четвертого регистра и с адресными входами третьего и четвертого блоков памяти параметров техпроцесса, п-1 информационных входов четвертого регистра соединены с выходами элементов ИЛИ первой группы, а адресные входы пятого блока памяти параметров техпроцесса соединены с выходами элементов ИЛИ второй группы причем информационные выходы первого регистра соединены с первыми входами элементов И второй группы вторые входы которых соединены с прямым выходом второго триггера, а выходы элементов И второй группы - с первыми входами элементов ИЛИ третьей

группы, вторые входы которых соединены с выходами элементов И первой группы, вторые входы которых соединены с первым входом шестого элемента И, с прямым-вхо- дом третьего триггера, с первым входом четвертого элемента И и с первыми входами элементов И четвертой группы, вторые входы которых соединены с выходами первого блока памяти последовательности техпро- 0 цесса, а выходы элементов И четвертой группы - с первыми входами элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов И третьей группы, первые входы которых соединены с 5 первыми входами элементов И первой группы, а вторые входы - с выходом первого элемента НЕ, вход которого соединен с п-м выходом третьего регистра, с первым входом первого элемента И, с входом установки 0 в О четвертого триггера и с входом установки в 1 пятого триггера, второй вход первого элемента И соединен с выходом первой схемы сравнения, вторая группа входов которой соединена с выходами эле- 5 ментов ИЛИ третьей группы и с адресными входами первого блока памяти последовательности техпроцесса, вход разрешения считывания которого соединен с выходом шестого элемента И и с первым входом пер- 0 вого элемента ИЛИ, причем счетный вход первого счетчика импульсов соединен с выходом восьмого элемента И, а выходы - с первой группой выходов второй схемы сравнения, вторая группа входов которой соеди- 5 нена с первой группой выходов пятого блока памяти параметров техпроцесса, информационный вход которого соединен с выходом третьего блока памяти, вход разрешения считывания которого соединен с вхо- 0 дами разрешения считывания четвертого и входом разрешения записи пятого блоков памяти параметров техпроцесса, с первыми входами элементов И пятой группы и с первым выходом кольцевого регистра, а вторые 5 входы элементов И пятой группы соединены с первыми входами элементов И шестой и седьмой групп и с выходом дешифратора кода, информационные входы которого соединены с выходами элементов ИЛИ второй 0 группы первые входы которых соединены с выходами второго счетчика импульсов, счетный вход которого соединен с выходом седьмого элемента И, входы элементов ИЛИ второй группы соединены с п-1 выходами 5 третьего блока памяти параметров техпроцесса,выходы элементов И шестой группы соединены с входами установки в 1 триггеров второй группы, прямые выходы которых соединены с первыми входами элементов И восьмой группы, вторые входы

которых соединены с первыми входами элементов И девятой группы и с прямыми выходами триггеров первой группы, с входами второго .элемента ИЛИ, выход которого соединен с входом второго элемента НЕ, выход которого соединен с входом установки в Ort пятого триггера, а входы установки в 1 триггеров первой группы соединены с выходами элементов И пятой группы, входы установки в О триггеров первой группы соединены с выходами элементов И седьмой группы, а инверсные выходы триггеров второй группы соединены с вторыми входами элементов И девятой группы, третьи входы которых соединены с третьими входами элементов И восьмой группы, с Нервыми входами седьмого, восьмого и девятого элементов И и прямым выходом пятого триггера, прямой выход первого триггера соединен с первым входом второго элемен- та И, выход которого соединен с прямым входом третьего триггера, входы установки в О второго и третьего триггеров соединены с выходом третьего элемента И, первый вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом пятого и вто- рыми входами седьмого и второго элементов И, третий выход блока синхронизации соединен с вторыми входами четвер- того и девятого элементов И, выход последнего из которых соединен с входом разрешения считывания пятого блока памяти параметров техпроцесса, четвертый и пя- тый выходы блока синхронизации соединены соответственно с вторыми входами восьмого и шестого элементов И, вторые входы третьего и пятого элементов И соединены с прямым выходом четвертого триггера, вход установки в 1 которого со- единен с выходом четвертого элемента 1Л, инверсный выход четвертого триггера соединен с третьим входом второго элемента И, четвертый вход которого соединен с инверсным выходом пятого триггера, выход пято- го элемента И соединен с информационным входом кольцевого регистра, третий1 выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом разрешения записи четвертого ре- гистра, второй выход кольцевого регистра соединен с входом разрешения записи третьего регистра и входом разрешения считывания второго блока памяти последовательности техпроцесса, выход элемента И соединен с входом установки в О первого

триггера, вход установки в 1 которого соединен с входом установки в 1 второго триггера и является входом пуска устройства, первыми и вторыми выходами кода операций которого являются соответственно выходы элементов И восьмой и девятой групп, причем первый и второй выходы син- хронизации соответственно соединены с вторым входом третьего элемента И с вторыми входами пятого, седьмого и второго элементов И, отличающееся тем, что, с целью повышения надежности за счёт контроля выполнения последовательности команд, которые представляют сетевую структуру управления исполнительными механизмами и no ebiffiettHHTt Hoc TH выполняемого технологического процесса, в устройство программного управления введены коммутатор, десятая труп па элементов И, третий и четвертый элементы ИЛИ, десятый, одиннадцатый и двенадцатый элементы И и третья схема сравнения, первый выход которой соединен с первым входом двенадцатого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход и выход которого соединены соответственно )-м информационным выходом четвертого блока памяти параметров техпроцесса и с вторыми входами элементов И шестой группы, а второй выход третьей схемы сравнения соединен с первым входом десятого элемента И, втдрой вход и выход которого соединены соответственно с выходом тр етьего элемента ИЛИ, первый и второй входы которого соединены соответственно с гтервым и вторым выходами второй схемы сравнения и с вторыми входами элементов И седьмой груп пы, а третий вход десятого эл емента И соединен с первым входом одиннадцатого элемента И, вторым входом двенадцатого элемента И и прямым выходом пятого триггера, выход одиннадцатого элемента И соединен с первыми входами элементов И десятой группы, выходы которых соединены с входами установки в О триггеров второй группы а вторые входы элементов И десятой группы соединены соответственно с выходами дешифратора кода, причем первая группа входов третьей схемы сравнения соединена с второй группой выходов пятого блока памяти параметров техпроцесса, вторая группа входов третьей схемы сравнения соединена с выходом коммутатора, входы которого являются входом изменяющихся условий управляющего сигнала устройства.

SI,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство программного управления | 1987 |

|

SU1418710A1 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1242980A1 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для распаковки команд | 1987 |

|

SU1464157A1 |

Изобретение относится к цифровым вычислительным машинам для программного управления и может быть использовано при построении специализированных вычислительных устройств для осуществления формирования последовательности применительно к приводам станков с программным управлением. Устройство программного управления позволяет решать задачи формирования последовательности команд, которые представляют сетевую структуру, для управления приводами станка с программным управлением, для осуществления контроля за величиной управляющего сигнала исполнительного механизма. Кроме того, устройство позволяет моделировать структуру сети типа мультигрэф 1 ил. ел с

| Устройство для решения задачи поиска длиннейшего пути | 1983 |

|

SU1206791A1 |

| Устройство программного управления | 1987 |

|

SU1418710A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Кофман А | |||

| Введение в прикладную комбинаторику | |||

| -М.: Наука, 1975. | |||

Авторы

Даты

1992-12-15—Публикация

1991-01-02—Подача