19

О)

tl ел

kj

Изобретение относится к вычислительной технике и может быть использовано для распаковки командной информации в процессоре быстродейству- ющей ЭВМ, в частности в процессоре, допускающем параллельное исполнение нескольких последовательно расположенных команд.

Цель изобретения - повышение быст родействия за счет одновременной распаковки нескольких команд.

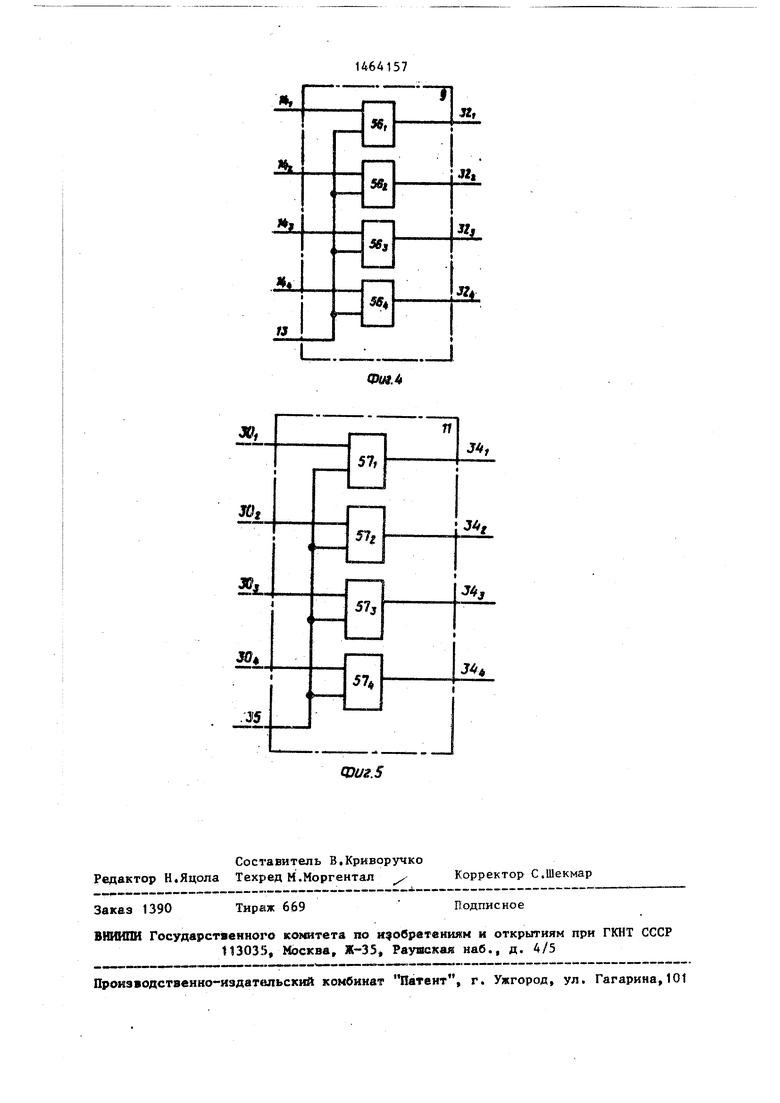

На фиг.1 представлена структурная схема устройства для распаковки команд (все функциональные схемы бло- ков для разрядности информационной шины памяти, равной двойному слову, т.е. четырем полусловам)t на фиг.2 - функциональная схема блока указателей начала выборки; на фиг.З - функ- циональная схема блока мультиплексоров (для одного бита из каждого полуслова) ; на фиг.4 - функциональная схема группы элементов ИЛИ; на фиг.З - функциональная схема группы элементов И.

Устройство для распаковки команд (фиг,1) содержит перзьй 1, второй 2 и третий 3 буферные регистры команд, регистр 4 признаков команд, блок 5 указателей начала выборки, блок 6 ла мя ги, блок 7 мультиплексоров, элемент И 8, группу 9 элементов ЮШ, D-триггер 10, группу 11 элементов И, вход 12 старших разрядов кода команд устройства, вход 13 сброса устройст- -ва, вход 14 номеров команд устройств (сигналы приема команд в обрабатывающие устройства процессора), вход 15 разрешения приема команд устройст ва, вход 16 синхронизации устройства вход 17 младших разрядов кода команд устройства, вход 18 резкима распаковки устройства р выход 19 кода номера команды устройства, выход 20 распа-о ковки команд устройства, выход 21 блока 5, выходы 22 и 23 блока 3, выходы 24-26 блока 2, выход 27 элементов И 8, выходы 28-30 блока 6 памяти выход 31 блока 7, вькод 32 блока 9, выход 33 .блока 4, выход 34 блока 11 и выход 35 D-триггера 10,

Блок 5 указателей начала выборки (фиг.2) содержит регистр 36, шифра- тор 37, реализованный на группе 38 элементов И, содержащей с первого по седьмой элементы И 39-45„ и элементе ИЛИ 46. Блок 7 мультиплексоров (фиг.З) содержит элементы И-ИЛИ 47-

о

5 0 5

0 п -

5

52 и элементы И 53-55. Группа 9 элементов ИЛИ (фиг.4) содержит элементы ИЛИ 56.1-56.4. Группа 11 элементов И (фиг.5) содержит элементы И 57.1 57.4.

В описании работы устройства использованы следующие обозначения: RR - формат команд длиной в одно полуслово; RX, RS, SI, S и RRE - формат команд длиной в два полуслова; SS, SSE - формат команд длиной в три полуслова .

Команды в памяти должны располагаться на границе полуслова (или четного байта), поэтому при обращении в память за командами значение младшего (31-го) разряда адреса команды всегда равно нулю, и в дальнейшем этот разряд не рассматривается. В начало новой ветви программы (после успешного перехода, смены состояния процессора, или первоначальной загрузки программы) 30, 29, ..., 30-й разряды адреса указывают номер полуслова, с которого начинается первая команда новой ветви программы,

Два старших разряда к аждой команды (0-й и 1-й) определяют ее формат. Так, если в 0-м и 1-м разрядах ко-. манды содержится код 00, то команда состоит из одного полуслова, при кодах 01 .или 10 - из двух полуслов, при коде 11 - из трех полуслов.

При разрядности информационной шины памяти, равной п полусловам, на ней могут содержаться от п/3 до п команд, при этом в младшем полуслове или в младших двух полусловах (а в начале ветви программы - когда адрес указывает на эти полуслова) могут содержаться не полные команды, а только начало следующей команды, а продолжение данной команды поступает при новом чтении из памяти,

Распаковка команд организована таким образом, что из командной ин- формащ-1и, принятой во второй буферньй регистр 2 команд, в первый буферный регистр 1 команд всегда заносятся только все полные команды, независимо от их форматов, а младшие два полуслова зан.осятся в третий буферный .регистр 3 команд. Они будут участво- i вать в распаковке следующего блока информации, принятого из памяти (при наличии в предьщущем блоке неполной команды, т.е. остатка). Первый буфер- ньш регистр 1 команд содержит Зп-3

полуслов (где п - разрядность информационной шины памяти в полусловах), которые распределены по командам следующим образом; первые п - 2 команды содержат по три полуслова, п - 1-я команда содержит два полуслова, а .п-я команда - одно полуслово. При этом независимо от формата команды -i на место первых п - 2 команд записываются по три, а на место п - 1-й кома1щы - два последовательно расположенных полуслова, Однако в обрабатывающих устройствах используется лишь число битов, определяемое кодом операции, который всегда записывается на место старшего байта старшего полуслова. Второй буферный регистр 2 команд содержит п полуслов и соответствует разрядности информационной шины памяти. Третий буферный регистр 3 команд содержит два полуслова и соответствует максимально возможному остатку в предьдущей распаковке.

Блок 5 указателей начала выборки вырабатывает признаки, указывающие с какого полуслова начинается командная информация в данном такте работы устройства. Если в предьщущем такте поступил признак начала ветви, тогда командная информация может начинаться с 1 , 2,,..,п-го полуслова из второго буферного регистра 2 команд в соответствии с значением младших разрядов адреса полуслова. Если в предьщущем такте не поступил признак начала ветви, тогда командная информация может начинаться с первого или второго полуслова третьего буферного регистра 3 команд (регистра остатка) или с первого полуслова второго буферного регистра 2 команд в соответствии с выработанным в предьщущем такте в блоке 6 памяти кодом адреса

Признаки, вырабатываемые блоком 5 указателей начала выборки, а также старшие два бита от каждого полуслова из третьего 3 и второго 2 буферны регистров команд (выходы 22 и 24) поступают в блок 6 памяти, представляющий собой программируемую логическую матрицу и вырабатывающий три группы управляющих сигналов.

Группа управляющих сигналов,поступающая с выхода 29 в блок 7 мультиплексоров, указывает с какого полуслова начинается каждая команда и управляет занесением информационны полуслов из буферных регистров 2 и 3

0

5

0

5

0

5

0

5

0

5

команд в соответствуюп5ие комавдные полуслова буферного регистра 1 команд. Код адреса представляет собой признаки остатка и поступает с выхода 28 в блок 5 указателей начала выборки. Группа управляющих сигналов, поступающая с выхода 30, указывает на наличие 1,2,,,,, п-й команд в данном блоке koмaнднoй информации и служит в качестве информационных входов для триггеров регистра 4 номеров команд при наличии высокого уровня на первом входе группы элементов И (вьрсод 35 D-триггера 10),

Работу устройства рассмотрим на примере выборки командной информации при обработке некоторой последовательности команд.

Предположим, что разрядность информационной шины памяти равняется четырем полусловам (64 бита), тогда первьш буферный регистр 1 команд должен содержать девять полуслов (по три полуслова для первой и второй команд, два полуслова для третьей команды и одно полуслово для четвертой команды), регистр 4 номеров команд должен содержать четыре триггера, группа 9 элементов HTOd должна состоять из четырех элементов ИЛИ, группа 11 элементов И должна состоять из четырех элементов И, элемент И 8 должен быть шестивходовым, а на вход 17 блока 5 должны поступить 30-й и 29-й разряды адреса. Пусть обрабатывается новая ветвь программы, содержащая команды форматов RR, RX, SS, RS, RR, SS, RR, RR, RR, ,,., причем 29-й и 30-й разряды находятся соответственно в состоянии О и 1, Расположение командной информации представлено в таблице, I

Сразу после определения необходимости перехода на новую ветвь программы обрабатывающие устройства процессора вырабатывают сигнал Сброс, по которому D-триггер 10 наличия действительной информации в буферных регистрах 2 и 3 команд устанавливается в состояние О, одновременно в регистре 4 сбрасывают- мя все признаки наличия предварительно распакованных команд. Тем самым на элементе И 8 подготавливается формирование разрешающего импульса на выходе 27 для приема блока командной информации новой ветви программы в буферный регистр 2, а нулевое состояние выхода 35 В-триггер.а 10 запрещает передачу в регистр 4 номеров распакованных команд через группу 11 элементов И,

Первое двойное слово командной информации новой ветви поступает на информационный вход буферного регистра 2 команд и сопровоясдается единичным состоянием входов 18 и 15, .а также кодом 01 на входах 17, и Г/ (фиг.2).

По тактовому импульсу 16 на выходе элемента И 8 формируется разрешающий импульс, по которому первое двойное слово командной информации записывается в буферный регистр 2 команд предыдущее значение двух младших полуслов с выхода 26 записывается в буферный регистр 3 команд, D-триг- гер 10 устанавливается в состояние 1 (фиг.О, В регистре 4 номеров команд информация остается без изменения (все триггеры в состоянии О) так как предьщущий нулевой уровень на выходе 35 В триггера 10 формирует нулевые уровни на информационных входах 34 всех триггеров регистра 4 (через группу 11 элементов И),

На выходах блоков 5, 3 и 2 формируются входные сигналы для блока 6 памяти, а на выходах блока 6 фор1чи- руются активные линии в соответствии с таблицей кодирования. В соответствии с входными воздействиями на элементы И 39-45 и элемент ИЛИ 46 (фиг.2) .на выходе 21.4 блока 5 указателей начала вь бор:кн сигнал становится активным. Это означает, что коды старших двух битов первого и второго полуслов из регистра 3, а также старших двух битов первого полуслова из регистра 2 игнорируются (командная информация начинается со второго полуслова . в ре:гистре 2). Первой команде формата RR и второй команде формата RX соответствуют коды 00 на выходах 24 Я 24;) и коды 01 на вькодах 24j- и 24. На выходе блока 6 памяти будут активны выходы:

28, (остаток равен нулю), 29, 29 (вторая команда начина тся с второго полуслова, третья команда - с третьего полуслова регистра 2) и 30,

30j (признаки наличия: второй и третьей команд). Сигкалы с выходов 29 и 29 поступают в блок 7 мультиплексоров (фиг.З). Сигнал с выхода 294 разрешает передачу второго,третьего и четвертого полуслов регистра 2 (выходы 25j, 26f и 262) соответственно на место первого, второго и третьего полуслов второй команды (выходы

31

f

31,

5

0

5

0

5

0

5

ij., 31, блока 7 мультиплексоров) , активный выход 29 разрешает передачу третьего и четвертого полуслов регистра 2 (линия 26 и 26g), соответственно на,место первого и второго полуслов третьей команды (выходы 31. и 31g блока 7 мультиплексора) ,

По следующему тактовому импульсу, при наличии единичного уровня . на входе 1-5 устройства, информация, подготовленная на выходе 31 блока 7 мультиплексоров (первые две команды), записывается в буферный регистр 1 команд, номера команд, подготовленные на выходе 30 блока 6 памяти через группу 11 элементов И записываются в регистр 4 (так как передача разрешается единичным состоянием выхода 35 D-триггера 10, которьй установится в состояние О только после прихода, следующего сигнала Сброс и в дальнейшем будем считать, что передача номеров команд через группу элементов И разрешается), второе двойное слово командной информации записывается в буферный регистр 2 команд, а значение младших двух полуслов первого двойного слова из буферного регистра 2 команд запомина;- ется в буферном регистре 3 кома1-щ, В соответствии с входными воздействиями на элементь И.39-45 и элемент ИЛИ 46 (фиг. 2) на сигнал выходе 21 , 1 блока 5 становится активным (командная информация начинается с первого полуслова в регистре 2),

Третьей команде формата SS и четвертой команде формата RS соответствуют коды 11 на выходах 24,

24,

и 10 на выходах 24 и 24g , На выходе блока 6 будут активны выходы:28 (остаток равен одному полуслову),

50 3 (первая команда начинается с первого полуслова регистра 2), 30 (признак наличия первой команды). Активный сигнал с выхода 29,j посту- .пает в блок 7 мультиплексоров

сг (фиг.З) и разрешает передачу первоЭ

го, второго и третьего полуслов регистра 2 (выходы 25, 5 25 и 25 на фиг.З), соответственно на место пер- його, второго и третьего полуслов

первой команды (выходы 31. , 31, и 31 блока 7 мультиплексоров).

Таким образом, в данный момент на выходе 20 устройства находятся первая (формата RR) и вторая (формата RX) команды на месте второй и третьей команд буферного регистра 1 соответственно, а на выходе 19 устройства номера второй и третьей команд. В то же время на информационных входах буферного регистра 1 и регистра 4 номеров команд подготовлена информация для следующей команды формата SS. После приема первой и второй команд обрабатывающими уст- poйcтвa и (в зависимости от конкретной реализации процессора это может произойти либо в одном, либо в двух разных тактах), сообщается признака- 1«ш приема на входах 14,2 и 14,3 номеров команд устройства, которые через элементы ИЛИ 56 и 56 (фиг,4) сбрасывают соответствующие триггеры регистра 4 номеров команд. Инверсные выходы 33 триггеров регистра 4 подготавливают на элементе И 8 прием следующего двойного слова командной информации.

По аналогии с изложенным и при выполнении соответствующих условий по следующему TaxroBONry импульсу в буферный регистр 1 записывается третья распакованная команда формата SS на место первой команды, в регистр 4 - номер первой команды, в регистр 2 - третье двойное слово командной информации, в регистр 3 - третье и четвертое полуслова второго двойного слова командной информащи,

Так как четвертая команда формата RS занимает младшее полуслово второг двойного слова и старшее полуслово третьего двойного слова, она не участвовала в предыдущей распаковке и в обрабатывающие блоки поступила лишь третья команда формата SS, В данный момент начало четвертой команды находится во втором полуслове буферного регистра 3, В соответствии с входными воздействиями на элементы И 39-45 и элемент ИЛИ 46 (фиг,2) сигнал на выходе 21,2 блока 5 становится активным (командная информация начинается с второго полуслова в ре- гиСтре 3), Четвертой команде формата RS, пятой команде формата RR соответствуют коды 10 на вьсходах 22з и 22, коды 00 на линиях 24з и 24 .

и коды 11 на выходах 24j. и 24, На , выходе блока 6 будут активны выходы: 282 (остаток равен двум полусловам),

29,

2,

29 (первая команда начинается с второго полуслова регистра 3, вторая команда начинается с второго полуслова регистра 2), 30,, ЗО. (признаки наличия первой и второй ко

манд), Активные сигналы выходов 29, и 294 поступают в блок 7 мультиплексоров (фиг,3) и разрешают передачу второго полуслова регистра 3 (линия 232 первого и второго полуслова

регистра 2 (линии 25, и 25) соответственно на место первого, второго и третьего полуслов первой команды (выходы 31, 31 и 31j блока 7 мультиплексоров) .

После приема третьей команды формата SS обрабатывающиьм блоками процессора и при выполнении соответствующих условий по следующему тактовому импульсу в регистр 1 записываются четвертая команда формата RS на место первой команды и пятая команда формата RR на место второй ко- ма11ды, в регистр 4 - номера первой и второй команд, в регистр 2 - чет-

вертое двойное слово командной инфор- Main-iH, в регистр 3 - третье и четвертое полуслова третьего двойного слова командной информации.

Шестая команда формата SS занима- ет младаме два полуслова третьего двойного слова и старшее полуслово четвертого двойного слова. На это указывает код 001, записанный в ре- гистр 36, и код 11 на линиях 22 и 22, На седьмую, восьмую и девятую команды форматов RR указывают коды

5

0

5

00 00 00 на линиях 24,, 24., 24

3

t.

.

24, 24 и 24g. Перечисленные коды,

а также активный сигнал 21, выра бо- танный блоком 5 в соответствии с записанной в регистре 36 информаисией, поступают в блок 6 памяти. На выходе блока 6 будут активны выходы 28

29, , 29,

29

Г

(остаток равен нулвр) , у , ц , 29 (первая команда начинается с первого полуслова регистра 3, вторая команда - с второго полуслова регистра 2, третья - с третьего полуслова регистра 2 и четвертая - с четвертого полуслова регистра 2), 30, 30, ЗОз, 30 (признаки наличия первой, второй, третьей и четвертой команд) , Активные сигналы с выходов 29, 29, 297- и 29 поступают в блок

7 мультиплексоров (фиг.З) и разрешают передачу первого и второго полуслов регистра 3 (выходы 32J и 23i) и первого полуслова регистра 2 (вь ход 25j) соответственно на место первого, второго и третьег о полуслрв первой команды (выходы 31, З,

манд.

о т л и ч

10 а ю щ

е е с я тем,

что, с целью повышения быстродейст- 1 ВИЯ за счет одновременной распаковки нескольких команд, оно содержит третий буферный регистр команд, группу элементов И, группу элементов ИЛИ, D-триггер и блок указателей начала

З), второго, третьего и четвертого выборки причем вход разрешения при- полуслов регистра 2 (выходы 25 ю

ема команд устройства соединен с информационным входом D-триггера и первым входом элемента И, второй вход которого является входом синхронизации устройства, выход элемента И соединен с входами синхронизации Ф-триггера, первого, второго и третьего буферных регистров команд, блока указателей начала выборки и регистра .номеров кома1щ, вход сброса устройства соединен с входом сброса Ф-триг- гера и с первыми входами элементов ИЛИ группы, вторые входы которых сое динены с соответствующими разрядами входа номеров команд устройства, выходы элементов ИЛИ группы соединены с соответствующими входами сброса регистра номеров команд, информацион ный вход третьего буферного регистра команд соединен с вторым выходом вто рого буферного регистра команд, первый выход третьего буферного регистр комавд соединен с третьим информационным входом блока мультиплексоров, а второй выход третьего буферного регистра команд соединен с вторым адресным входом блока памяти, третий адресньш вход которого соединен с вы ходом блока указателей начала выборки, первый вход признаков которого соединен с входом мпадших разрядов кода команд устройства, вход задания режима распаковки устройства соедине с вторым входом признаков.блока указателей начала выборки, третий вход признаков которого соединен с выходом кода адреса блока памяти, прямой выход D-триггера соединен с первыми входами элементов И группы, второй выход кода микроопераций блока памят соединен с соответствующими вторыми входами элементов И группы, выходы элементов И группы соединены с соответствующими информационными входами триггеров регистра номеров команд, прямые выходы которого являются выходами кода номера команды устройства, инверсные выходы регистра номеро команд соединены с остальными входа ми элемента И.

25з и 25) соответственно на место первого, второго и третьего полуслов второй команды (выходы 31, 315- и 31); третьего и четвертого полуслов регистра 2 (выходы 25,, и 254) соответственно на место первого и второго полуслов третьей команды (выходы 31 и 31g); четвертого полуслова ре гистра 2 на место первого (и единственного) полуслова четвертой команды (выход 31д).

После приема четвертой и пятой команд в обрабатывающие блоки по следующему тактовому импульсу в буфер:м ный регистр 1 записываются шестая, седьмая, восьмая и девятая команды, в регистр 4 - номера первой, второй, третьей и четвертой команд, в регистр 2 - следующее двойное слово командной информапии, в регистр 3 - мпадшие два полуслова предыдущего двойного слова из регистра 2,

Процесс продолжается до поступления следующего импульса Q6poc, . указывающего на необходимость перехода на новую ветвь программы.

Ф

ормула изобретения

1. Устройство для распаковки команд, содержащее первьй и второй бу- регистры команд,, блок памяти, блок мультиплексоров, регистр номеров команд и И,, причем выход распакованных команд устройства соединен с выходом первого буферного регистра команд, информационный вход которого соединен с выходом блока мультиплексоров, первый и второй информационные входы которого ны соответственно с первым и вторым , выходаьш второго буферного регистра команд, третий выход которого соединен с первым адресным входом блока памяти, первый выход кода микроопераций которого соединен с управляющи входом блока мультипл1гксоров, вход старших разрядов кода команд устройства соединен с информационным входом второго буферного регистра ко

о т л и ч

10 а ю щ

е е с я тем,

что, с целью повышения быстродейст- 1 ВИЯ за счет одновременной распаковки нескольких команд, оно содержит третий буферный регистр команд, группу элементов И, группу элементов ИЛИ, D-триггер и блок указателей начала

выборки причем вход разрешения при-

5

0

5

0

5

0

5

0

55

ема команд устройства соединен с информационным входом D-триггера и первым входом элемента И, второй вход которого является входом синхронизации устройства, выход элемента И соединен с входами синхронизации Ф-триггера, первого, второго и третьего буферных регистров команд, блока указателей начала выборки и регистра .номеров кома1щ, вход сброса устройства соединен с входом сброса Ф-триг- гера и с первыми входами элементов ИЛИ группы, вторые входы которых соединены с соответствующими разрядами входа номеров команд устройства, выходы элементов ИЛИ группы соединены с соответствующими входами сброса регистра номеров команд, информационный вход третьего буферного регистра команд соединен с вторым выходом второго буферного регистра команд, первый выход третьего буферного регистра комавд соединен с третьим информационным входом блока мультиплексоров, а второй выход третьего буферного регистра команд соединен с вторым адресным входом блока памяти, третий адресньш вход которого соединен с выходом блока указателей начала выборки, первый вход признаков которого соединен с входом мпадших разрядов кода команд устройства, вход задания режима распаковки устройства соединен с вторым входом признаков.блока указателей начала выборки, третий вход признаков которого соединен с выходом кода адреса блока памяти, прямой выход D-триггера соединен с первыми входами элементов И группы, второй выход кода микроопераций блока памяти соединен с соответствующими вторыми входами элементов И группы, выходы элементов И группы соединены с соответствующими информационными входами триггеров регистра номеров команд, прямые выходы которого являются выходами кода номера команды устройства, инверсные выходы регистра номеров команд соединены с остальными входами элемента И.

Ч)иг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство выборки команд процессора | 1986 |

|

SU1410028A1 |

| Устройство для управления буфер-НОй пАМяТью | 1979 |

|

SU840903A1 |

| Микропрограммный процессор | 1978 |

|

SU744587A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

Изобретение относится к вычислительной технике и может быть использовано для распаковки командной информации в процессоре быстродействующей ЭВМ. Цель изобретения - повышение быстродействия за счет одновременной обработки нескольких команд. Устройство для распаковки содержит буферные регистры 1-3 команд, регистр 4 номеров команд, блок 5 указателей начала выборки, блок 6 памяти, блок 7 мультиплексоров, элемент И 8, группу 9 элементов ИЛИ, D-триггер 0, группу 11 элементов И. 1 з.п. ф плы, 1 табл.

Составитель В.Криворучко Редактор Н.Яцола Техред М.Моргентал Корректор С.Шекмар

Заказ 1390

Тираж 669

ВНЮШИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР tOOSI), Москва Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для буферизации команд | 1976 |

|

SU610109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-07—Публикация

1987-07-06—Подача