n7jg,

miff.

00

00

со

И:юбре1сние относится к радиоизмерн- те. 1ьной технике и может быть использовано при разработке анализаторов спектра.

Це.1ь изобретения - новышение стабиль- нск ти частоты и уменьшение времени перестройки частоты выходного сигнала.

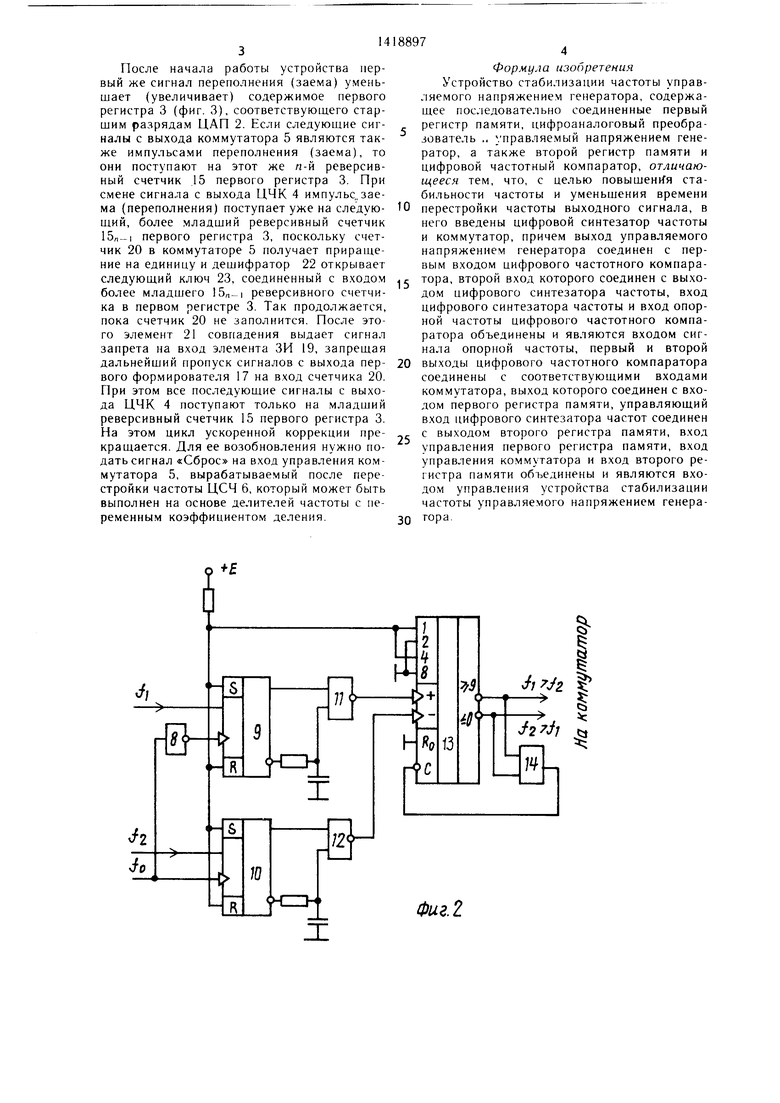

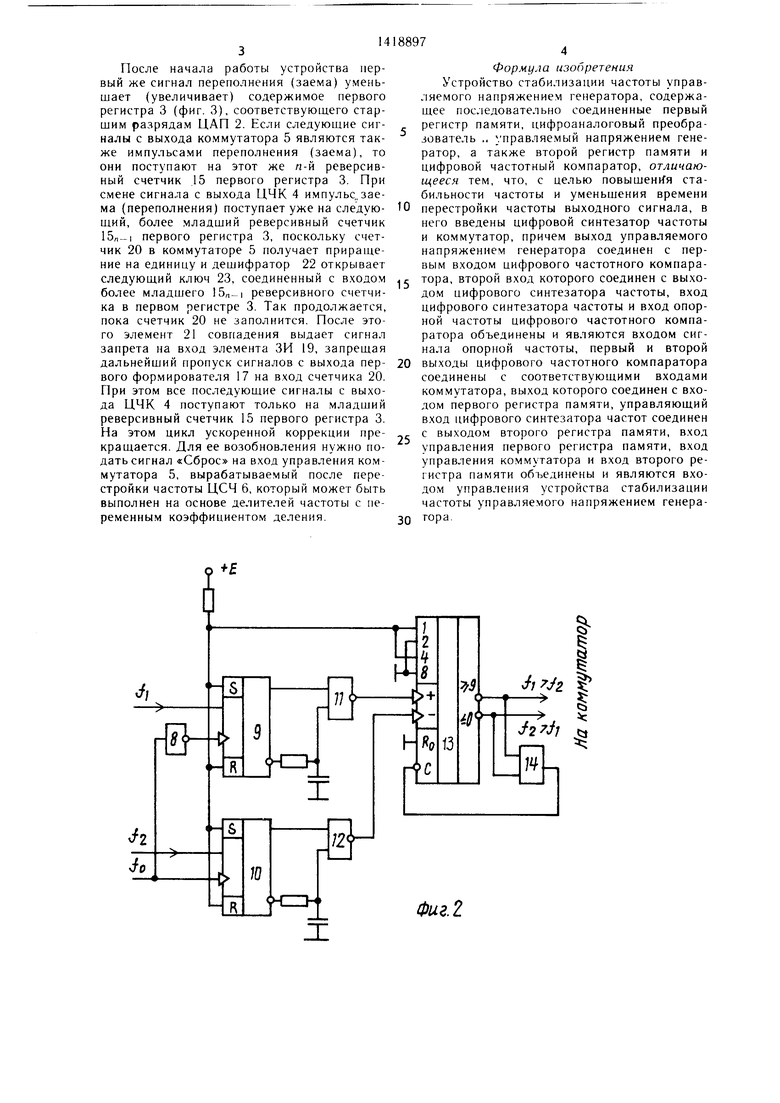

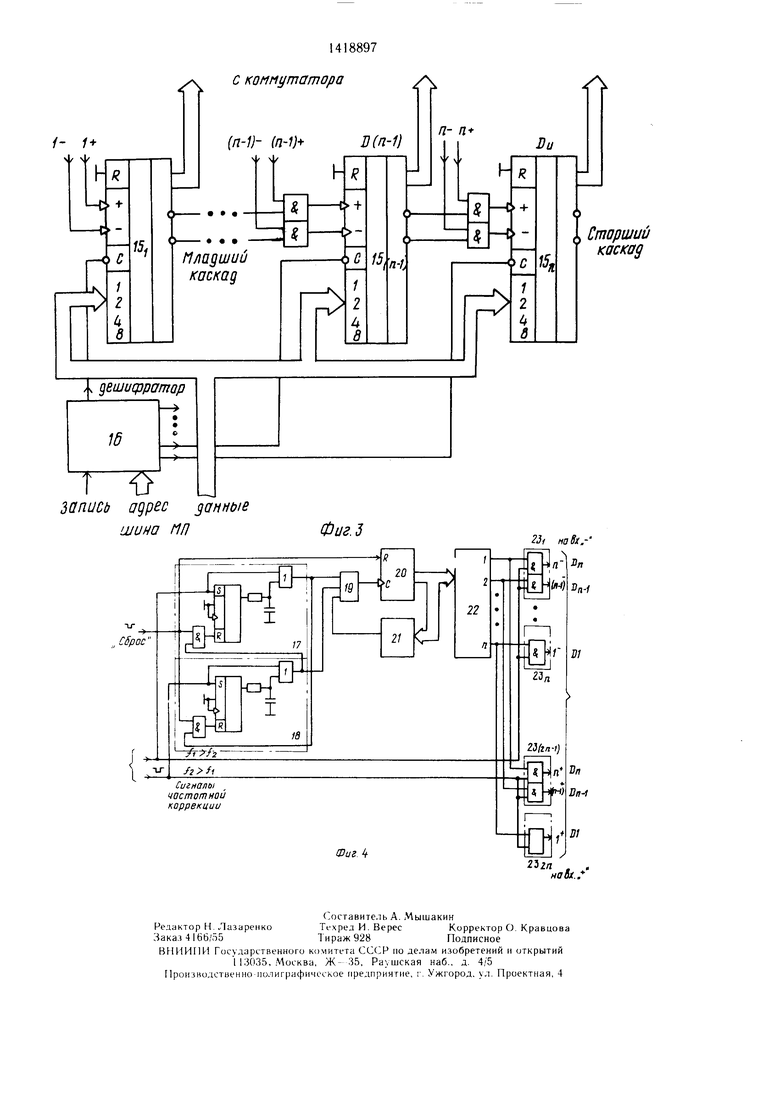

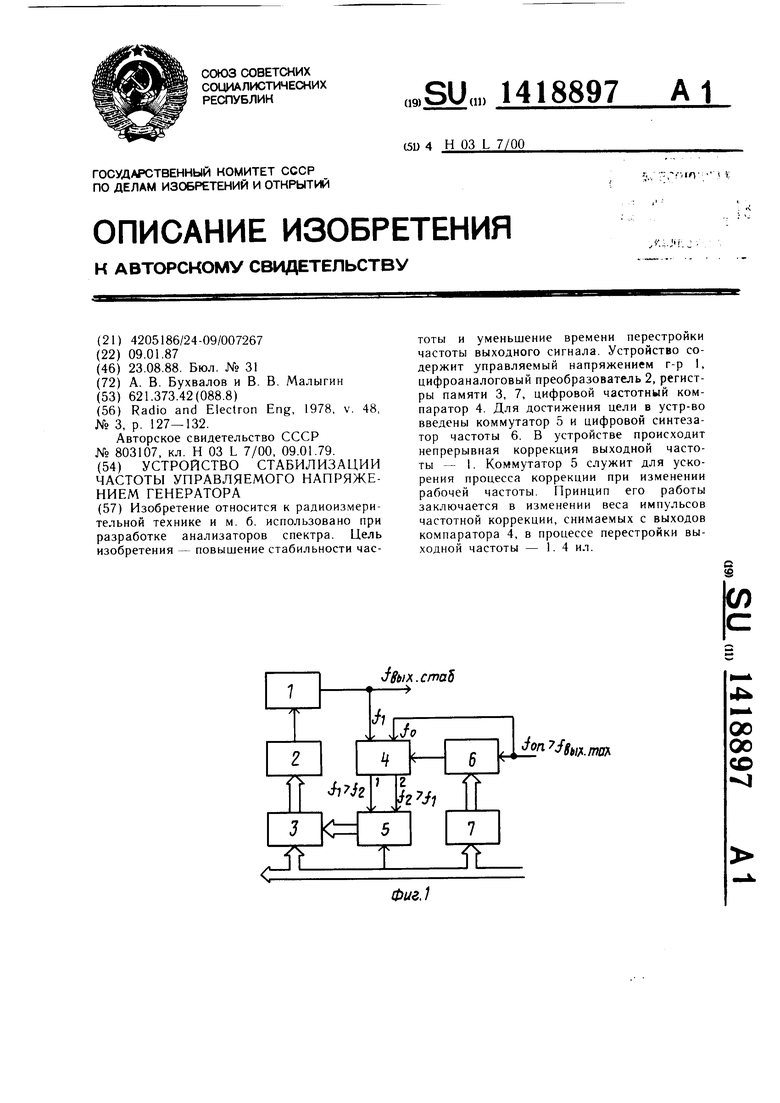

На фиг. 1 приведена структурная электрическая схема устройства стабилизации частоты управляемого напряжением генератора; па фи1. 2принципиальная схема цифрового частотного компаратора; на фиг . 3 принципиальная схема первого регистра памяти; на фи1. 4 принципиальная схема коммутатора.

Устройство стабилизации частоты управляемого напряжением генератора содержит управляемый напряжением генератор (УНГ)

1,цифроаналоговый преобразователь ( ЦАГ1)

2,первый регистр 3 памяти, цифровой частотный компаратор (ЦЧК) 4. коммутатор 5, цифровой синтезатор частоты (ЦСЧ) 6, вто )oii регистр 7 памяти.

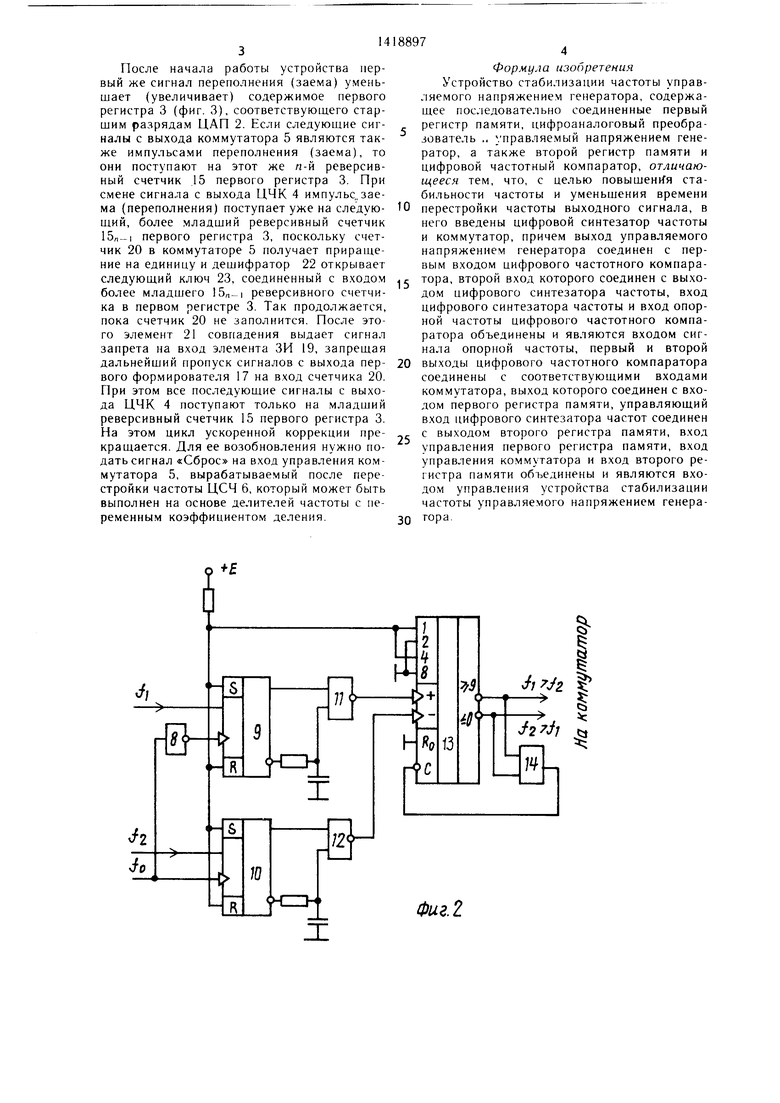

Цифровой частотный компаратор (ЦСЧ) 4 (фиг. 2) содержит инвертор 8, первый и второй О-триггеры 9 и 10, первый 11 и второй 12 элементы 2И-НЕ, реверсивный счетчик 13, элементы И 14.

Первый ре1 истр 5 памяти (фиг. 3) содержит первый, второй, ..., п-А реверсивные счетчики 1Г)1 1Г)/;, дешифратор 16.

Коммугато) 5 (фиг. 4) содержит первый 17 и вг()Н)11 18 фо)мирователи импульсов, э.юмепг 311 19, счегчик 20, э,;|емен1 21 совпадения, Д1 ппи|) 22, первый, второй

2 (и ключи 231 23.,.

Уст{)ОЙсги() работает с, 1едую1цим образом.

Ишепение частоты выходного сигнала проис.ходи путем записи нового кода в пе)вы11 peinciji i5 и нового значения кода частот Ц( Ч () во второй регистр 7. 1ДАГ1 2, пре :1П 1азуя цифровой код в аналогч)вЫ11, осуществляет непосредственное управление УНГ I. . Ья ика работы ЦЧК 4, осуществляю- пнмо сравнение вьгчодной частоты УНГ 1, /1 иосгупаклпей па первьп вход ЦЧК 4, с г(ых.)Д|;ой частотой ЦСЧ 6 /j, поступающей на его второй в.ход, след ю|цая. При раве)1- сгве часгог /i и /j на первом и втором выхо- U1X ЦЧК 4 присутствует логическая единица. При не)авенстве часгог с выхода, LO- ()тветствукчце1 о бо, 1ьп1ей частоте, снимается пос;1едовате.1ьность импульсов с частот(Л1, 1;1)1)порпиопа/1ьной разности частот сравни- ваемь сигналов, па друг ом выходе при этом будет единица. Выходные сигналы ЦЧК, 4 )т 4epe:i коммутатор 5 на вход пер- Boi o lei истра .. Так, при импульсы с первого пыхода ЦЧК 4 уменьшают зпаче- ние кода, ранее занесенного в ре- 131стр 3. при /./, импульсы с второю выхода ЦЧК 4 уве.тичивают значение кода, ранее занесенною в первый регистр 3. Причем, кажды(( импульс с выхода ЦЧК 4 уве.личиваег и,аи умепьпшет содержимое

первого регистра 3 на единицу младшего разряда. Таким образом происходит непрерывная коррекция выходной частоты УНГ 1.

-Формирователи, состоящие из первого и

второго D-триггеров 9 и 10, RC-цепочки и первого 11 и второго 12 элементов 2 И-НЕ, на один из которых подается сигнал с выхода УНГ 1, на другой - с выхода ЦСЧ 6, формируют по их переднему фронту короткие

0 не совпадающие по фазе импульсы, которые поступают на входы суммирования или вычитания реверсивного счетчика 13, При равенстве частот значение реверсивного счетчика 13 не меняется и на выходах заема и

переполнения присутствуют единицы. При неравенстве частот значение реверсивного счетчика 13 смец ается в ту или иную сторону, так при снимаются импульсы с выхода переполнения, а при - с выхода заема. Диапазон счета реверсивного счет0 чика 13 от своего среднего значения до минимального или максимального образует зазор, демпфирующий кратковременные флуктуации сравниваемых частот /: и /2, Таким образом частота импульсов на выходе заема или переполнения прямопропорцио5

0

5

5

пальна разности частот /i и /2Коммутатор 5 (фиг. 4) служит для ускорения процесса коррекции выходной частоты УНГ 1 при изменении рабочей частоты Црипцип его работы заключается в изменении веса импульсов частотной коррекции, снимаемых с выходов ЦЧК 4, в процессе перестройки выходной частоты УНГ 1. Первый 17 и второй 18 формирователи вырабатывают короткие импульсы по переднему фропту сигналов переполнения или заема, поступающих на соответствующие входы коммутатора с ЦЧК 4. Цричем первый 17 и второй 18 формирователи, воспринимая каждый из поступающих на них сигналов, вырабатывают импульсы по первым из серий

0 сигналов переполнения или заема. Таким образом, первый формирователь 17 вырабатывает импульсы только от первого сигнала переполнения после начала работы устройст- ja по сигналу «Сброс, поступающего на вход управления коммутатора 5, а также от первого сигнала переполнения, следующего сразу же за сигналом заема. Аналоги но работает и второй формирователь 18. Импульсы с выхода первого 17 и второго 18 формирователей через элемент ЗИ 19 посту пают па вход счетчика 20, имеющего разрядность, равную разрядности ЦАП 2, Результат счета является адресом разряда первого регистра 3, куда подаются в текущий момент времени сигналы с выхода ЦЧК 4, Это достигается дешифрацией выходных сиг5 палов счетчика 20. Выходы дешифратора 22 ком.мутируют сигналы заема и переполнения, поступающие с выхода ЦЧК 4 на вход пер- ВО1Ю регистра 3.

14

После начала работы устройства первый же сигнал переполнения (заема) уменьшает (увеличивает) содержимое первого регистра 3 (фиг. 3), соответствующего старшим разрядам ЦАП 2. Если следующие сигналы с выхода коммутатора 5 являются также импульсами переполнения (заема), то они поступают на этот же л-й реверсивный счетчик 15 первого регистра 3. При смене сигнала с выхода ЦЧК 4 импульс,, заема (переполнения) поступает уже на следующий, более младший реверсивный счетчик первого регистра 3, поскольку счетчик 20 в коммутаторе 5 получает приращение на единицу и дешифратор 22 открывает следующий ключ 23, соединенный с входом более младшего 5„-| реверсивного счетчика в первом регистре 3. Так продолжается, пока счетчик 20 не заполнится. После этого элемент 21 совпадения выдает сигнал запрета на вход элемента ЗИ 19, запрещая дальнейший пропуск сигналов с выхода первого формирователя 17 на вход счетчика 20. При этом все последующие сигналы с выхода ЦЧК 4 поступают только на младший реверсивный счетчик 15 первого регистра 3. На этом цикл ускоренной коррекции прекращается. Для ее возобновления нужно подать сигнал «Сброс на вход управления коммутатора 5, вырабатываемый после перестройки частоты ЦСЧ 6, который может быть выполнен на основе делителей частоты с переменным коэффициентом деления.

0

о

5

0

5

Формула изобретения Устройство стабилизации частоты управляемого напряжением генератора, содержащее последовательно соединенные первый регистр памяти, цифроаналоговый преобразователь ., управляемый напряжением генератор, а также второй регистр памяти и цифровой частотный компаратор, отличающееся тем, что, с целью повышения стабильности частоты и уменьшения времени перестройки частоты выходного сигнала, в него введены цифровой синтезатор частоты и коммутатор, причем выход управляемого напряжением генератора соединен с первым входом цифрового частотного компаратора, второй вход которого соединен с выходом цифрового синтезатора частоты, вход цифрового синтезатора частоты и вход опорной частоты цифрового частотного компаратора объединены и являются входом сигнала опорной частоты, первый и второй выходы цифрового частотного компаратора соединены с соответствующими входами коммутатора, выход которого соединен с входом первого регистра памяти, управляющий вход цифрового синтезатора частот соединен с выходом второго регистра памяти, вход управления первого регистра памяти, вход управления коммутатора и вход второго регистра памяти объединены и являются входом управления устройства стабилизации частоты управляемого напряжением генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1982 |

|

SU1067603A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1991 |

|

RU2010414C1 |

| Устройство для кодирования сигналов частотных датчиков | 1987 |

|

SU1564728A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МЕСТА ПОВРЕЖДЕНИЯ ЭЛЕКТРИЧЕСКОГО КАБЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2190234C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

| Устройство для сопряжения микроЭВМ с кассетным магнитофоном | 1982 |

|

SU1345185A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1626314A1 |

| Формирователь частотно-модулированных сигналов | 1988 |

|

SU1711319A1 |

Изобретение относится к радиоизмерительной технике и м. б. использовано при разработке анализаторов спектра. Цель изобретения - повышение стабильности частоты и уменьшение времени перестройки частоты выходного сигнала. Устройство содержит управляемый напряжением г-р I, цифроаналоговый преобразователь 2, регистры памяти 3, 7, цифровой частотный компаратор 4. Для достижения цели в устр-во введены коммутатор 5 и цифровой синтезатор частоты 6. В устройстве происходит непрерывная коррекция выходной частоты - I. Коммутатор 5 служит для ускорения процесса коррекции при изменении рабочей частоты. Принцип его работы заключается в изменении веса импульсов частотной коррекции, снимаемых с выходов компаратора 4, в процессе перестройки выходной частоты - I. 4 ил.

+

/

т 1

запись адрес данные шина tin

Фиг.З

Srf

„ Сброс

/7

ti

I

/5

Сигналы частотной коррекции

Фиг. k

Л

/5,

Старший каскад

23t на Si,20

г;5|

п-1

22

2/

А

Ш

01

23„

23fin-t)

J3n Вп

Ш

2Эгя

а &(..

| Radio and Electron Eng, 1978, v | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

| Устройство стабилизации частотыКВАРцЕВОгО гЕНЕРАТОРА | 1979 |

|

SU803107A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-09—Подача