где KH-IKI (r) - выходной код первого накопителя 1 в зз псимости от такта работы устройства. Таким образом на выходе первого накопителя 1 формируются коды приращений фазы формируемых сигналов за один такт работы устройства Указанные коды поступают на вход второго накопителя 3, где осуществляется их суммирование. На выходе второго накопителя 3 формируются коды фазы синтезируемого сигнала в дискретные моменты времени, численное значение которых определяется соотношением

нп

2

(r)S(KuJHj+2 К/г)

г - 1г 1 J

N

fint U- 2(КОЦ + I Кд) . (6) |N| r 1r 1j

При JTGM второе слагаемое в правой части выражения (6) реализуется автоматически путем переполнения второго накопителя 3, емкость которого эквивалента 2л. Таким образом на выходе второго накопителя 3 формируется последовательность кодов фазы, численные значения которых изменяются в соответствии с законом полинома второй степени, что соответствует синтезу личейно-частотно-модулированно- го сигнала В комбинационном сумматоре 4 выходньн коды второго накопителя 3 суммируются с кодом фазового сдвига К , который поступает с пятого выхода формирователя 2. В течение длительности формируемого сигнала код фазового сдвига K/Vfl на пятом выходе формирователя 2 несколько раз изменяется. Количество манипуляций фазы и элементарных частей в формируемом сигнале определяется числом двоичных разрядов i, которые используются для адресации второго блока 14 памяти в формирователе 2. Таким образом, на выходе комбинационного сумматора 4 формируется последовательность кодов фазы, которая соответствует закону изменения фазы сложного линейно-частотно-модулированного фазоманипулированного сигнала и описывается выражением

где 1/.1 (r) - кодообразующая последовательность.

Результирующий код фазы К (г) формируемого сигнала фиксируется синхронизирующими импульсами в регистре 5.

Сформированные коды фазы Ку (г) формируемого сигнала с выхода регистра 5 поступают на входы адресации блока 6 памяти, в котором записана таблица преобразования, соответствующая функции синуса. Таким

образом в блоке 6 памяти осуществляется преобразование фаза-синус и на его выходе формируются коды амплитудных выборок синтезируемого линейно-частотно- модулированного фазоманипулироваиного

сигнала. Указанные коды поступают на вход ЦАП 7, где преобразуются в соответствующую аналоговую величину. В результате этого на выходе ЦАП 7 формируется дискретный сигнал. Переход от дискретного к

непрерывному сигналу осуществляется с помощью полосового фильтра 8, полоса пропускания которого согласована с полосой частот формируемого сигнала.

Процесс формирования линейно-частотно-модулированного фазоманипулиро- ванного сигнала заканчивается в момент установления на третьем выходе двоичного счетчика 10 низкого уровня напряжения.

При этом содержимое старших q разрядов двоичного счетчика 10 изменяется на единицу и соответ ственно изменяется код адресации первого блока 11 памяти. Последнее приводит к тому, что на первом и втором

выходах формирователя 2 формируются новые коды скорости частотной модуляции К а и начальной частоты Код последующего формируемого сигнала. Далее процесс установки цифрового синтезатора сигналов

в исходное состояние и формирования выходного сигнала аналогичен описанному. Можно формировать линейно-частотно-модулированные сигналы без внутриимпульс- ной фазовой манипуляции. Это достигается

в том случае, если с второго выхода первого блока 11 памяти на управпяющий вход второго блока 14 памяти поступает запрещающий сигнал, под действием которого в теиение всей длительности линейно-частотно-модулированного сигнала на выходах второго блока 11 памяти формируется нулевой код фазового сдвига.

Таким образом, цифровой синтезатор сигналов обладает широкими функциональными возможностями и позволяет осуществлять внутриимпульсную фазовую манипуляцию в формируемом сигнале. Кроме того, цифровой синтезатор сигналов обладает быстродействием, так как реализована минимальная по аппаратурным затратам структура вычислителя кодов фазы формируемого линейно-частотно-модулированного сигнала. В данном случае вычислитель кодов фазы состоит из двух последовательно включенных первого и второго накопителей 1 и 3, синхронизация которых осуществляется одновременно от одного формирователя 2, т.е. при вычислении кодов фазы формируемого сигнала, преобразования кодов фазы в коды амплитуды и цифроаналоговым преобразовании используется конвейерный метод вычислений. Повышение быстродействия устройства достигается путем соответствующего разделения необходимых вычислительных операций по различным тактам работы устройства. Например, если передним фронтом очередного синхронизирующего импульса в регистр ЦАП 7 записывается код амплитуды для момента времени tr, то этим же синхроимпульсом в регистр 5 записывается код фазы сигнала для момента времени (tr + Т), в регистр второго накопителя 3 записывается код фазы формируемого сигнала для момента времени (tr + 2Т), а в регистр первого накопителя 1 записывается код приращения фазы формируемого сигнала для момента времени (tr + ЗТ).

Использование конвейерного метода вычислений позволяет добиться максимального быстродействия устройства в целом. Минимальный период импульсов синхронизации в данном случае определяется максимальным временем выполнения одной из необходимых операций. В предлагаемом устройстве наибольшее время необходимо для выполнения операции суммирования в первом или втором накопителях 1 и 3, разрядность которых не менее двадцати двоич- ных разрядов. Поэтому минимальное значение периода синхронизирующих импульсов предлагаемого устройства определяется соотношением

Т 1сл ,

(8)

где ten - время выполнения операции сложения в накапливающем сумматоре (накопителе);

t - время сложения в комбинацион- ном сумматоре;

t3 - время задержки в буферном регистре, входящем в состав первого или второго накопителя 1,3.

Формула изобретения

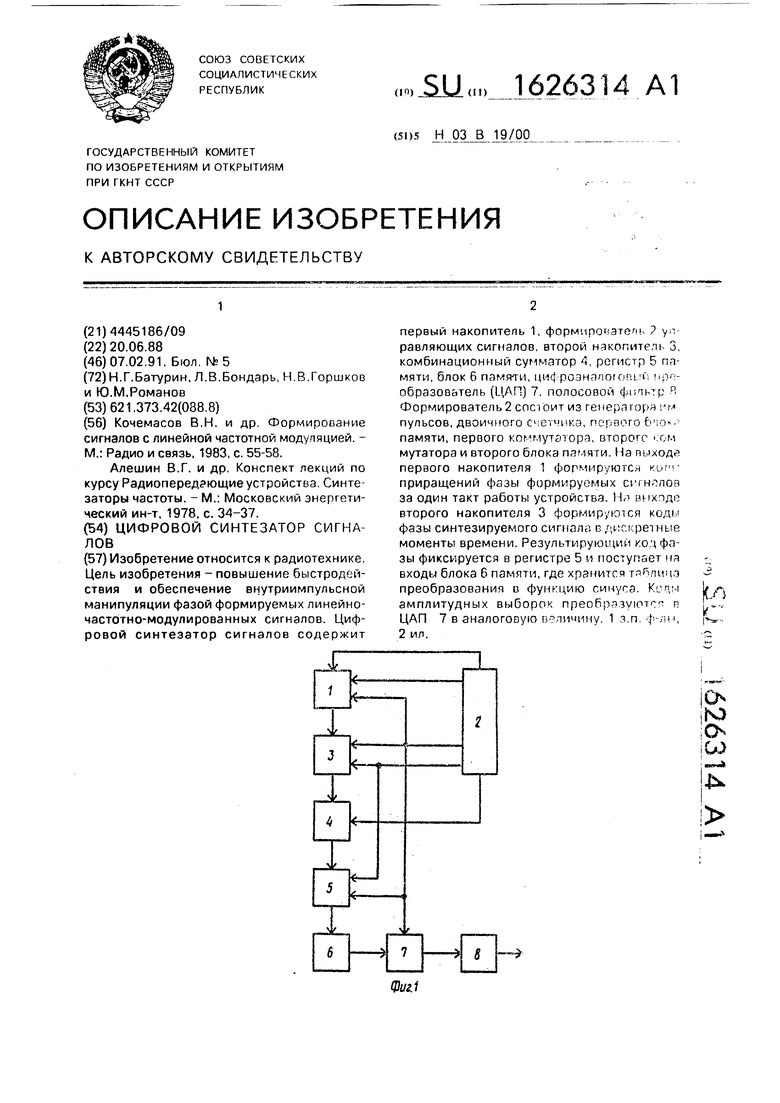

01. Цифровой синтезатор сигналов, содержащий последовательно соединенные первый накопитель и второй накопитель, последовательно соединенные блок памяти, цифроаналоговый преобразователь и по5 лосовой фильтр, отличающийся тем, что, с целью повышения быстродействия и обеспечения внутриимпульсной манипуляции фазой формируемых линеино-частотно- модулированных сигналов, введен

0 формирователь управляющих сигналов, а между выходом второго накопителя и входом блока памяти введены последовательно соединенные комбинационный сумматор и регистр памяти, первый и второй выходы

5 формирователя управляющих сигналов подключены соответственно к первому и второму входам первого накопителя, вход синхронизации которого объединен с входами синхронизации второго накопителя,

0 регистра памяти и цифроаналогового преобразователя и подключен к третьему выходу формирователя управляющих сигналов, четвертый выход которого соединен с установочным входом второго накопителе и с

5 установочным входом регистра памяти, а второй вход комбинационного сумматора подключен к пятому выходу формирователя управляющих сигналов.

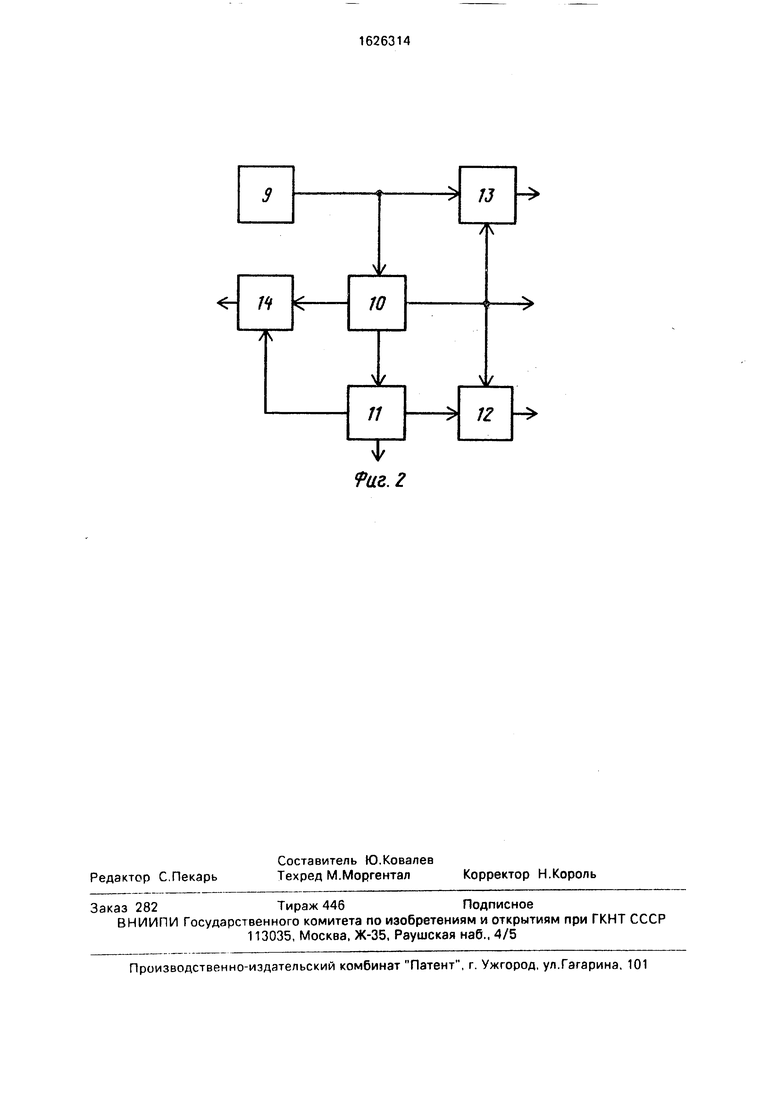

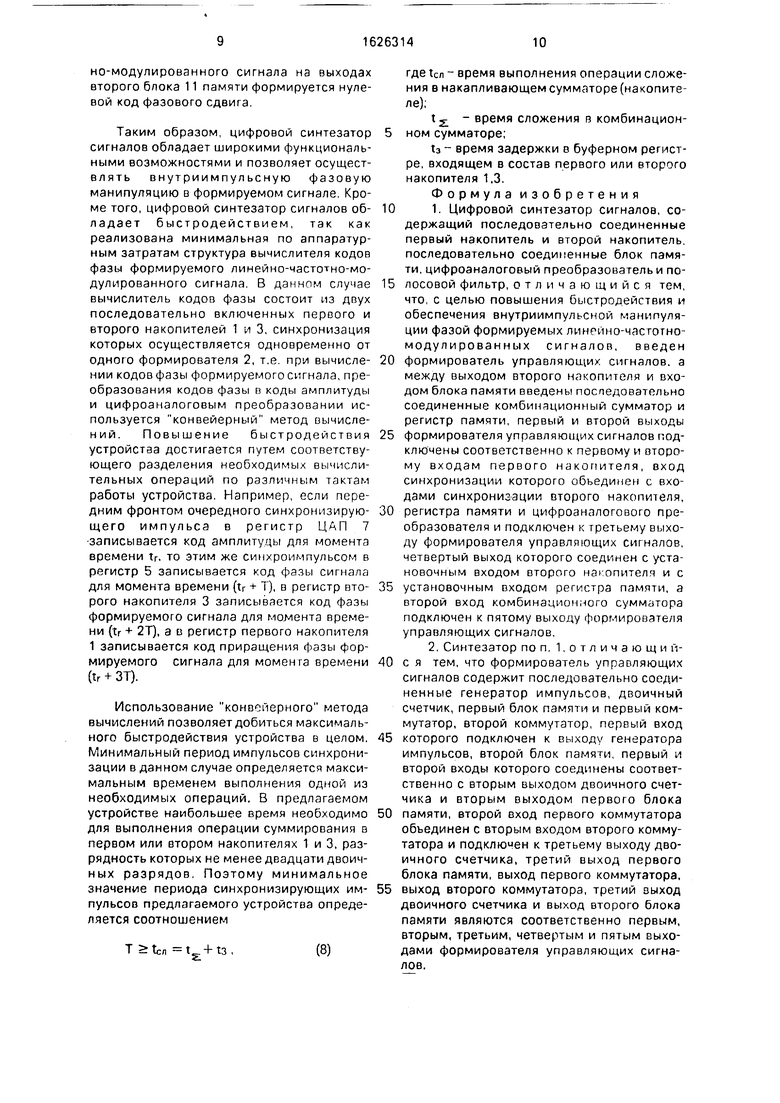

2. Синтезатор по п. 1. о т л и ч а ю щ и й0 с я тем, что формирователь управляющих сигналов содержит последовательно соединенные генератор импульсов, двоичный счетчик, первый блок памяти и первый коммутатор, второй коммутатор, первый вход

5 которого подключен к выходу генератора импульсов, второй блок памяти, первый и второй входы которого соединены соответственно с вторым выходом двоичного счетчика и вторым выходом первого блока

0 памяти, второй вход первого коммутатора объединен с вторым входом второго коммутатора и подключен к третьему выходу двоичного счетчика, третий выход первого блока памяти, выход первого коммутатора,

5 выход второго коммутатора, третий выход двоичного счетчика и выход второго блока памяти являются соответственно первым, вторым, третьим, четвертым и пятым выходами формирователя управляющих сигналов.

Ф

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь частотно-модулированных сигналов | 1990 |

|

SU1732420A1 |

| Формирователь линейно-частотно-модулированных сигналов | 1987 |

|

SU1494203A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Цифровой синтезатор частотно-модулированных сигналов | 1988 |

|

SU1552345A1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Цифровой вычислительный синтезатор с быстрой перестройкой частоты | 2019 |

|

RU2721408C1 |

| Цифровой вычислительный синтезатор с подавлением перекрестных помех | 2019 |

|

RU2726833C1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| Цифровой вычислительный синтезатор частотно-модулированных сигналов | 2019 |

|

RU2718461C1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия и обеспечение внутриимпульсной манипуляции фазой формируемых линейно- частотно-модулированных сигналов. Цифровой синтезатор сигналов содержит первый накопитель 1, формирователи 1 у равляющих сигналов, второй накопитель 3, комбинационный сумматор 4, регистр 5 памяти, блок 6 памяти, цис| p03H-innrri uii - обраэователь (ЦАП) 7. полосовой Я Формирователь 2 состоит из генератора гм пульсов, двоичного с1 ет1П Кэ, пс-рв го f r памяти, первого коммутатора, второго см мутатора и второго блока памя ги. На выхода первого накопителя 1 формируются кы приращений фазы формируемых за один такт работы устройства. Н/ вихпде второго накопителя 3 формируются кодп фазы синтезируемого сигнала вдиг; речные моменты времени. Результирующий когд фазы фиксируется в регистре 5 и поступает на входы блока 6 памяти, где хранится преобразования в функцию синуга. амплитудных выборок преобразуют п ЦАП 7 в аналоговую величину 1 зп ли, 2 ил. (Л

| Кочемасов В.Н | |||

| и др | |||

| Формирование сигналов с линейной частотной модуляцией | |||

| - М.: Радио и связь, 1983, с | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Алешин В.Г | |||

| и др | |||

| Конспект лекций по курсу Радиопередающие устройства | |||

| Синтезаторы частоты | |||

| - М.: Московский энергетический ин-т, 1978, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

Авторы

Даты

1991-02-07—Публикация

1988-06-20—Подача