Изобретение относится к радиотехнике и может быть использовано в синхронных системах радиотехнических комплексов для формирования сигналов с малым временем дискретной перестройки частоты в широких пределах и минимизированным уровнем побочных (паразитных) составляющих в спектре выходного колебания.

Известна традиционная структура синтезатора частот на основе системы фазовой автоподстройки частоты (ФАПЧ), реализующая методику косвенного синтеза частоты. Такая схема включает в себя эталонный генератор, делитель частоты с фиксированным коэффициентом деления, фазовый детектор, петлевой фильтр, усилитель постоянного тока, подстраиваемый генератор и делитель частоты с переменным коэффициентом деления, образующих кольцо фазовой автоподстройки частоты подстраиваемого генератора [1, с.37]. Данная схема, являющаяся прототипом заявляемого устройства, обладает недостаточным быстродействием при первоначальной синхронизации и дискретной перестройке частоты в широких пределах.

Улучшенное быстродействие при первоначальной синхронизации и дискретной перестройке частоты присуще схеме синтезатора частот, в которой используется импульсный частотно-фазовый детектор (ЧФД) с тремя устойчивыми состояниями и блоком генераторов тока заряда/разряда. Структура и описание работы такого синтезатора, выполненного на основе системы фазовой автоподстройки частоты с подкачкой заряда - Charge Pump Phase Locked Loop (CPPLL), приведена в работах [2,3]. Однако существенным недостатком структур синтезаторов на основе базовой схемы CPPLL является наличие в спектре выходного колебания синтезатора множества побочных (паразитных) дискретных составляющих. Это обусловлено тем, что на выходе импульсного частотно-фазового детектора системы CPPLL в переходном и синхронном режимах работы непрерывно возникает хаотичный поток коротких импульсов [4,5], которые, поступая на вход управления частотой

подстраиваемого генератора, создают побочные (паразитные) составляющие в спектре выходного колебания синтезатора.

Таким образом, известные ранее структуры синтезаторов частот не позволяют достичь высокого быстродействия дискретной перестройки в широком диапазоне частот при условии отсутствия в спектре выходного колебания множества побочных (паразитных) составляющих.

Целью изобретения является комплексное (одновременное) улучшение основных параметров синтезатора частот, а именно: сокращение времени первоначальной синхронизации и дискретной перестройки частоты в процессе работы и минимизация уровня побочных (паразитных) составляющих в спектре выходного колебания синтезатора частот.

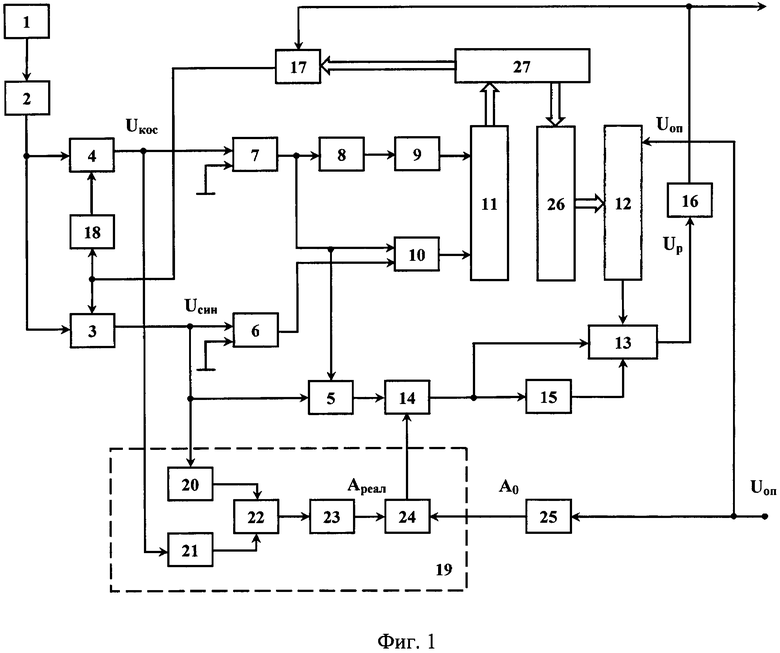

Синтезатор частот содержит эталонный генератор 1, делитель частоты с фиксированным коэффициентом деления 2, фазовый детектор 3, синхронный детектор 4, коммутатор 5 полярности сигнала, первый 6 и второй 7 компараторы напряжений, формирователь импульсов 8, линию 9 временной задержки, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10, реверсивный счетчик 11, цифро-аналоговый преобразователь (ЦАП) 12, первый сумматор 13, перемножитель сигналов 14, интегратор 15, подстраиваемый генератор 16, делитель частоты с переменным коэффициентом деления (ДПКД) 17, фазовращатель 18 на π/2, блок 19 установки и стабилизации петлевого усиления (БУСПУ), масштабирующий делитель напряжения 25, буферный регистр 26 и блок контроля и управления 27. Блок БУСПУ (19) содержит первый и второй блоки возведения текущего значения напряжения во вторую степень 20 и 21, второй сумматор 22, блок возведения текущего значения напряжения в ½ степень 23 и второй делитель напряжений 24,

В обсуждаемом устройстве, в отличие от систем CPPLL, отсутствуют импульсные ЧФД, которые создают импульсные помехи в управляющем частотой ПГ напряжении. Это обуславливает минимизацию уровня побочных (паразитных) составляющих в спектре выходного колебания синтезатора.

Устройство работает в двух режимах: режим первоначальной синхронизации и режим дискретной перестройки частоты.

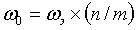

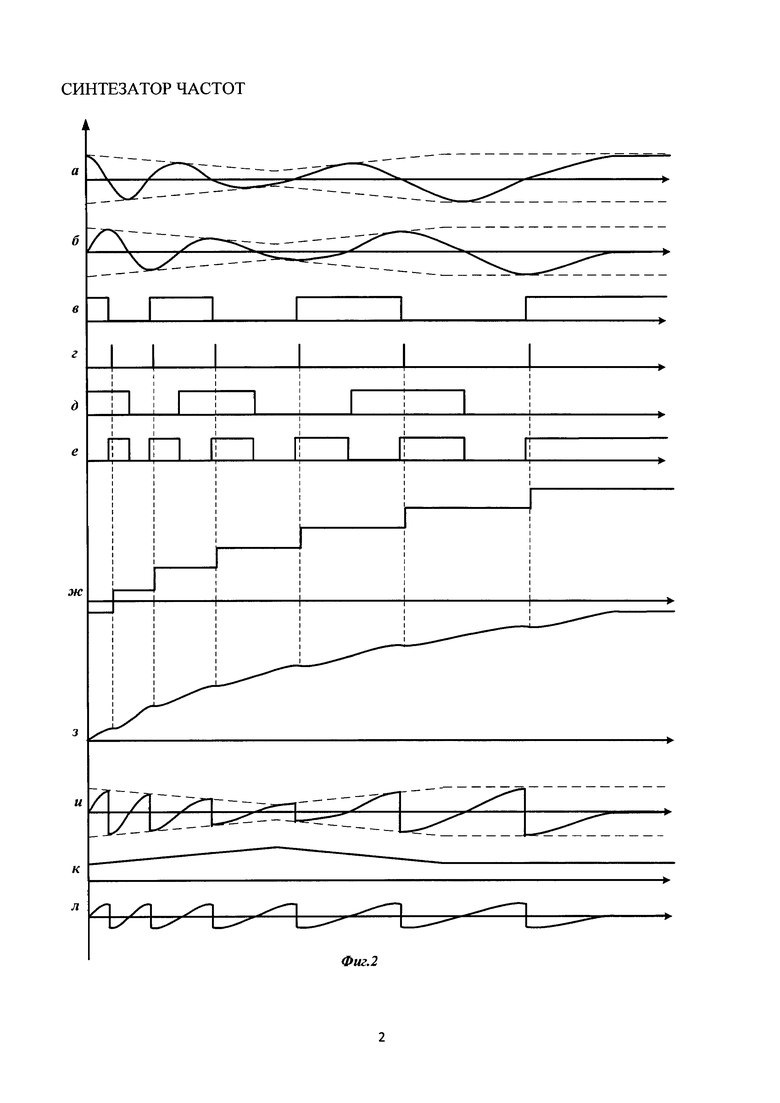

1. В режиме первоначальной синхронизации (при включении устройства) на выходах фазового 3 и синхронного 4 детекторов возникают квадратурные составляющие биений с частотой, соответствующей начальной частотной расстройке Δω=ωэ/m-ω0/n, где ωэ - частота сигнала с выхода эталонного генератора, m - фиксированный коэффициент деления в делителе частоты 2, ω0- частота колебаний выходного сигнала подстраиваемого генератора 16, n - переменный коэффициент деления в ДПКД 17. На фиг.2 показаны эпюры напряжений в точках схемы устройства для случая Δω > 0.

На фиг. 2а и фиг.2б показаны выходные сигналы синхронного 4 и фазового 3 детекторов соответственно. Первый 6 и второй 7 компараторы напряжений из выходных сигналов детекторов формируют логические сигналы, показанные на фиг.2д и фиг.2в. Формирователь импульсов 8 формирует короткие импульсы в моменты времени соответствующие фронтам выходного импульсного сигнала второго компаратора 7. На фиг.2г показаны эти импульсы, прошедшие через линию 9 временной задержки. Выходной сигнал логической схемы «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10 показан на фиг.2е. Из эпюр фиг.2г,е следует, что код, записанный в реверсивном счетчике 11 и далее ретранслированный через блок 27 контроля и управления в код буферного регистра 26 и, следовательно, выходное напряжение ЦАП 12 нарастают. Эпюры выходного напряжения ЦАП 12 показаны на фиг.2ж.

Таким образом, при появлении сигнала на входе системы выходное напряжение ЦАП 12 ступенчато нарастает, в результате чего частота подстраиваемого генератора 16 изменяется в сторону уменьшения текущего частотного рассогласования Δω.

При снижении текущего частотного рассогласования Δω до величины, соответствующей полосе захвата аналоговой ветви управления частотой ПГ (включающей в себя блоки 3, 5, 14, 15 и 13) происходит установление синхронного режима работы синтезатора частот.

На фиг. 2л и фиг.2и показаны соответственно выходной сигнал перемножителя сигналов 14 и выходной сигнал коммутатора 5 полярности сигнала, а на фиг,2з показан выходной сигнал (Up) первого сумматора 13, осуществляющий регулирование частоты ПГ 16.

Таким образом, формирование счетных импульсов для реверсивного счетчика на основе колебаний разностной частоты с выхода детекторов внутри цифровой ветви управления частотой ПГ (включающей в себя блоки 3, 4, 6, 7, 8, 9, 10, 11, 26, 12 и 13) приводит к значительному сокращению времени синхронизации синтезатора частот. При этом многократное расширение полос захвата и удержания синхронного режима работы устройства по отношению к прототипу ограничивается только разрядностью и быстродействием элементной базы цифровых блоков схемы.

При изменении полярности начального частотного рассогласования, т.е. при условии Δω < 0, изменяется направление счета реверсивного счетчика 11 и, соответственно, полярность изменений напряжений на выходе ЦАП 12 и первого сумматора 13. В остальном процесс первоначальной синхронизации синтезатора и эпюры напряжений в точках схемы остаются аналогичными.

Для корректного функционирования и повышения точности и стабильности процесса синхронизации в устройстве осуществляется согласование локальных дискриминационных характеристик цифровой и аналоговой ветвей управления частотой ПГ. Единичный дискрет ΔUЦАП, формируемого на выходе ЦАП ступенчатого напряжения, должен соответствовать полному размаху напряжения сигнала на выходе коммутатора полярности, равному 2А0. Для этой цели опорное напряжение Uоп цифро-аналогового преобразователя используется для формирования единичных аналоговых ступеней напряжения с выхода ЦАП (ΔUЦАП = Uоп /2q, где q - разрядность ЦАП) и для вычисления в масштабирующем делителе напряжения 25 нормализованного (требуемого) значения амплитуды сигнала фазового рассогласования с выхода фазового детектора (А0 = Uоп /2q+l). Далее с помощью блока установки и стабилизации петлевого усиления 19 реально возникающее значение амплитуды

сигнала фазового рассогласования с выхода фазового детектора 3 приводится к нормализованному (требуемому) значению (А0 = Uоп /2q+l).

Установка и стабилизация требуемого коэффициента петлевого усиления аналоговой ветви управления осуществляется в текущем масштабе времени и происходит следующим образом. Квадратурные составляющие биений с частотой Δω с выходов фазового 3 и синхронного 4 детекторов подаются на входы первого и второго блоков возведения текущего значения напряжения во вторую степень 20 и 21 соответственно. На фиг.2а и фиг.2б, показаны сигналы с выходов синхронного и фазового детекторов при изменяющихся амплитудах сигналов на входе устройства и с выхода ПГ или изменяющихся коэффициентах передачи детекторов. Выходные сигналы блоков 20 и 21 подаются на входы второго сумматора 22, напряжение с выхода которого поступает на вход блока возведения текущего значения напряжения в ½ степень 23. Выходное напряжение блока 23 - Ареал (реал - реальное), соответствующее амплитуде напряжений биений с выходов детекторов, поступает на первый вход (вход знаменателя дроби деления) второго делителя напряжений 24. На второй вход (вход числителя дроби деления) второго делителя напряжений 24 поступает постоянное напряжение А0, уровень которого соответствует номинальному (требуемому) значению амплитуды выходных сигналов детекторов. Сигнал на выходе второго делителя напряжений 24, показанный на фиг.2к, соответствует мгновенному текущему отклонению значения амплитуды выходных сигналов детекторов от номинального значения А0 и представляет собой корректирующий коэффициент, подаваемый на второй вход перемножителя сигналов 14. Выходной сигнал перемножителя сигналов 14, с учетом коррекции амплитуды сигнала с выхода фазового детектора 3, показан на фиг.2л.

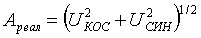

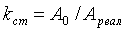

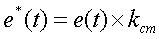

Если ввести обозначения: UK0C, UСИН, - напряжение на выходе синхронного и фазового детекторов соответственно (кос - косинусное, син - синусное). Ареал - мгновенное текущее значение амплитуды выходного сигнала детекторов, Uоп - опорное напряжение ЦАП, А0 - номинальное (требуемое) значение

амплитуды сигналов с выходов детекторов, kст - коэффициент коррекции значения коэффициента петлевого усиления (ст - стабилизации), e(t) - ам-плитуда напряжения на выходе коммутатора полярности 5, e*(t) - сигнал на выходе блока 14, то выполняемую в БУСПУ процедуру коррекции значения коэффициента петлевого усиления системы можно описать следующими соотношениями:

1.

2.

3.

4.

Вследствие изложенного, реализуется сопряжение коэффициентов передачи аналоговой ветви управления частотой ПГ (ее локальная дискриминационная характеристика приведена на фиг.2л) и цифровой ветви управления (ее локальная дискриминационная характеристика приведена на фиг.2ж). Это обеспечивает «сшивание» и «линеаризацию» (см. эпюру фиг.2з) глобальной дискриминационной характеристики заявляемого устройства.

После завершения процесса первоначальной синхронизации устройство переходит в режим синхронной работы.

2. В режиме дискретной перестройки частота выходного колебания ПГ

частоты синтезатора аналогичны описанным выше процессам первоначальной синхронизации.

1. Мартиросов В.Е. Оптимальный прием дискретных сигналов ЦСПИ. М.: Радиотехника, 2010. - 208 с, с. 37.

2. Gardner F.M. Charge-Pump Phase-Lock Loops. // IEEE Transactions on Communications. Vol. com-28, №11, November, 1980, p.1849-1858.

3. Egan F.W. Frequency Synthesis by Phase Lock, 2nd Edition. John Wiley & Sons inc., 1999, 624 pp.

4. Donald R. Stephens. PHASE-LOCKED LOOPS FOR WIRELESS COMMUNICATIONS. Digital, Analog and Optical Implementations. Kluwer Academic Publishers, 2002, 422 pp.

5. Дмитриев С., Никитин Ю. Одиночные радиочастотные синтезаторы с импульсно-фазовой автоподстройкой частоты серии ADF4000 // Компоненты и технологии. №9, 2002.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЛОБАЛЬНО ЛИНЕАРИЗОВАННАЯ СИСТЕМА СИНХРОНИЗАЦИИ | 2014 |

|

RU2554535C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ СИГНАЛОВ ПО СЕТИ ЭЛЕКТРОПИТАНИЯ | 2001 |

|

RU2178952C1 |

| Демодулятор сигналов фазовой телеграфии | 1986 |

|

SU1392631A1 |

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| Аналого-цифровой амплитудный детектор | 1986 |

|

SU1417183A1 |

| Демодулятор сигналов частотной телеграфии | 1986 |

|

SU1392627A1 |

Изобретение относится к радиотехнике и может быть использовано в синхронных системах радиотехнических комплексов для формирования сигналов с малым временем дискретной перестройки частоты в широких пределах и минимизированным уровнем побочных (паразитных) составляющих в спектре выходного колебания. Целью изобретения является комплексное (одновременное) улучшение основных параметров синтезатора частот, а именно: сокращение времени первоначальной синхронизации и дискретной перестройки частоты в процессе работы и минимизация уровня побочных (паразитных) составляющих в спектре выходного колебания синтезатора частот. Синтезатор частот содержит эталонный генератор 1, делитель частоты с фиксированным коэффициентом деления 2, фазовый 3 и синхронный 4 детекторы, коммутатор 5 полярности сигнала, первый 6 и второй 7 компараторы напряжений, формирователь импульсов 8, линию 9 временной задержки, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10, реверсивный счетчик 11, цифро-аналоговый преобразователь (ЦАП) 12, первый сумматор 13, перемножитель сигналов 14, интегратор 15, подстраиваемый генератор 16, делитель частоты с переменным коэффициентом деления (ДПКД) 17, фазовращатель 18 на π/2, блок 19 установки и стабилизации петлевого усиления (БУСПУ), масштабирующий делитель напряжения 25, буферный регистр 26, блок контроля и управления синтезатором 27, а также необходимые связи между ними. 1 з.п. ф-лы, 2 ил.

1. Синтезатор частот, содержащий последовательно соединенные эталонный генератор, делитель частоты с фиксированным коэффициентом деления и фазовый детектор, а также последовательно включенные подстраиваемый генератор, выход которого является выходом устройства, и соединенный по первому входу делитель частоты с переменным коэффициентом деления, выход которого подключен к второму входу фазового детектора, отличающийся тем, что в устройство введены последовательно включенные фазовращатель на π/2, вход которого соединен с выходом делителя частоты с переменным коэффициентом деления, синхронный детектор, второй вход которого соединен с выходом делителя частоты с фиксированным коэффициентом деления, второй компаратор напряжений, второй вход которого подключен к общей шине, формирователь импульсов, линия временной задержки и соединенный по счетному входу реверсивный счетчик, а также введены последовательно включенные буферный регистр, цифро-аналоговый преобразователь и первый сумматор, первый вход которого соединен с выходом цифро-аналогового преобразователя, а выход соединен с управляющим входом подстраиваемого генератора, а также введены последовательно включенные первый компаратор напряжений, первый вход которого соединен с выходом фазового детектора, а второй вход соединен с общей шиной, логическая схема «ИСКЛЮЧАЮЩЕЕ ИЛИ», второй вход которой соединен с выходом второго компаратора напряжений, а выход подключен к управляющему полярностью счета входу реверсивного счетчика, а также введены последовательно включенные коммутатор полярности сигнала, управляющий вход которого подключен к выходу второго компаратора напряжений, а сигнальный вход соединен с выходом фазового детектора, и соединенный по первому входу перемножитель сигналов, выход которого подключен к второму входу первого сумматора, а также введен интегратор, вход которого соединен с выходом перемножителя сигналов, а выход подключен к третьему входу первого сумматора, а также введены масштабирующий делитель

напряжения, на вход которого подается опорное напряжение цифро-аналогового преобразователя, и блок установки и стабилизации петлевого усиления (БУСПУ), выход которого подключен ко второму входу перемножителя сигналов, а соответствующие входы соответственно соединены с выходом масштабирующего делителя напряжения и с выходами фазового и синхронного детекторов, а также введен блок контроля и управления, вход которого соединен с выходом реверсивного счетчика и первый выход которого подключен к второму входу делителя частоты с переменным коэффициентом деления, а второй выход подключен к входу буферного регистра.

2. Синтезатор частот по п.1, отличающийся тем, что блок установки и стабилизации петлевого усиления (БУСПУ) содержит последовательно включенные первый блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом фазового детектора, второй сумматор, блок возведения текущего значения напряжения в ½ степень и соединенный по первому входу второй делитель напряжений, выход которого является выходом БУСПУ и второй вход которого подключен к выходу масштабирующего делителя напряжения, и, кроме того, содержит второй блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом синхронного детектора, а выход подключен к второму входу второго сумматора.

| В.Е | |||

| МАРТИРОСОВ, Оптимальный прием дискретных сигналов ЦСПИ | |||

| - М.: Радиотехника, 2010, 208 с., стр | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| В.Е | |||

| МАРТИРОСОВ и др., Квазикогерентный модулятор сигнала QPSK, Труды МАИ, Выпуск N 80, 21 с, стр 1-9, рис.1 | |||

| Синтезатор частот | 1978 |

|

SU794706A1 |

| Синтезатор частот | 1985 |

|

SU1298834A1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1225013A1 |

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| Демодулятор сигналов двукратной фазовой телеграфии | 1986 |

|

SU1392630A1 |

| US 5150128 A, 22.09.1992 | |||

| US 4580107 A, 01.04.1986. | |||

Авторы

Даты

2016-08-27—Публикация

2015-06-11—Подача