| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1980 |

|

SU892666A1 |

| Формирователь импульсов | 1989 |

|

SU1698968A1 |

| Устройство для временного разделения импульсных сигналов | 1989 |

|

SU1707749A1 |

| Устройство для формирования серий импульсов | 1990 |

|

SU1781816A1 |

| Устройство подавления шумов вТЕлЕфОННОМ СлужЕбНОМ КАНАлЕ | 1979 |

|

SU794742A1 |

| Устройство для управления обменом по асинхронной магистрали вычислительной системы | 1982 |

|

SU1117624A1 |

| Устройство для вычитания и добавления импульсов | 1988 |

|

SU1557671A1 |

| Многоканальное устройство для временного разделения и синхронизации импульсных сигналов | 1989 |

|

SU1651361A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| Устройство для получения разностной частоты импульсов | 1984 |

|

SU1238220A1 |

Изобретение относится к импульсной технике и может быть использовано в радиотехнических устройствах для разделения по времени двух независимых последовательностей импульсов. Цель изобретения - расширение функциональных возможностей устройства - достигается за счет обеспечения его функционирования как в синхронном, так и в асинхронном режимах при одновременном повьшении надежности функ-. ционирования. Устройство содержит первую и вторую входные шины 1 и 2, шину 3 управления, тактовую пшну 4, триггеры 5 и 6, импульсный ключ 7, выходные шины 8 и 9, элементы ИЛИ-НЕ 10-17, элемент НЕ 18, элемент 19 задержки, элементы И-НЕ 20 и 21. Длительность сигналов на шинах 8 и 9 всегда сохраняется равной длительности тактовых импульсов, что существенно повьш1ает надежность работы ycTV ройства. 4 ил. с S (Л

Фиг.1

Изобретение относится к импульс- ной технике и может быть использован в радиоэлектронных устройствах для разделения во времени двух независи- мых последовательностей импульсов.

Цель изобретения - расширение функ- циональн ьгх возможностей путем обеспечения возможности функционирования как в синхронном, так и в асинхрон- ном режимах, при одновременном повышении надежности функционирования.

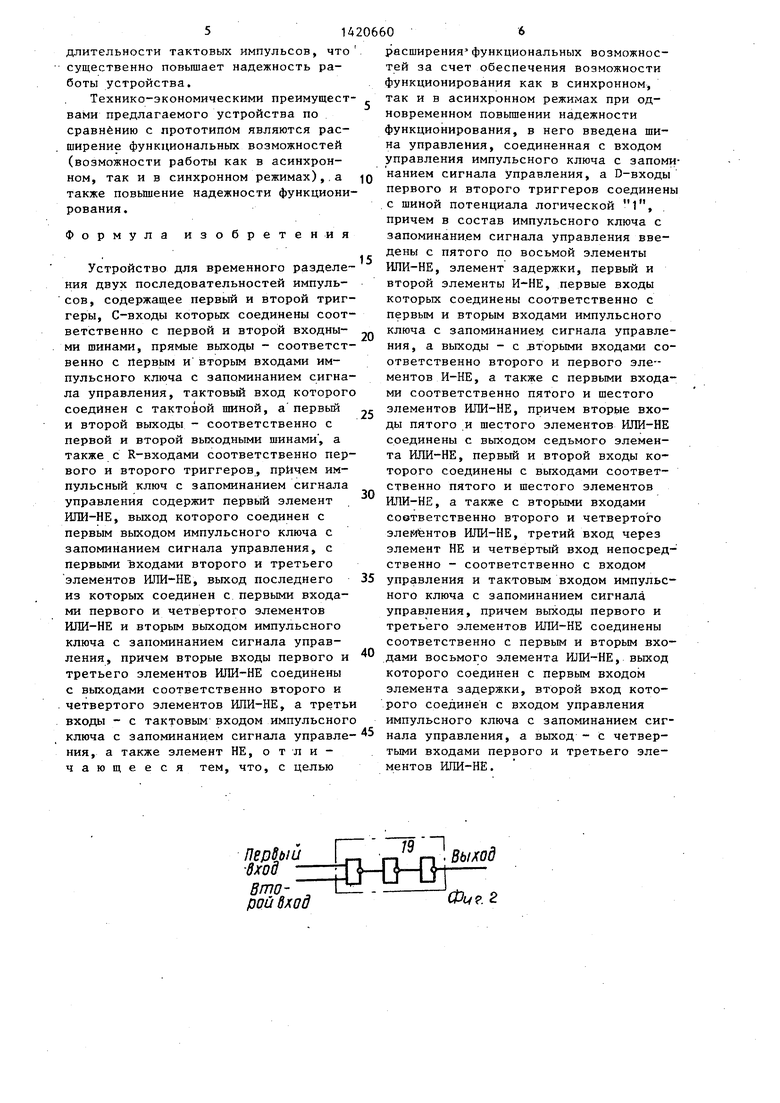

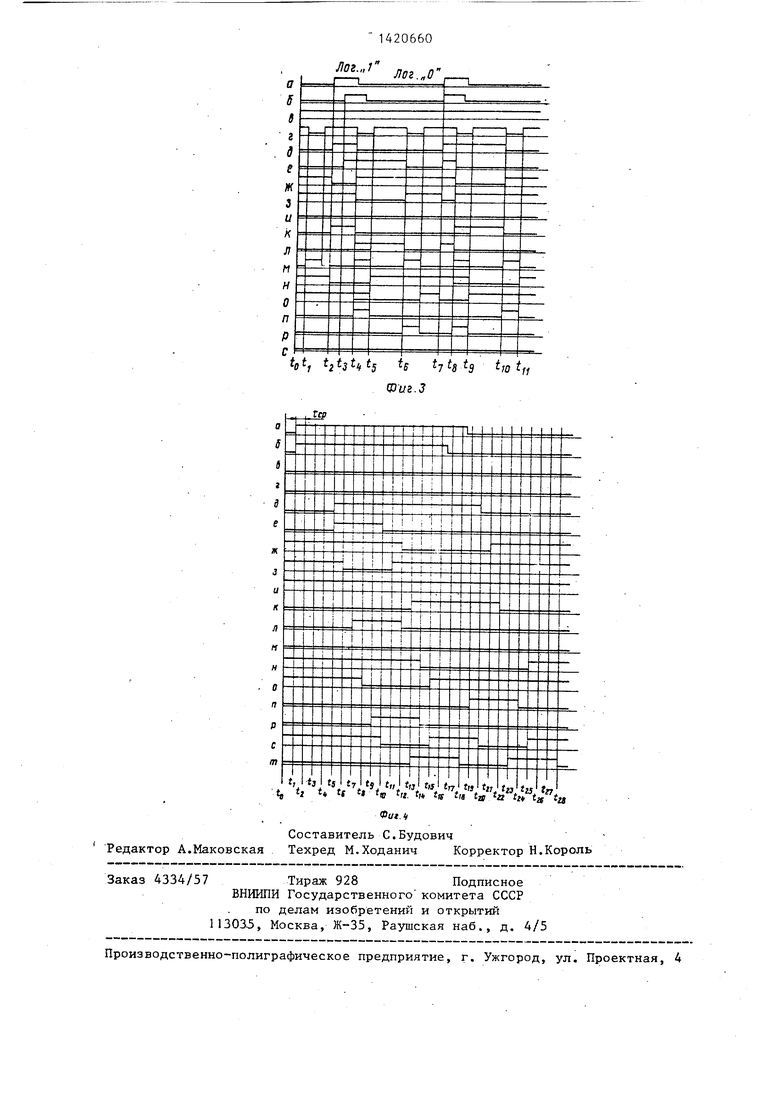

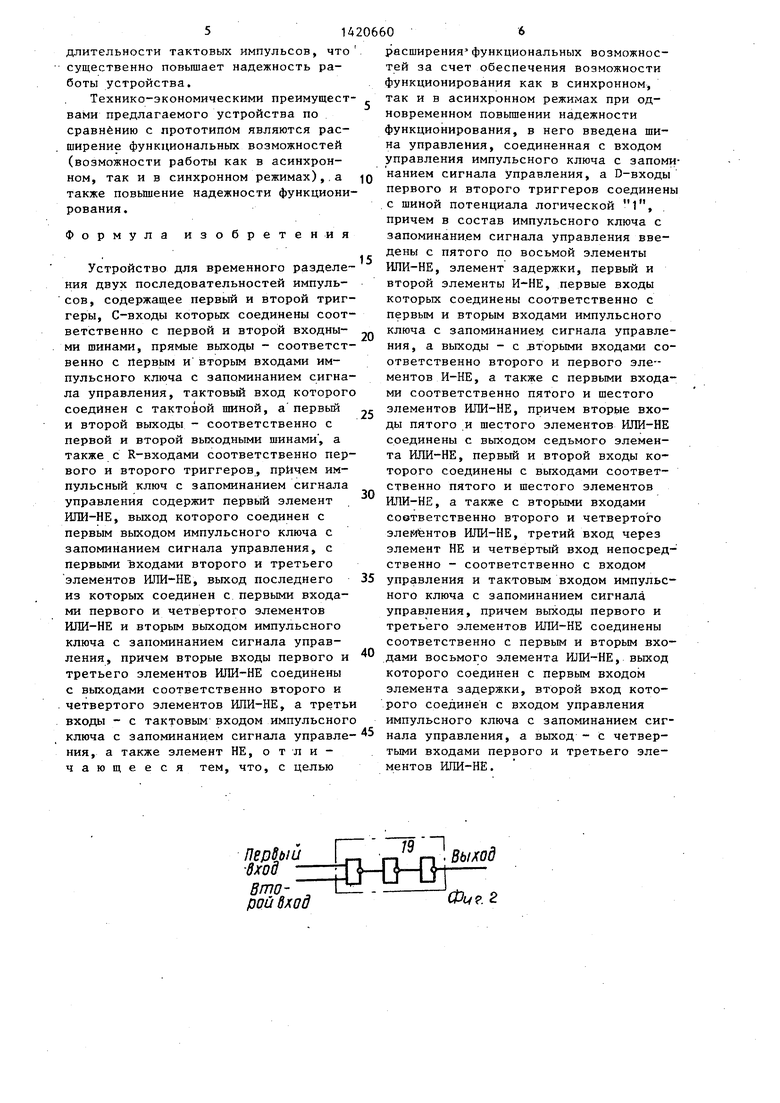

На фиг. 1 показана структурная .электрическая схема устройства; на фиг. 2 - вариант выполнения элемента задержки (19); на фиг. 3,4 - временные диаграммы, поясняющие работу устройства в синхронном и асинхронном режимах соответственно.

Устройство (фиг. 1) содержит пер- вую 1 и вторую 2 входные шины, шину 3 управления, тактовую шину 4. Шины 1 и 2 соединены с С-входами триггеров 5 и 6 соответственно, прямые выходы ко- |Торых соединены с первым и вторым . входами соответственно импульсного ключа:7 с запоминанием сигнала управления, первый выход которого сое - динен с R-входом триггера 5 и первой выходной шиной 8, а второй вы- ход - с R-входом триггера 6 и второй выходной шиной 9. Ключ 7 содержит первый элемент ИЛИ-НЕ ТО, выход которого соединен с первым выходом ключа 7 и первыми входами второго 11 и третьего 12 элементов ИЛИ-НЕ. Выход элемента ИЛИ-НЕ 12 соединен с вторым выходом ключа 7 и первыми входами четвертого 13 и второго 11 элементов ИЛИ-НЕ. Вторые входы элемен- тон ИЛИ-НЕ 11 и 13 соединены с выходами соответственно пятого 14 и шестого 15 элементов ИЛИ-НЕ, а также с первым и вторым соответственно входами седьмого элемента ИЛИ-НЕ.16. Выходы элементов ИЛИ-НЕ 10 и 12 соединены соответственно с первым и вторым входами восьмого элемента ИЛИ- НЕ 17. Третий вход элемента ИЛИ-НЕ 1б через элемент НЕ 18 соединен с входом управления ключа 7. Выход элемента ИЛИ-НЕ 17 соединен с первым входом элемента 19 задержки. Первый и второй входы ключа 7 соединены с первыми входами первого 20 и второго 21 соответственно элементов И-НЕ, выходы которых соединены с вторьми входами соответственно элементов И-НЕ 21 и 20, а также с первь ми входами соот

0

5

0 0 r Q j

0

ветственно элементов ИЛИ-НЕ 14 и 15, вторые входы которых соединены с выходом .элемента ИЛИ-НЕ 16, четвертый вход которого соединен с тактовым входом ключа 7, Выходы элементов ИЛИ- НЕ 1 1 и 13 соединены с вторыми входами соответственно элементов ИЛИ-НЕ . 10 и 12, третьи входы которых соединены с тактовым входом ключа 7, а четвертые входы - с выходом элемента 19 задержки, второй вход которого соединен с входом управления ключа 7, D-входы триггеров 5 и 6 соединены с шиной потенциала логический 1. Шина . 3 управления и тактовая шина 4 соединены соответственно с входом управления и тактовым входом ключа 7.

На фиг. 3 показаны временные диаграммы, поясняющие работу устройства в синхронном режиме: а - на входной шине 1; б - на входной шине 2; в - на шине 3 управления; г - -на тактовой шине 4; д - на выходе триггера 5; е - на выходе триггера 6; ж - на выходе элемента И-НЕ 20; з - на выходе элемента И-НЕ 21; и - на выходе элемента НЕ 18; к - на выходе элемента ИЛИ-НЕ 14| л - на выходе элемента ИЛИ-НЕ 15| м- на выходе элемента ИПИ- НЕ 16; и - на выходе элемента ИЛИ-НЕ 11; о - на выходе элемента ИЛИ-НЕ 13; п - на выходной шине 8; р - на выходной шине 9; с - на выхода элемента 19 задержки.

Аналогичные диаграммы, приведенные на фиг, 45 поясняют работу ус т- ройства в асинхронном режиме (с .- на выходе элемента ИЛИ-НЕ 17; m - на выходе элемента 19 задержки., вариант

которого показан на фиг. 2). . 1 . .

Рассмотрим работу устройства в

двух режимах.

I. Режим тактирования.

В исходном состоянии на шинах 1 и 2 - уровень логического О, на шинах 3 и 4 - уровень логической 1, триггеры 5 и 6 - в состоянии логического О, на выходах элементов 20, 21, 11, 13 и 17 - логическая 1, на выходах элементов 18, 14-16, 10, 12 и 19 логический О. .

Поступающий на шину 4 тактовый импульс на шины И и 9 не проходит. Если входным импульсом устанавливается в состояние логической 1 триг- гер 5, то элементы 20, 14 и 17 изменяют свои выходные, сигналы на противоположные, и в момент поступления

очередного тактового импульса на шине 8 появляется уровень логической

I11

I «

Этот уровень вызывает сброс триггера 5 и удерживает триггер на элементах 10.и 11, а также триггер на элементах 10 и 12 в состоянии логической 1 по выходу элемента 10 вплоть до окончания импульса. Таким образом, с выхода элем.ента 10 вьздается импульс с уровнем логической 1 и

длительностью, равной длительности тактового импульса.

Аналогичным образом в режиме тактирования работает второй канал устройства.

II.. Асинхронный режим.

На шинах 3 и 4 постоянно поддерживается уровни логического О.

В исходном состоянии на выходе инвертора 18 - уровень логической 1 на выходах остальных элементов присутствуют те же уровни логических сигналов, что и в режиме тактирования На выходе элемента 16 постоянно под- держивается уровень логического О, вследствие чего элементы 14 и 15 работают как инверторы.

С приходом импульса на шину 1 триг rep 5 устанавливается в состояние логической 1, на выходах элементов 20 и 11 появляются уровни логического

О, а на 1пине 8 - уровень логической 1. Этим уровнем сбрасывается триггер 5 и .через элемент 17 запускается элемент 19 задержки, на выходе которого появляется уровень логической 1, закрывающий элементы 10 и 12.

Надежность работы устройства повышается также за счет выполнения элементов .14-16 в виде трехстабильного триггера с неполными связями для временного разделения тактового импуль- 35 са и сигнала на выходе одного из элементов 20 и 21. Если к моменту такто- Borq импульса оба выхода элементов 20 и 21 находятся в состоянии логической

1, то этот тактовый .импульс прохо- Таким образом, на 8 выдается им- элемента 16 уровнем лопульс длительностью ( , которая определяется временем срабатывания элементов 10 и 17 и внут зенним параметром задержки элемента 19. Длительность импульса на выходе элемента 19 также равна Т и определяет минимальный промежуток времени между окончанием импульса на соответствующем выходе устройства (в данном случае на шине 8) и. началом следующего импульса на одном из выходов устройства.

Параметр t выбирается из следующих соображений.

С одной стороны, время определягической 1, удерживающим на выходах элементов 14 и 15 уровень логического О, а на выходах элементов 11 и 13 - уровень логической 1, кото45 рый запирает элементы 10 и 12, поэтому тактовые импульсы на шины 8 и 9 не проходят. Если же тактовый импульс приходит позже, чем успезает устано-. виться уровень логического О на

50 выходе одного из элементов 20 и 21, то на выходе элемента 14 или 15 вырабатывается уровень логической , запирающий элемент 16 и устанавливающий на выходе элемента 11 или 13

ет быстродействие устройства в йсин- gg уровень логического

хронном режиме и поэтому должно быть как можно меньше. С другой стороны, время t должно быть достаточным для надежного сброса триггеров 5 и 6 и

чего данный тактовый дит на Еину 8 или 9. длительность сигнало устройства всегда со

срабатывания элементов внешней схемы, в которой используется устройство. К таким элементам относятся триггеры и элементы с триггерными связями. Для надежного срабатывания этих элементов требуются импульсы с длительностью не менее 2 Т . - среднее время срабатывания одного логического элемента. Отсюда вытекает условие для выбора параметра

п /

с. 2 t

(1)

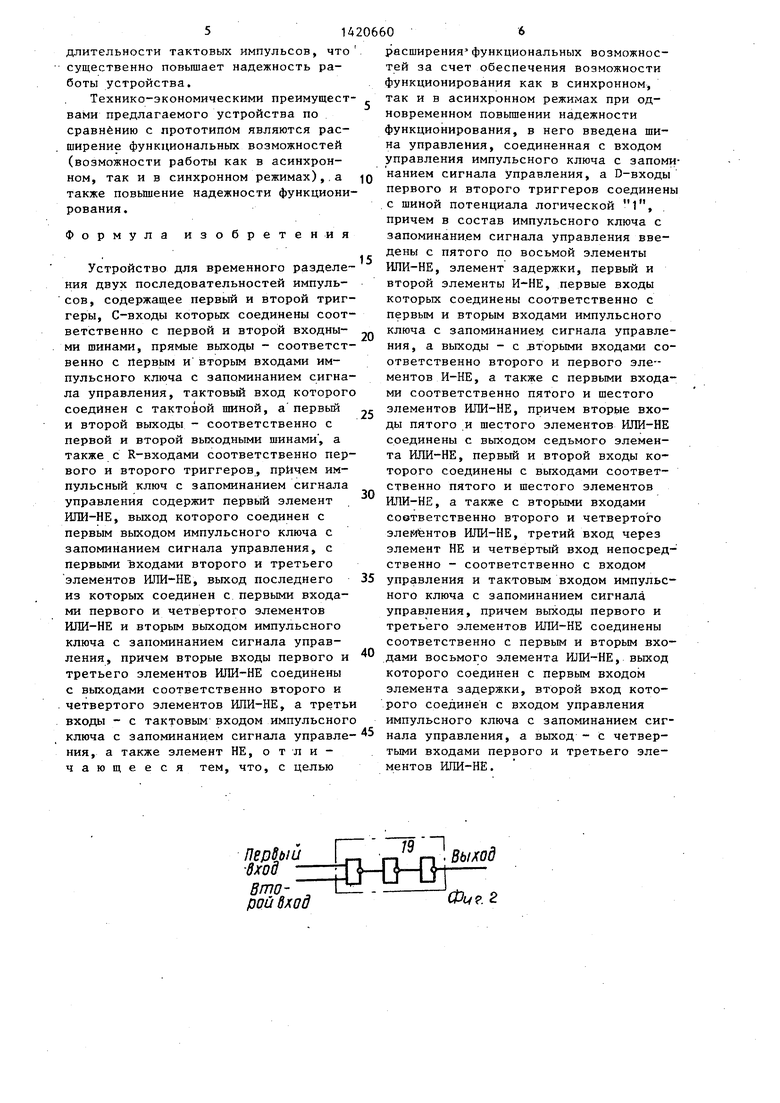

Учитывая условие (1), можно выполнить элемент 19 задержки на логичес- ких элементах так, как это показано на фиг. 2. Для приведенного примера параметр элемента задержки С, 3 б ср , а с учетом времени срабатывания элементов 10 и 17 (или 12 и 17) параметр о равен 5 e en Если из схемы элемента

IJiDi:; J ijj.p

задержки исключить инверторы, то с-. ср минимальное значение параметра для данной схемы импульсного ключа 7.

Триггер на элементах 20 и 21 позволяет с высоким разрешением по времени запомнить очередность поступления входных импульсов, что повьшает надежность работы устройства.

Надежность работы устройства повышается также за счет выполнения элементов .14-16 в виде трехстабильного триггера с неполными связями для временного разделения тактового импуль- са и сигнала на выходе одного из элементов 20 и 21. Если к моменту такто- Borq импульса оба выхода элементов 20 и 21 находятся в состоянии логической

гической 1, удерживающим на выходах элементов 14 и 15 уровень логического О, а на выходах элементов 11 и 13 - уровень логической 1, который запирает элементы 10 и 12, поэтому тактовые импульсы на шины 8 и 9 не проходят. Если же тактовый импульс приходит позже, чем успезает устано-. виться уровень логического О на

выходе одного из элементов 20 и 21, то на выходе элемента 14 или 15 вырабатывается уровень логической , запирающий элемент 16 и устанавливающий на выходе элемента 11 или 13

уровень логического

, вследствие чего данный тактовый импульс проходит на Еину 8 или 9. Таким образом, длительность сигналов на шинах В и 9 устройства всегда сохраняется равной

длительности тактовых импульсов, что существенно повышает надежность работы устройства.

Технико-экономическими преимуществами предлагаемого устройства по сравнению с прототипом являются расширение функциональных возможностей (возможности работы как в асинхронном, так и в синхронном режимах),,а также повьшение надежности функционирования.

Формула изобретения

10

15

20

30

Устройство для временного разделения двух последовательностей импульсов, содержащее первый и второй триггеры, С-входы которых соединены соответственно с первой и второй входными шинами, прямые выходы - соответственно с Первым и вторым входами импульсного ключа с запоминанием сигнала управления, тактовый вход которого соединен с тактовой шиной, а первый и второй выходы - соответственно с первой и второй выходными шинами , а также с R-входами соответственно первого и второго триггеров, причем импульсный ключ с запоминанием сигнала управления содержит первый элемент ИЛИ-НЕ, выход которого соединен с первым выходом импульсного ключа с запоминанием сигнала управления, с первыми входами второго и третьего элементов ИЛИ-НЕ, выход последнего из которых соединен с первыми входами первого и четвертого элементов ИЛИ-НЕ и вторым выходом импульсного ключа с запоминанием сигнала управления, причем вторые входы первого и третьего элементов ШШ-НЕ соединены с выходами соответственно второго и четвертого элементов ИЛИ-НЕ, а третьи входы - с тактовым входом импульсного ключа с запоминанием сигнала управле- ния, а также элемент НЕ, о т л и - чающееся тем, что, с целью

U206606

расширения функциональных возможностей за счет обеспечения возможности функционирования как в синхронном, так и в асинхронном режимах при одновременном повьшении надежности функционирования, в него введена шина управления, соединенная с входом управления импульсного ключа с запоминанием сигнала Управления, а D-входы первого и второго триггеров соединены с шиной потенциала логической 1, причем в состав импульсного ключа с запоминанием сигнала управления введены с пятого по восьмой элементы ИЛИ-НЕ, элемент задержки, первый и второй элементы И-НЕ, первые входы которых соединены соответственно с первым и вторым входами импульсного ключа с запоминанием сигнала управления, а выходы - с вторыми входами соответственно второго и первого элементов И-НЕ, а также с первыми входами соответственно пятого и шестого 25 элементов ИЛИ-НЕ, причем вторые входы пятого .и шестого элементов ИЛИ-НЕ соединены с выходом седьмого элемента ИЛИ-НЕ, первый и второй входы которого соединены с выходами соответственно пятого и шестого элементов ИЛИ-НЕ, а также с вторыми входами соответственно второго и четвертого элементов ИЛИ-НЕ, третий вход через элемент НЕ и четвертый вход непосредственно - соответственно с входом управления и тактовым входом импульсного ключа с запоминанием сигнала управления, причем выходы первого и третьего элементов ШШ-НЕ соединены соответственно с первым и вторым входами восьмого элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента задержки, второй вход которого соединен с входом управления импульсного ключа с запоминанием сигнала управления, а выход - с четвертыми входами первого и третьего элементов ИЛИ-НЕ.

35

40

nepSbia вход Вгцо; , рои Вход

ТЭ

. Вы/(од

Ф1.2.

лог.„О

tgt is Фиг.З

| Устройство для временного разделения импульсных сигналов | 1983 |

|

SU1200401A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для временного разделения импульсных сигналов | 1981 |

|

SU1007189A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-30—Публикация

1986-11-19—Подача