I

Изобретение относится к импульсной технике.

Известен триггер, построенный по схеме M-S и содержащий основной и вспомогательный триггеры D}Однако это устройство имеет oi раниченные функциональные возможности

Наиболее близким по технической сущности является M-S триггер, содержащий два основных (М) и один вспомогательный (S) триггерыС2.

Недостатком известного триггера является ограниченные функциональные возможности, т.е. известный триггер может работать либо в режиме счета, либо в режиме запоминания информации. Отсутствие возможности выполнять одним элементом несколько функций затрудняет построение сложных схем, в том числе схем с переменными параметрами, а отсутствие двух независимых тактовых входов не позволяет совмещать на одном элементе .функции синхронного и асинхронного типа.

Цель изобретения - расширение функциональных возможностей MS-триггера, заключающееся в том, что триггер по каждому из двух тактовых входов получает возможность изменять коэффициент счета с 2 на 1, изменять фазу выходного сигнала, работать по положительному и отрицательному перепаду тактового сигнала раздельно или совместно, формировать на выходе

10 последовательности, состоящие из тактовых импульсов необходимой полярности, передавать входную информацию непосредственно на выход, а наличие двух независимых тактовых входов,

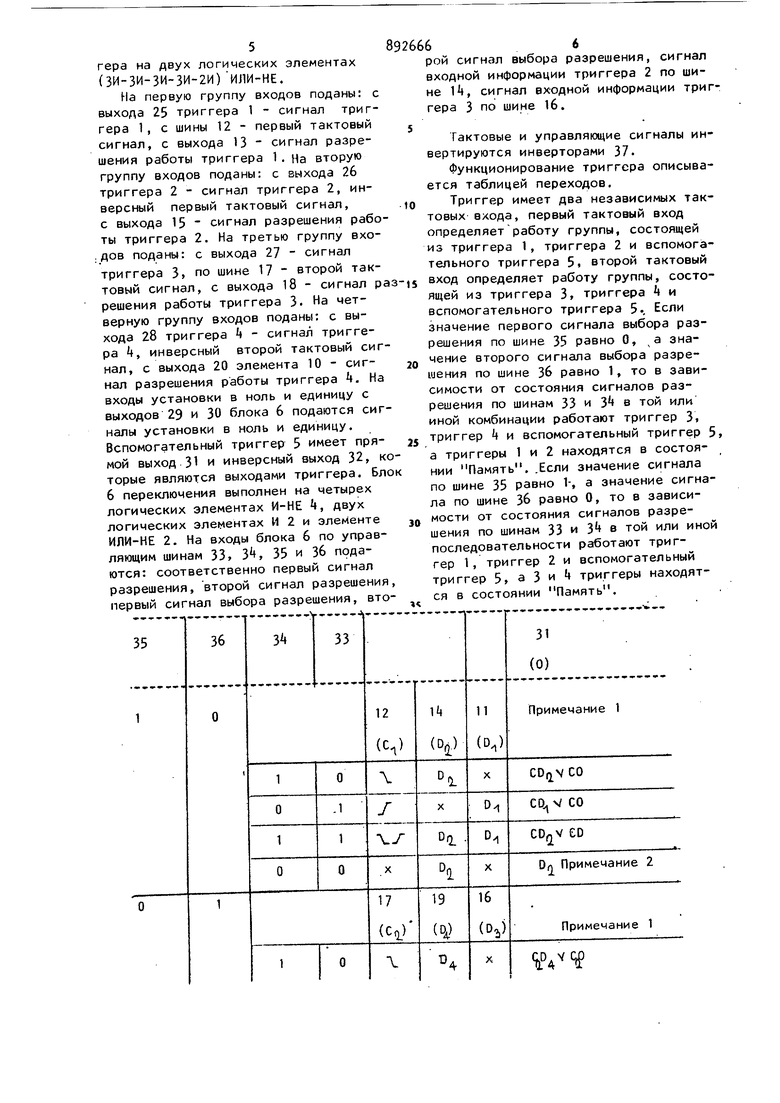

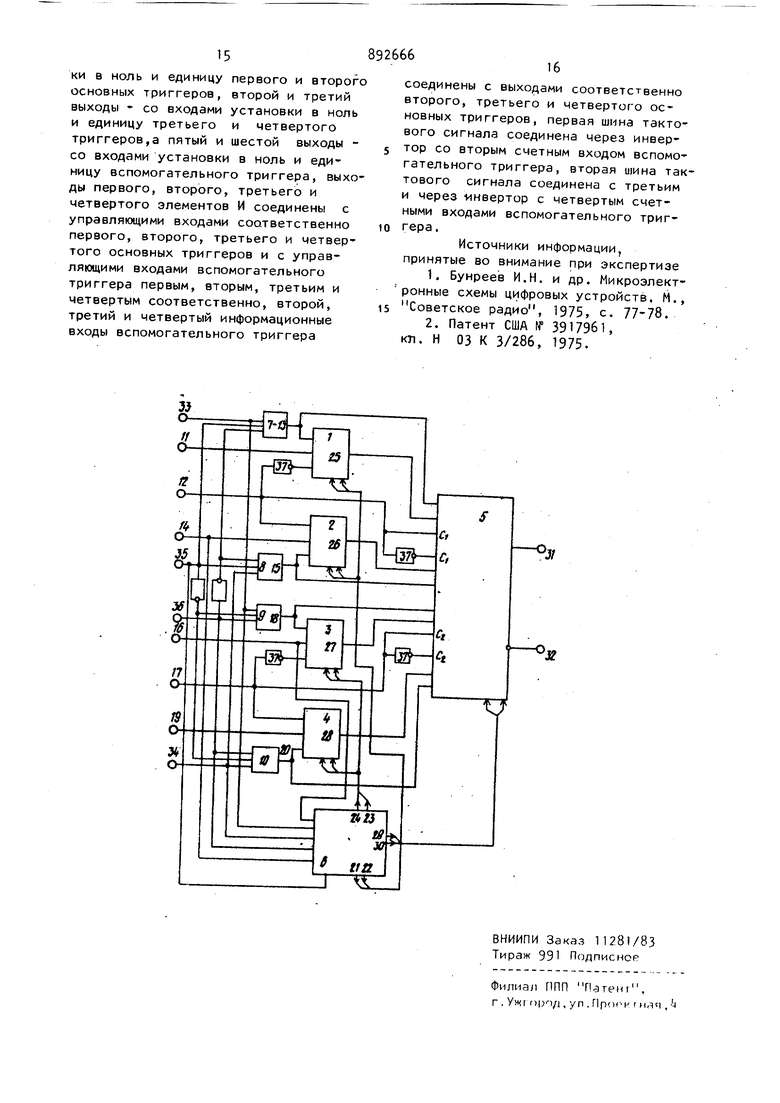

15 кроме вышеперечисленных возможностей, позволяет совмещать на одном элементе функции синхронно-асинхронного типа, синхронно-асинхронного типа по различным тактовым сигналам, асин20хронно-асинхронного типа, максимальное количество выполняемых функций без введения дополнительной коммутирующей логики равно четырем. 38 Поставленная цель достигается тем, что в триггер, содержащий два ос новных и один вспомогательный триггера, прямой и инверсный выходы, счет ный вход первого основного триггеpa через инвертор соединен с первой шиной тактового сигнала, а информационный вход - с первой информационной шиной, информационный вход второго основного триггера соединен со второй информационной шиной, первый счетный вход вспомогательного триггера соединен с первой шиной тактового сигнала, а первый информационный вход соединен, с выходом первого основного триггера, введены третий основной триггер, сметный вход которого через инвертор соединен со второй шиной тактового сигнала, а информационный вход соединен с третьей информационной шиной, четвертый основной триггер, счетный вход которого соединен со второй шиной тактового сигнала, а информационный вход соединен с четвер той информационной шиной, четыре логических элемента И, блок переключения, четыре шины управления, первая шина управления соединена с первыми входами первого и третьего элементов И и с первым входом блока пере1О1ючения, вторая шина управления соединена с первыми входами второго и четвертого элементов И и со вторым входом блока переключения, третья шина управления соединена со вторыми входами первого и второго элементов И, с третьим входом блока переключения и через инвертор со вторыми входами третьего и четвертого элементов И, четвертая шина управления соединена с третьими входами третьего и четвер того элементов И, с четвертым входом блока переключения и через инвертор с третьими входами первого и второго элементов И, пятый л шестой входы блока переключения соединены соответ ственно со второй и третьей информационными шинами, а ег,о первый и второй выходы соединены со входами установки в ноль и единицу первого и второго основных триггеров, второй и третий выходы - со входами установ ки в ноль и единицу третьего и четвертого триггеров, а пятый и шестой выходы - со входами установки в ноль и единицу вспомогательного триггера, выходы первого, второго, третьего и четвертого элементов И соединены с управляьхиими входами соответственНО первого, второго, третьего и четвертого основных триггеров и с управляющими входами вспомогательного триггера первым, вторым, третьим и четвертым соответственно, второй, третий и четвертый информационные входы вспомогательного триггера соединены с выходами соответственно второго, третьего и четвертого основных триггеров, первая шина тактового сигнала соединена через инвертор со вторым счетным входом вспомогательного триггера, вторая шина тактового сигнала соединена с третьим и через инвертор с четвертым счетными входами вспомогательного триггера. На. чертеже представлена схема триггера. Устройство содержит четыре основных одноступенчатых триггера 1-, вспомогательный одноступенчатый три)- гер 5, блок 6 переключения, четыре трехвходовых элемента И 7-10, комммутирующих сигналы разрешения и сигналы выбора разрешения. Все четыре основных триггера 1-4 выполнены по схеме однотактного 0-триггера, каждый на двух -логических элементах (ЗИ-2И) ИЛИ-НЕ. На входы триггера 1 подается по шине 11 входная информация, по первой тактовой шине 12 - инверсный тактовый сигнал, с выхода 13 элемента И 7 сигнал разрешения работы первого основного триггера. На входы триггера 2 подаются: по информационной шине 14 - входная информация, по тине 12 - тактовый сигнал, с выхода.15 элемента И 8 - сигнал разрешения работы триггера 2. На входы триггера 3 подаются: по информационной шине 16 входная информация, по второй тактовой шине 17 инверсный второй тактовый сигнал, с выхода 18 элемента И 9 - сигнал разрешения работы триггера 3. На входы триггера 4 подаются: по информационной шине 19 - входная информация, по шине 17 7 второй тактовый сигнал, с выхода 20 элемента И 10 - сигнал разрешения работы триггера 4. Каждый основной триггер имеет входы установки в ноль и в единицу. На входы установки триггеров 1 и 2 подаются с выходов 21 и 22 сигналы установки в ноль и единицу.На входы установки триггеров 3 и 4 подаются с выходов 23 и 24 сигналы установки в ноль и единицу. Вспомогательный триггер 5 выполнен по схеме однотактного D-триггера на двух логических элементах (ЗИ-ЗИ-ЗИ-ЗИ-2И) ИЛИ-НЕ. На первую группу входов поданы: с выхода 25 триггера 1 - сигнал триггера 1, с шины 12 - первый тактовый сигнал, с выхода 13 - сигнал разрешения работы триггера 1. Ца вторую группу входов поданы: с выхода 26 триггера 2 - сигнал триггера 2, инверсный первый тактовый сигнал, с выхода 15 сигнал разрешения рабо ты триггера 2. На третью группу вхо.дов поданы: с выхода 27 - сигнал триггера 3 по шине 17 - второй тактовый сигнал, с выхода 18 - сигнал р решения работы триггера 3. На четверную группу входов поданы: с выхода 28 триггера - сигнал триггера ky инверсный второй тактовый сиг нал, с выхода 20 элемента 10 - сигнал разрешения работы триггера . На входы установки в ноль и единицу с выходов 29 и 30 блока 6 подаются сиг налы установки в ноль и единицу. Вспомогательный триггер 5 имеет прямой выход 31 и инверсный выход 32, к торые являются выходами триггера. Бл 6 переключения выполнен на четырех логических элементах И-НЕ , двух логических элементах И 2 и элементе ИЛИ-НЕ 2. На входы блока 6 по управляющим шинам 33, , 35 и 36 подаются: соответственно первый сигнал разрешения, второй сигнал разрешения первый сигнал выбора разрешения, вто 66 рой сигнал выбора разрешения, сигнал входной информации триггера 2 по шине 1, сигнал входной информации триггера 3 по шине 16. Тактовые и управляющие сигналы инвертируются инверторами 37. Функционирование триггера описывается таблицей переходов. Триггер имеет два независимых тактовых входа, первый тактовый вход определяетработу группы, состоящей из триггера 1, триггера 2 и вспомогательного триггера 5, второй тактовый од определяет работу группы, состоящей из триггера 3, триггера и вспомогательного триггера 5. Если значение первого сигнала выбора разрешения по шине 35 равно О, а значение второго сигнала выбора разрешения по шине Зб равно 1, то в зависимости от состояния сигналов разрешения по шинам 33 и 3 в той или иной комбинации работают триггер 3. триггер k и вспомогательный триггер 5, а триггеры 1 и 2 находятся в состоянии Память. .Если значение сигнала по шине 33 равно 1-, а значение сигнала по шине Зб равно О, то в зависимости от состояния сигналов разрешения по шинам 33 и 3 в той или иной последовательности работают триггер 1, триггер 2 и вспомогательный триггер 5, а 3 и триггеры находятся в состоянии Память.

8

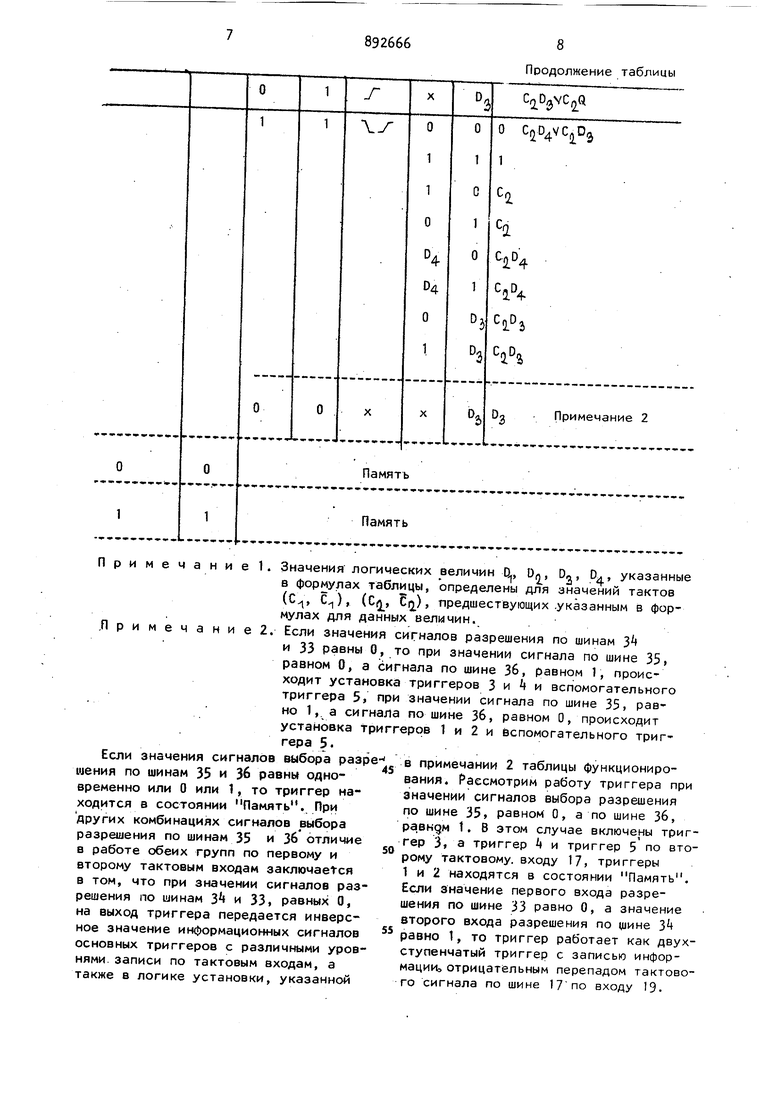

892666 Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерное устройство | 1981 |

|

SU966856A1 |

| Триггерное устройство | 1980 |

|

SU991579A1 |

| Триггерное устройство | 1981 |

|

SU970647A1 |

| Распределитель | 1982 |

|

SU1051710A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2005 |

|

RU2282306C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

Примечание. Значения логических величин Ц, 0,, Dj, D, указанные

в формулах таблицы, определены для значений тактов (С.,, Ц), (С, о), предшествующих .указанным в формулах для данных величин. ,Примечание2. Если значения сигналов разрешения по шинам 3

и 33 равны О, то при значении сигнала по шине 35 равном О, а сигнала по шине 36, равном 1, происходит установка триггеров 3 и и вспомогательного триггера 5, при значении сигнала по шине 35, раано 1,. а сигнала по шине 36, равном О, происходит

установка триггеров 1 и 2 и вспомогательного триггера 5.

Если значения сигналов выбора разре

шения по шинам 35 и 36 равны одновременно или О или 1, то триггер находится в состоянии Память. При других комбинациях сигналов выбора разрешения по шинам 35 и Зб отличие в работе обеих групп по первому и второму тактовым входам зaключaetcя в том, что при значении сигналов разрешения по шинам 3 и 33 равных О, на выход триггера передается инверсное значение информационных сигналов основных триггеров с различными уровнями, записи по тактовым входам, а также в логике установки, указанной

в примечании 2 таблицы функционирования. Рассмотрим работу триггера при значении сигналов выбора разрешения по шине 35 равном О, а по шине Зб, paBHQM t. В этом случае включены триггер 3, а триггер и триггер 5 по второму тактовому, входу 17, триггеры 1 и 2 находятся в состоянии Память. Если значение первого входа разрешения по шине 33 равно О, а значение второго входа разрешения по шине равно 1, то триггер работает как двухступенчатый триггер с записью информации, отрицательным перепадом тактового сигнала по шине 17по входу 19. Если значение первого входа разрешения по шине 33 равно 1, а значение второго входа разрешения по шине 3 равно О, то триггер работает как двухступенчатый триггер с записью ин формации положительным перепадом вто рого тактового сигнала по шине 17 по входу 16, Если значения )B разрешения по шинам 33 и 3 1, то триггер осуществляет передачу информации по входам 19 и 16 без запоминания предыдущей информации.в триг гере 5 на время изменения уровня вто рого тактового сигнала по шине 17. В этом случае положительным уровнем второго тактового сигнала по шине 17 в триггер 5 передается информация из триггера 3, а отрицательным уровнем из триггера «. В зависимости от состояния информационных входов 19 и Тб на выходе триггера 31 по второму так товому сигналу по шине 17 можно полу чать константы О или 1, прямой или инверсный второй тактовый сигнал С2 или CQ, функцию С(5л при значении си (о.), равном О, функнала по шине 16 .цию рфСо. при значении- сигнала по шине 16 CD), равном.1, функцию при значении сигнала 19 (Од), равном О, функцию О) при значении сигнала (D) .равном 1 .Значение сигнала 19 (04 определяется для момента перехода второго тактового сигнала 17 из высокого уровня в низкий, а значение сигнала по шине 16 (Dj) определяется для момента перехода второго тактового сигнала из низкого .уровня в высокий. Предлагаемый триггер может выполнять четыре различные функции. Мали-. чие двух независимых тактовых входов делает возможным комбинировать синх ронные и асинхронные режимы при работе на один выход в каждом разряде. Рассмотрим возможности переключения и запоминания информации при -различных комбинациях режимов. Синхронно-синхронный режим. На первый и второй тактовые входы 12 и 17 поданы различные тактовые сигналы, а сам триггер находится в цепи таких же триггеров и выполняет по обоим тактовым входам синхронные функ ции. При этом возможны следующие варианты переключений. В а р и а н т 1. Переключение по конечной информации первого.режима во второй режим, например, при сигналах первого режима по шинам 3 33. 6 и сигналах выбора разрешений по шинам 35, Зб (1,0). Для переключения следует произвести следующие действия:.выход из режима может быть произведен при высоком или низком уровне на тактовой шине 12, установить внешнюю память, сигналы по шинам 35, 36 (00 или 11), установить соответствующее значение сигналов по шинам З, 33 (01 или 10), установить значение сигналов по шинам 35 36 (01), причем значение второго тактового сигнала по шине 17 должно быть таким, чтобы в момент переключения не произошла запись информации во вспомогательный триггер из основного триггера вновь включенного режима. Если значения сигналов по шинам 3 и 33 в прежнем режиме соответствуют значениям этих сигналов в новом режиме, то внешнюю память можно не устанавливать, а сразу включить новый режим. Моменты переключения режимов должны отстоять от моментов изменения тактовых сигналов на время, превышающее время срабатывания триггера. После переключения режима при низком уровне контакта шине 12 данным образом в основном триггере прежнего режима будет храниться информация, котсграя появилась бы во вспомогательном триггере 5 при следующем такте первого тактового сигнала по шине 12. Если прсизвести переключение в прежний режим, то его можно начать с прежней информации, только один тактовый импульс как бы пропадает, а его роль выполняют сигналы переключения при переключении режимов. Вариант2. Чтобы при переключении из режима в режим записать во вспомогательный триггер 5 информацию, хранимую в основном триггере нового режима, нужно произвести переключение при таком уровне второго тактового сигнала по шине 17, при котором происходит перепись информации во вспомогательный триггер 5 из основного триггера данного режима. ВариантЗ. Если при переключении режимов необходимо запоминать конечную информацию прежнего режима, которая находится во вспомогательном триггере 5, в обоих основных триггерах нужно образовать режим запоминания .по информационному входу, при котором основные триггеры, работающие с данным тактовым сигналом, будут установлены в состояние вспомогательного триггера 5,. Например, если этим входом будет шина триггера 2, то по шине Ц (Dr) нужно организовать запоминание по следующей формуле (р ) XVQX, где X - сигнал переключения шины l., при X (1) на шину 1 передается информация данного режима, при Х(0) на шину предается информация инверсного выхо да триггера 32, в результате чего происходит установка триггеров 1 и 2 в состояние триггера 5. Последовательность переключений будет выглядеть следующим образом: после получения конечной информации во вспомогательном триггере 5 устано ить сигналы по шинам 3,33 (00) и сигнал X (ОО) при значении первого тактового сигнала по шине 12, соответствующем памяти вспомогательного триггера 5, произойдет установка триггеров 1 и 2 в состояние триггера 5, установить вне нюю память, сигналы по шинам 35,Зб (00 или 11), установка, соответствующего режима согласно переходам, опи санным в П.1 и 2 для переключения в новый режим. Если нет необходимости в другом основном триггере, работающем по вто рому тактовому сигналу, то можно не устанавливать режим внешней памяти, а сразу включить необходимый режим при соответствующем уровне такта. Асинхронно-синхронный режим. Конкретизируя рассмотрим, например, .асинхронный реверсивный счетчик, име ющий цепь сдвига вправо и влево. По первому тактовому сигналу по шине 12 производится сдвиг, а по второ му тактовому сигналу по шине 17 производится асинхронный счет реверсивного счетчика. Для организации асинх ронного счета нужно объединить шины 16, 19 и 32, а на второй тактовый вход подать выходной сигнал предыдущего каскада по шинам 31 или 32. Включение асинхронного режима может быть в следующих вариантах: В а р и а нт 1. Включение режима счета по конечной информации во вспо могательном триггере. Последовательность установки следующая: установка внешней памяти, сигналы по шинам 35 Зб (00 или 11), установка сигналов по шинам 3, 33 (00)t установка режи ма асинхронного счета, сигналы по ши нам 35, 36 (01)установка направления счета, сигналы по шинам 3, 3 6 (01 ИЛИ 10), счетчик готов к счету, так как вспомогательные триггеры при любом значении тактового сигнала на входе триггера останутся в прежнем значении . Если в синхронной части есть цепь памяти по входу И ( и по формуле и нужно.оставлять в памяти синхронной части конечную информацию,то последовательность следующая: установка сигналов по шинам 3,33 (00), установка асинхронного режима, сигналы по шинам 35, 36 (01), установка направления счета, сигналы по шинам 3, 33 (01 или 10), счетчик готов к счету. В а р и а нт 2, Включение режима счета по информации, хранимой в основных триггерах счетной цепи. При таком включении асинхронной счетной цепи информация (в обоих основных триггерах) в данном случае в триггерах 3 и 4 должна быть одинаковой, в ином случае правильной установки не произойдет. Последовательность установки следующая: установка внешней памяти, сигналы по шинам 35, 36 (00 или 11), установка сигналов по шинам , 33 (11) во всех триггерах цепи и установка режима асинхронного счета, сигнал по шинам 35, 36 (01) в цепи через один триггер, так как могут быть изменения выходных уровней триггеров в связи с записью информации во вспомогательный триггер из какого-либо, в данном случае из третьего или четвертого основных триггеров, установка режима памяти по входу 16 на включенных через один триггерах счетной цепи, сигналы по шинам 3,33(00), при этом произойдет восстановление информации в основных триггерах по информации вспомогательного триггера, установка сигналов по шинам 35,36 (01) в остальных триггерах счетной цепи, при этом произойдет окончательная установка информации памяти асинхронной счетной цепи во всех вспомогательных триггерах, установка направления счета, сигналы по шинам З, 33 (01 или 10), счетная цепь готова к работе. ВариантЗ. Выход может быть с запоминанием конечной информации в обоих основных триггерах счетной цепи и без запоминания конечной информации. Вь1ход с запоминанием конечной ин- . формации можно произвести в следующе|| последовательности: установка режима памяти по шине 16, сигналы по шинам З, 33(00), при этом в оба основных триггера счетной цепи заносится информация вспомогательного триггера, установка режима внешней памяти, си налы по шинам 35, 36 (00 или-11), установка режима синхронной работы, сигналы по шинам 35, 36 (10) и установка соответствующих сигналов по шинам 3, 33 в зависимости от условий входа в синхронный режим. При выходе из асинхронного режима без запоминания конечной информации производится сразу вход в синхронный режим по заданным условиям. Асинхронно-асинхронный режим. Если оба тактовых входа объединены в асинхронные цепи, то переход из режима в режим можно осуществить по правилам, описанным в асинхронно-син хронном режиме. Процедура перехода в другой асинхронный режим по конечной информации прежнего режима с запоминанием конечной информации в основных триггерах прежнего режима выглядит так: установка памяти по шине 16, сигналы по шинам 3,33 (00)., изменение режима, сигналы по шинам 35, 36 (Ю), включение соответствующего направления счета, сигналы по шинам 3, 33 (01 или 10), цепь гото ва к счету. Переключение в другой асинхронный режим по информации, хранимой в осно ных триггерах первой счетной цепи, производится также, как описано в п.2, описанного ранее асинхронно-син f pOHHoro режима.Триггера, работающие со вспомогательным триггером по первому тактовому сигналу 12 и по второ му тактовому сигналу по шине 17 по своим функциональнь1м возможностям ра ноправны, поэтому комбинации режимов могут быть различными. Наибольший технико-экономический эффект предлагаемый триггер может дать при реализации в виде интеграль ной микросхемы, что упростит построение сложных устройств, например асин ронных и синхронных реверсивных счет чиков, имеющих цепь сдвига вправо и влево, счетчиков и делителей с переменным коэффициентом счета и деления , других различных комбинированных устройств, выполняющих до четыре функций, уменьшит их габариты и расширит возможности для комбинирования функций. Использование триггера для построения микросхем СИС может увеличить количество выполняемых ими функций и расширить их.универсальность. Формула изобретения Триггер, содержащий два основных и один вспомогательный триггера, прямой и инверсный выходы, счетный вход первого основного триггера через инвертор соединен с первой шиной тактового сигнала, а информационный вход с первой информационной шиной, информационный вход второго основного триггера соединен со второй информационной шиной, первый счетный вход вспомогательного триггера соединен с первой шиной тактового сигнала, а первый информационный вход соединен с выходом первого основного триггера, отличающийся тем, что, с целью расширения функциональных возможностей, в триггер введены третий основной триггер, счетный вход которого через инвертор соединен со второй шиной тактового сигнала, а информационный вход соединен с третьей информационной шиной, четвертый основной триггер, счетный вход которого соединен со второй шиной тактового сигнала, а информационный вход соединен с четвертой информационной шиной, четыре логических элемента И, блок переключения, четыре шины управления, первая шина управления соединена с первыми входами первого и третьего элементов И и с первым входом блока переключения, вторая ши.на управления соединена с первыми входами второго и четвертого элементов И и со вторым входом блока переключения, третья шина управления соединена со вторыми входами первого и второго элементов И, с третьим входом блока переключения и через инвертор со вторыми входами третьего и четвертого элементов И, четвертая шина управления соединена с третьими входами третьего и четвертого элементов И, с четверым входом блока переключения и через инвертор с третьими входами первого и второго элементов И, пятый и шестой входы блока ереключения соединены соответствено со второй и третьей информациоными шинами, а его первый и второй ыходы соединены со входами установки в ноль и единицу первого и второго основных триггеров, второй и третий выходы со входами установки в ноль и единицу третьего и четвертого триггеров,а пятый и шестой выходы со входами установки в ноль и единицу вспомогательного триггера, выходы первого, второго, третьего и четвертого элементов И соединены с управляющими входами соответственно первого, второго, третьего и четвертого основных триггеров и с управляющими входами вспомогательного триггера первым, вторым, третьим и четвертым соответственно, второй, третий и четвертый информационные входы вспомогательного триггера

соединены с выходами соответственно второго, третьего и четвертого основных триггеров, первая шина тактового сигнала соединена через инвертор со вторым счетным входом вспомогательного триггера, вторая шина тактового сигнала соединена с третьим и через инвертор с четвертым счетными входами вспомогательного триггера.

Источники информации, принятые во внимание при экспертизе

Советское радио, 1975, с. 77-78.

Авторы

Даты

1981-12-23—Публикация

1980-04-16—Подача