Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации.

Цель изобретения - повышение быст- с родействия за счет уменьшения задерек выходных сигналов всех каналов до величины задержки выходного сигнала ервого канала по отношению к тактовому сигналу и расширение функцио- JQ альных возможностей за счет обеспеения возможности синхронизации произвольного числа входных сигналов одновременно.

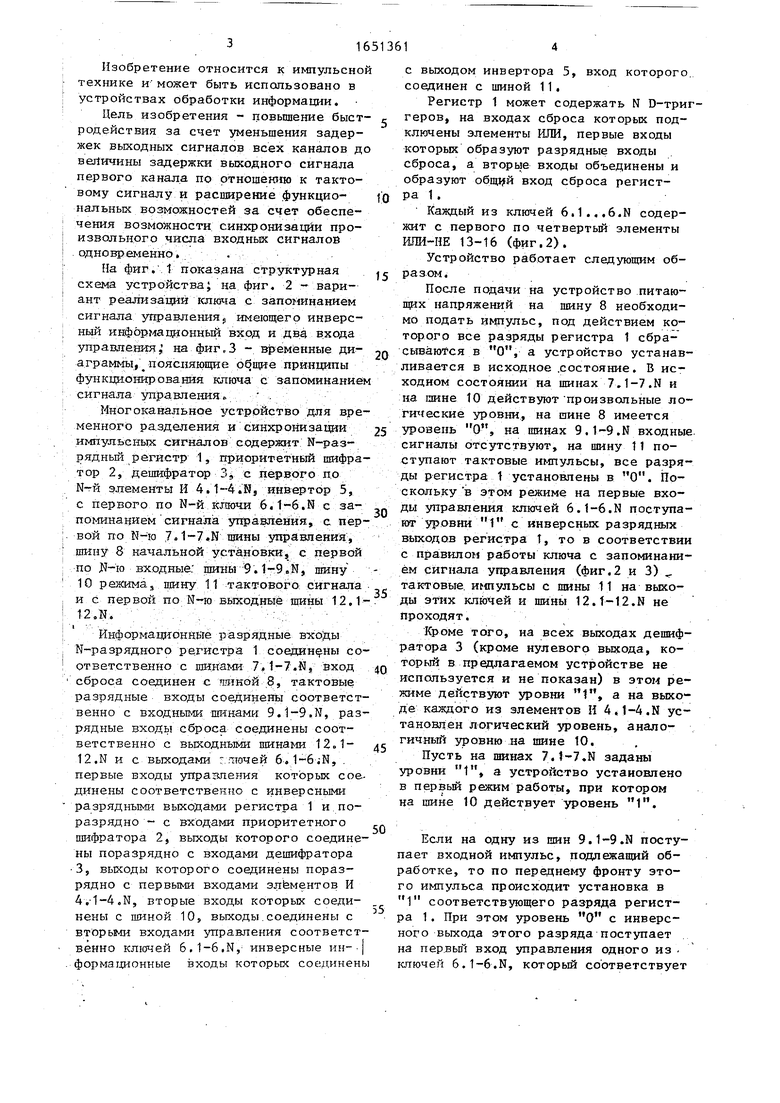

На фиг. 1 показана структурнаяjc

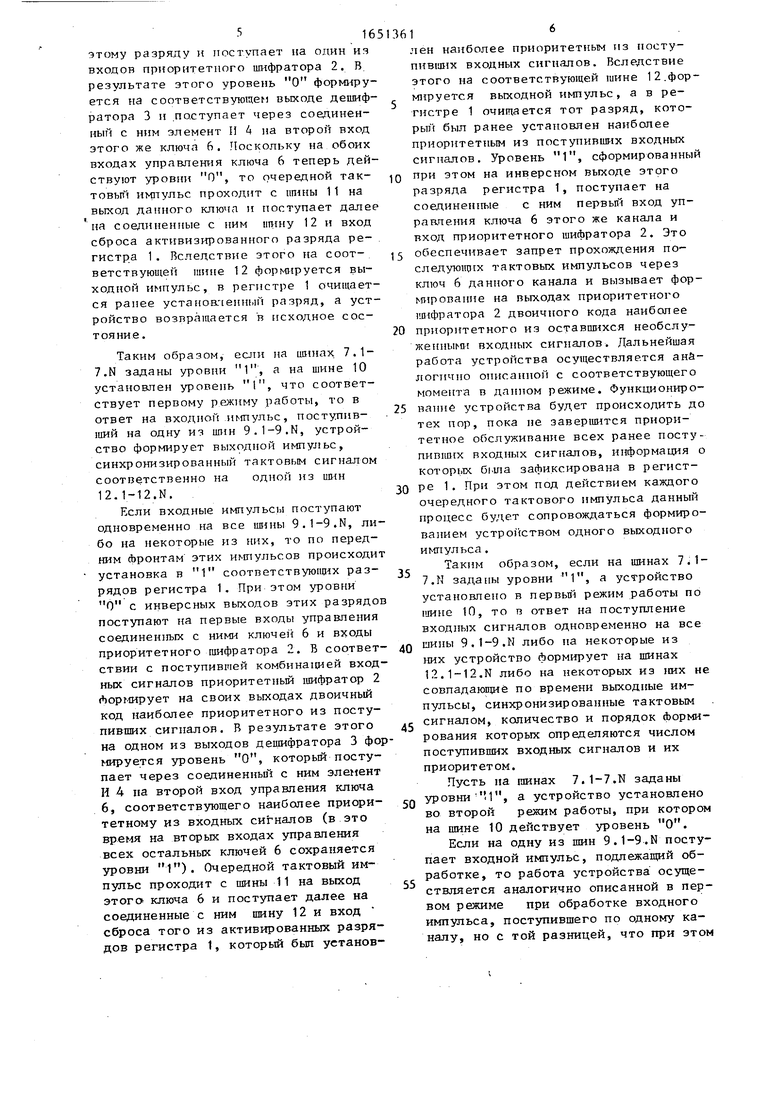

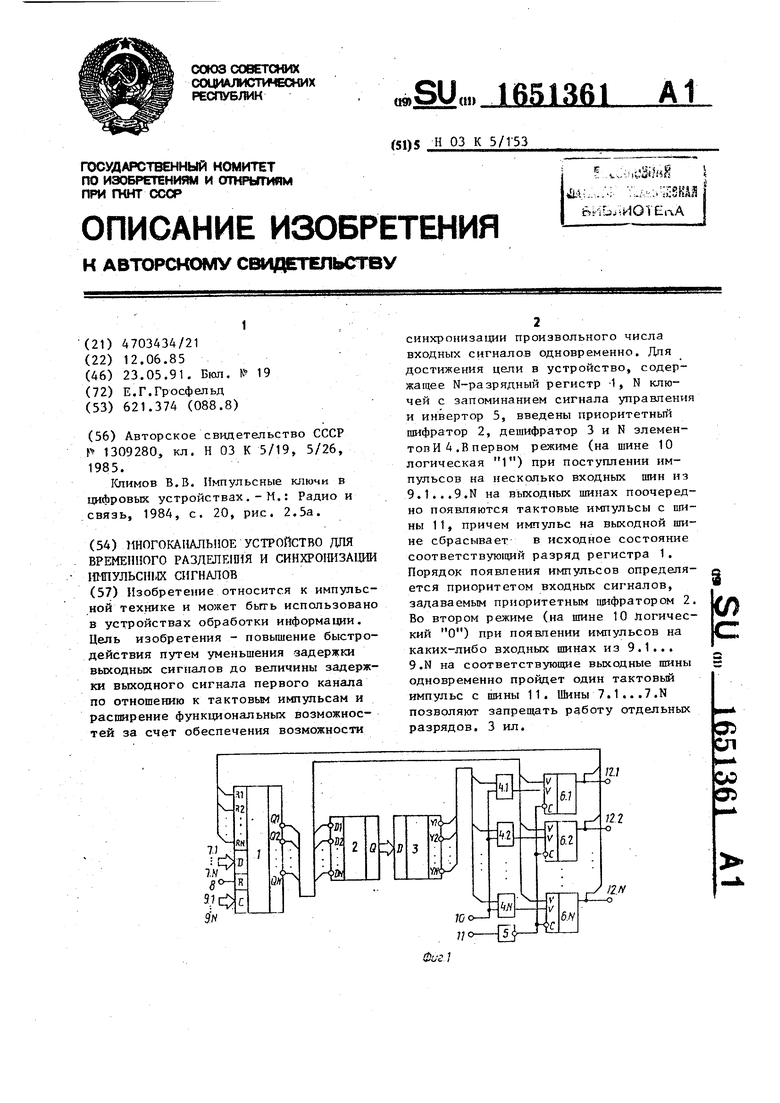

схема устройства; на фиг. 2 - вариант реализации ключа с запоминанием сигнала управления, имеющего инверсный информационный вход и два входа управления, на фиг.З - временные ди- п аграммы, поясняющие общие принципы функционирования ключа с запоминанием сигнала управления.

Многоканальное устройство для временного разделения и синхронизации 25 импульсных сигналов содержит N-раз- рядный регистр 1, приоритетный шифратор 2, дешифратор 3, с первого по N-й элементы И 4.1-4.Ы, инвертор 5, с первого по N-й ключи 6.1-6.R с за- , поминанием сигнала управления, с первой по N-ю 7.1-7«N щины управления, шину 8 начальной установки, с первой по J5-io входные шины 9.1-9.N, шину 10 режима, пину 11 тактового сигнала „ и с первой по N-ю выходные шины 12,1- 12.N.

Информационные разрядные входы N-разрядного регистра 1 соединены соответственно с шинами 7.1-7.и, вход /ю сброса соединен с чшкой 8, тактовые разрядные входы соединены соответственно с входными шинами 9.1-9.N, разрядные входы сброса соединены соответственно с выходными шинами 12.1- д5 12.N и с выходами -ночей 6.1-6;N, первые входы упразяения которых сое- динены соответственно с инверсными разрядными выходами регистра 1 и поразрядно - с входами приоритетного „. шифратора 2, выходы которого соединены поразрядно с входами дешифратора 3, выходы которого соединены поразрядно с первыми входами элементов И 4.1-4.N, вторые входы которых соеди- йены с шиной 10, выходы соединены с вторыми входами управления соответственно ключей 6.1-6.N, инверсные ин- | формационные входы которых соединены

с выходом инвертора 5, вход которого соединен с шиной 11.

Регистр 1 может содержать N D-триг геров, на входах сброса которых подключены элементы ИЛИ, первые входы которых образуют разрядные входы сброса, а вторые входы объединены и образуют общий вход сброса регистра 1 .

Каждый из ключей 6.1...6.N содержит с первого по четвертый элементы ИЛИ-НЕ 13-16 (фиг.2).

Устройство работает следующим образом.

После подачи на устройство питающих напряжений на шину 8 необходимо подать импульс, под действием которого все разряды регистра 1 сбрасываются в О, а устройство устанавливается в исходное .состояние. В исходном состоянии на шинах 7.1-7.N и иа шине 10 действуют произвольные логические уровни, на шине 8 имеется уровень Г0И, на шинах 9.1-9.N входные сигналы отсутствуют, на шину 11 поступают тактовые импульсы, все разряды регистра 1 установлены в О. Поскольку в этом режиме на первые входы управления ключей 6.1-6.N поступают уровни 1 с инверсных разрядных выходов регистра 1, то в соответствии с правилом работы ключа с запоминанием сигнала управления (фиг.2 и 3) .. тактовые импульсы с шины 11 на выходы этих ключей и шины 12.f-12.N не проходят.

Кроме того, на всех выходах дешифратора 3 (кроме нулевого выхода, который в предлагаемом устройстве не используется и не показан) в этом режиме действуют уровни 1, а на выходе каждого из элементов И 4.1-4.N установлен логический уровень, аналогичный уровню на шине 10.

Пусть на шинах 7.1-7.N заданы уровни 1, а устройство установлено в первый режим работы, при котором на шине 10 действует уровень 1.

Если на одну из шин 9.1-9.N поступает входной импульс, подлежащий обработке, то по переднему фронту этого импульса происходит установка в 1 соответствующего разряда регистра 1. При этом уровень О с инверсного выхода этого разряда поступает на первый вход управления одного из . ключей 6.1-6.N, который соответствует

этому разряду и поступает на один из входов приоритетного шифратора 2. В результате этого уровень О формируется на соответствующем выходе дешифратора 3 и поступает через соединенны с ним элемент И 4 на второй вход этого же ключа 6. Поскольку на обоих входах управления ключа 6 теперь действуют уровни О, то очередной тактовый импульс проходит с шины 11 на выход данного ключа и поступает далее на соединенные с ним тину 12 и вход сброса активизированного разряда регистра 1. Вследствие этого на соответствующей тине 12 формируется выходной импульс, в регистре 1 очищается ранее установленный разряд, а устройство возвращается в исходное состояние.

Таким образом, если на шинах 7.1- 7.N заданы уровни 1, а на шине 10 установлен уровень 1, что соответствует первому режиму работы, то в ответ на входной импульс, поступивший на одну из шин 9.1-9.N, устройство формирует выходной импульс, синхронизированный тактовым сигналом соответственно на одной из шин 12.1-12.N.

Если входные импульсы поступают одновременно на все шины 9.1-9.N, либо на некоторые из них, то по передним сЬронтам этих иг отульсов происходит установка в 1 соответствующих разрядов регистра 1. При этом уровни О с инверсных выходов этих разрядов поступают на первые входы управления соединенных с ними ключей 6 и входы приоритетного шифратора 2. В соответствии с поступившей комбинацией входных сигналов приоритетный шифратор 2 Аормирует на своих выходах двоичный код наиболее приоритетного из поступивших сигналов. В результате этого на одном из выходов дешифратора 3 формируется уровень О, который поступает через соединенный с ним элемент И 4 па второй вход управления ключа 6, соответствующего наиболее приоритетному из входных сигналов (в это время на вторых входах управления всех остальных ключей 6 сохраняется уровни 1). Очередной тактовый импульс проходит с шины 11 на выход этого ключа 6 и поступает далее на соединенные с ним шину 12 и вход сброса того из активированных разрядов регистра 1, который был установ

5

5

0

5

0

5

0

5

лен наиболее приоритетным из поступивших входных сигналов. Вследствие этого на соответствующей шине 12 формируется выходной импульс, а в регистре 1 очищается тот разряд, который был ранее установлен наиболее приоритетным из поступивших входных сигналов. Уровень 1, сформированный при этом на инверсном выходе этого разряда регистра 1, поступает на соединенные с ним первый вход управления ключа 6 этого же канала и вход приоритетного шифратора 2. Это обеспечивает запрет прохождения последующих тактовых импульсов через ключ 6 данного канала и вызывает формирование на выходах приоритетного шифратора 2 двоичного кода наиболее приоритетного из оставшихся необслуженными входных сигналов. Дальнейшая работа устройства осуществляется аналогично описанной с соответствующего момента в данном режиме. Функционирование устройства будет происходить до тех пор, пока не завершится приоритетное обслуживание всех ранее поступивших входных сигналов, информация о которых была зафиксирована в регистре 1. При этом под действием каждого очередного тактового импульса данный процесс будет сопровождаться формированием устройством одного выходного импульса.

Таким образом, если на шинах 7.1- 7.N заданы уровни 1, а устройство установлено в первый режим работы по шине 10, то в ответ на поступление входных сигналов одновременно на все шины 9.1-9.N либо на некоторые из них устройство Лормирует на шинах 12.1-12.N либо на некоторых из них не совпадающие по времени выходные импульсы, синхронизированные тактовым сигналом, количество и порядок Аорми- рования которых определяются числом поступивших входных сигналов и их приоритетом.

Пусть на тинах 7.1-7.N заданы уровни 1, а устройство установлено во второй режим работы, при котором на шине 10 действует уровень О.

Если на одну из шин 9.1-9.N поступает входной импульс, подлежащий обработке, то работа устройства осуществляется аналогично описанной в первом режиме при обработке входного импульса, поступившего по одному каналу, но с той разницей, что при этом

1651361

на выходах элементов И 4.1-4.N постоянно действуют уровни О.

Таким образом, если на шинах 7.1- 7.N заданы уровни 1, на шине 10 установлен уровень О, что соответствует второму режиму работы, то в ответ на входной импульс, поступивший на одну из шин 9.1-94N, устройство

формирует выходной импульс, синхрони- 10 на шинах 12.1-12.N, всегда равны длизированный тактовым сигналом, соот ветственно на одной из шин -12.1-12.N.

Если входные импульсы поступают одновременно на все-шины 9.1-9.N, либо на некоторые из них, то по передним фронтам этих импульсов происходит установка в 1 соответствующих разрядов регистра 1 . При этом уровни О с инверсных выходов этих разрядов поступают на соединенные с ними входы приоритетного шифратора 2 и первые входы управления ключей 6. Поскольку в этом режиме на вторых входах управления ключей 6.1-6.N постоянно действуют уровни О, то очередной тактовый импульс проходит с шины 11 одновременно на выходы всех тех ключей 6, на первых входах которых имеются ; уровни О, поступающие с соответствующих инверсных разрядных выходов регистра 1„ В результате этого импульсы, выделенные на выходах указанных ключей 6, поступают на,соединенные с ними шины 12 и разрядные входы сброса регистра 1. Это приводит к одновременному формированию на соответствующих шинах 12 выходных импульсов и обеспечивает полную очистку разрядов регистра 1, что вызывает установку устройства в исходное состояние.

Таким образом, если на шинах 7.1- 7.N заданы уровни 1, а устройство установлено во второй режим работы по шине 10, то в ответ на поступление входных сигналов одновременно на все шины 9.1-9.N либо на некоторые из них устройство формирует на шинах 12.1- 12.N либо на некоторых из них совпадающие по времени выходные импульсы, синхронизованные тактовым сигналом, причем общее число одновременно формируемых выходных сигналов определяется лишь только числом поступивших входных сигналов.

Следует отметить, что данное устройство позволяет осуществлять независимое маскирование любого из входных сигналов, либо произвольного числа входных сигналов одновременно, ис15

20

25

30

35

40

45

50

55

телыюсти тактового импульса независимо от синхронности сигналов на шинах 9.1-9.N и шине 11.

Техническими преимуществами устройства являются более высокое быстродействие при формировании выходных сигналов и расширенные функциональные возможности. Первое является следствием того, что в предлагаемом устройстве снижены по сравнению с известным задержки выходных сигналов относительно тактового сигнала, так как в известном устройстве задержки последовательно включенных ключей суммируются. Второе обусловлено наличием в нем возможности синхронизации произвольного числа входных сигналов одновременно.

Формула изобретения

Многоканальное устройство для временного разделения и синхронизации импульсных сигналов, содержащее с первой по входные шины, которые соединены с соответствующими тактовыми разрядными входами N-разрядного регистра, инверсные разрядные выходы которого соединены с входами управления соответственно с первого по N-й ключей с запоминанием сигнала управления, выходы которых соединены с соответствующими разрядными входами сброса N- разрядного регистра и соединены с соответствующими выходными шинами, а инверсный информационный вход ключа с запоминанием сигнала управления первого канала соединен с выходом инвертора, вход которого соединен с шиной тактового сигнала, отличающееся тем, что, с целью повышения быстродействия за счет уменьшения задержек выходных сигналов всех каналов до величины задержки выходного сигнала первого канала по отношению к тактовому сигналу при одновременном расширении функциональных возможностей за счет обеспечения возможности синхронизации произвольного

8

ключая этим их из процесса обработки. Для реализации данной функции необходимо подать уровень О на шину 7 того канала, входной сигнал которого требуется замаскировать.

Благодаря свойствам использованных в устройстве ключей 6.1-6.N длительности выходных импульсов, формируемых

5

0

5

0

5

0

5

0

5

телыюсти тактового импульса независимо от синхронности сигналов на шинах 9.1-9.N и шине 11.

Техническими преимуществами устройства являются более высокое быстродействие при формировании выходных сигналов и расширенные функциональные возможности. Первое является следствием того, что в предлагаемом устройстве снижены по сравнению с известным задержки выходных сигналов относительно тактового сигнала, так как в известном устройстве задержки последовательно включенных ключей суммируются. Второе обусловлено наличием в нем возможности синхронизации произвольного числа входных сигналов одновременно.

Формула изобретения

Многоканальное устройство для временного разделения и синхронизации импульсных сигналов, содержащее с первой по входные шины, которые соединены с соответствующими тактовыми разрядными входами N-разрядного регистра, инверсные разрядные выходы которого соединены с входами управления соответственно с первого по N-й ключей с запоминанием сигнала управления, выходы которых соединены с соответствующими разрядными входами сброса N- разрядного регистра и соединены с соответствующими выходными шинами, а инверсный информационный вход ключа с запоминанием сигнала управления первого канала соединен с выходом инвертора, вход которого соединен с шиной тактового сигнала, отличающееся тем, что, с целью повышения быстродействия за счет уменьшения задержек выходных сигналов всех каналов до величины задержки выходного сигнала первого канала по отношению к тактовому сигналу при одновременном расширении функциональных возможностей за счет обеспечения возможности синхронизации произвольного

числа входных сигналов одновременно, в него введены с первого по N-й элементы И, дешифратор, приоритетный шифратор, шина режима, шина начальной установки с первой по N-ю шины управления, которые соединены с соответствующими информационными разрядными входами N-разрядного регистра, вход сброса которого соединен с шиной начальной установки, инверсные разрядные выходы соединены с соответст- вуюгщми входами приоритетного шифратора, выходы которого поразрядно соединены с входами дешифратора, выхо-

ды которого соединены с первы- ми входами соответствующих элементов И, вторые входы которых соединены с шиной режима, а инверсные информационные входы с первого по N-й ключей с запоминанием сигнала управления соединены меяду собой, причем каадый ключ с запоминанием сигнала управления выполнен по входу управления с расширением по ИЛИ и при этом дополнительный вход управления каждого ключа с запоминанием сигнала управления соединен с выходом соответствующего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты | 1986 |

|

SU1368984A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Управляемый делитель частоты | 1987 |

|

SU1455388A2 |

| Устройство для контроля и сигнализации | 1990 |

|

SU1795494A1 |

| Устройство для диагностики неисправностей многоярусных пирамидальных схем | 1980 |

|

SU980084A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Многоканальное устройство для включения резервных радиостанций | 1991 |

|

SU1823139A1 |

| Счетчик импульсов | 1987 |

|

SU1497744A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1223234A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации. Цель изобретения - повышение быстродействия путем уменьшения задержки выходных сигналов до величины задержки выходного сигнала первого канала по отношению к тактовым импульсам и расширение функциональных возможностей за счет обеспечения возможности синхронизации произвольного числа входных сигналов одновременно. Для достижения цели в устройство, содержащее N-разрядным регистр 1, N ключей с запоминанием сигнала управления и инвертор 5, введены приоритетный шифратор 2, дешифратор 3 и N элементов И 4 .В первом режиме (на шине 10 логическая 1) при поступлении импульсов на несколько входных шин из 9.1...9.N на выходных шинах поочередно появляются тактовые импульсы с шины 11, причем импульс на выходной шине сбрасывает в исходное состояние соответствующий разряд регистра 1. Порядок появления импульсов определяется приоритетом входных сигналов, задаваемым приоритетным шифратором 2. Во втором режиме (на шине 10 логический О) при появлении импульсов на каких-либо входных шинах из 9.1... 9.N на соответствующие выходные шины одновременно пройдет один тактовый импульс с шины 11. Шины 7.1...7.N позволяют запрещать работу отдельных разрядов. 3 ил. зэ ел со 0

V

с

v v

Выход

ГLЛJ J JглJlJlJ JlJтлJ J J

ггтппп f

п

75

Выход О

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Климов В.В | |||

| Импульсные ключи в цифровых устройствах,-М.: Радио и связь, 1984, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-05-23—Публикация

1989-06-12—Подача