11

Изобретение относится к измерительной технике и может быть использовано при создании измерителей частотно-временных параметров сигнала на основе преобразователей моментов времени в код, в частности в измерителях временных интервалов и синхр нометрах.

Цель изобретения - повышение быстродействия и точности измерения за счет того, что интерполяцию производят в несколько циклов, причем в каждом последующем цикле происходит уточнение результата предыдущих циклов интерполяции.

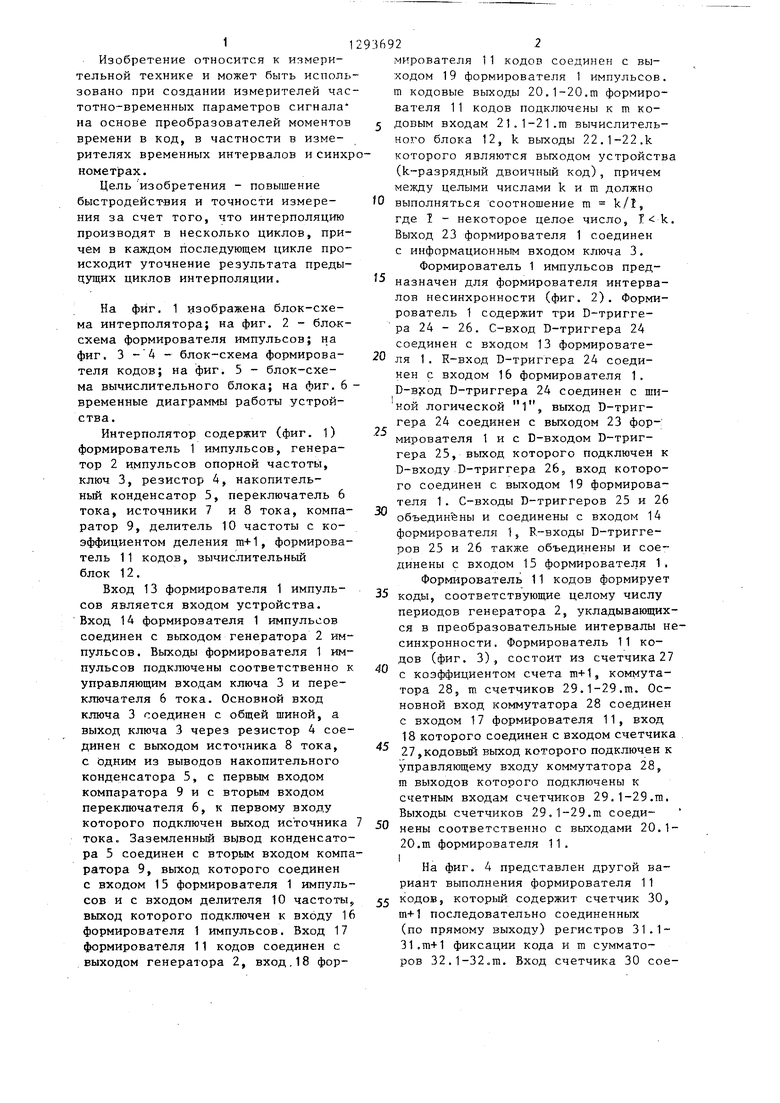

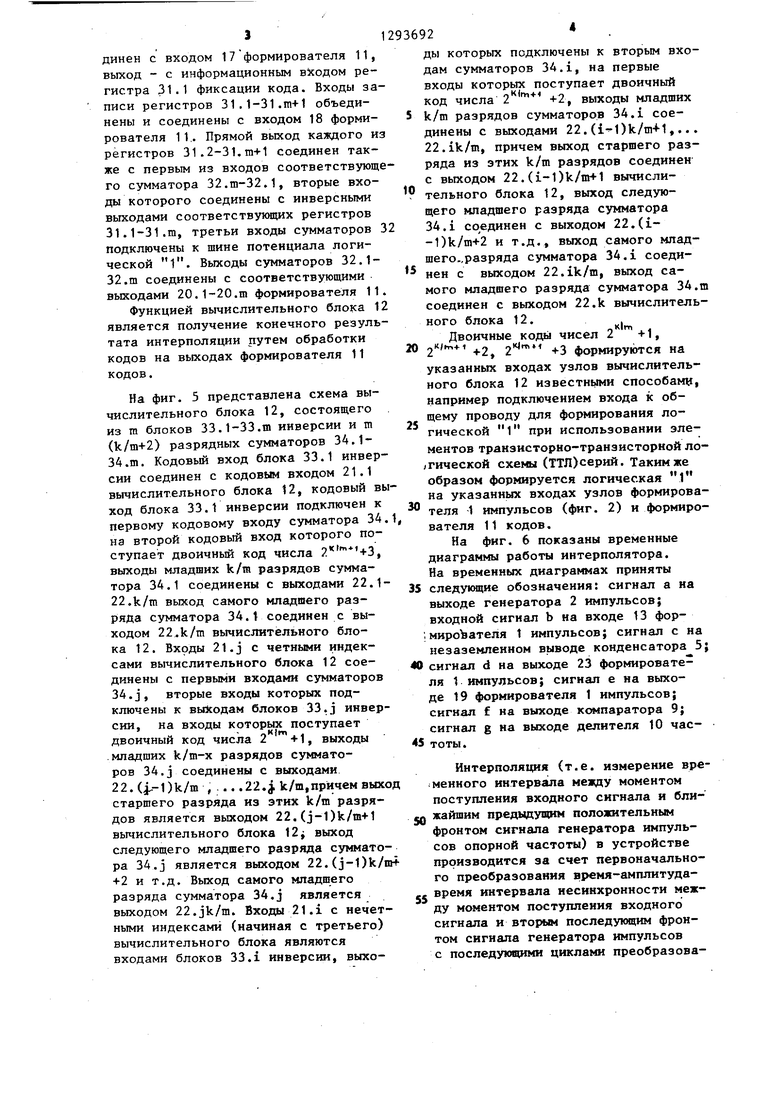

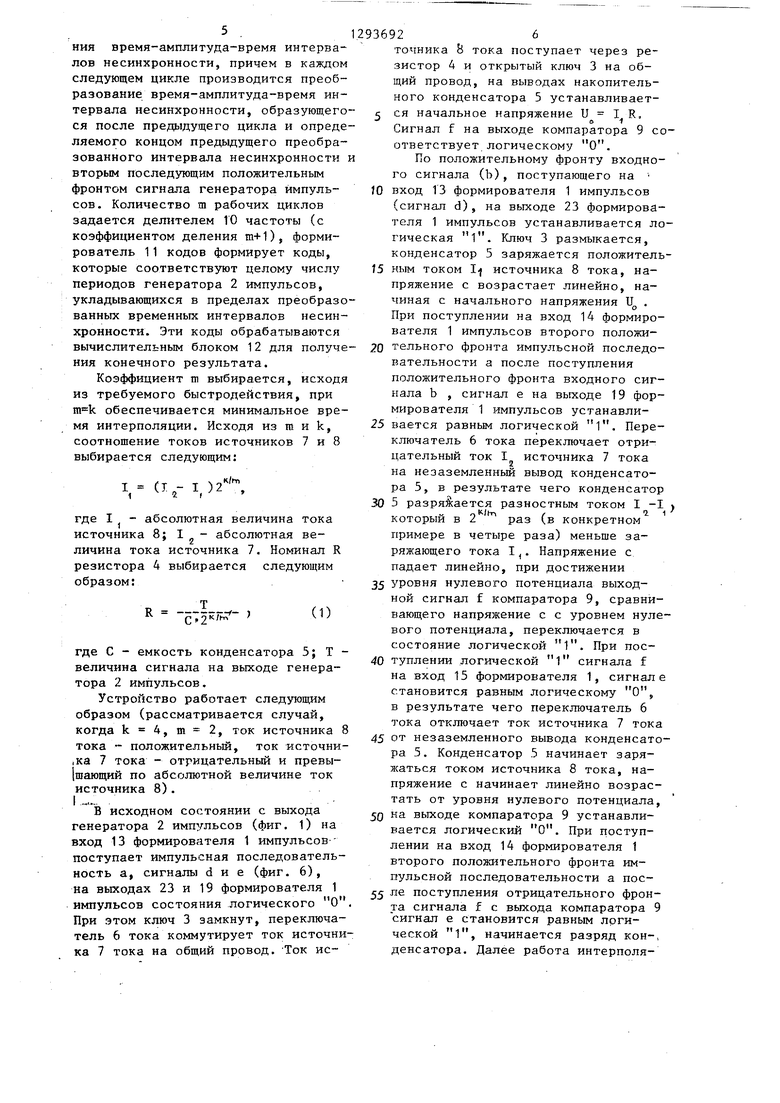

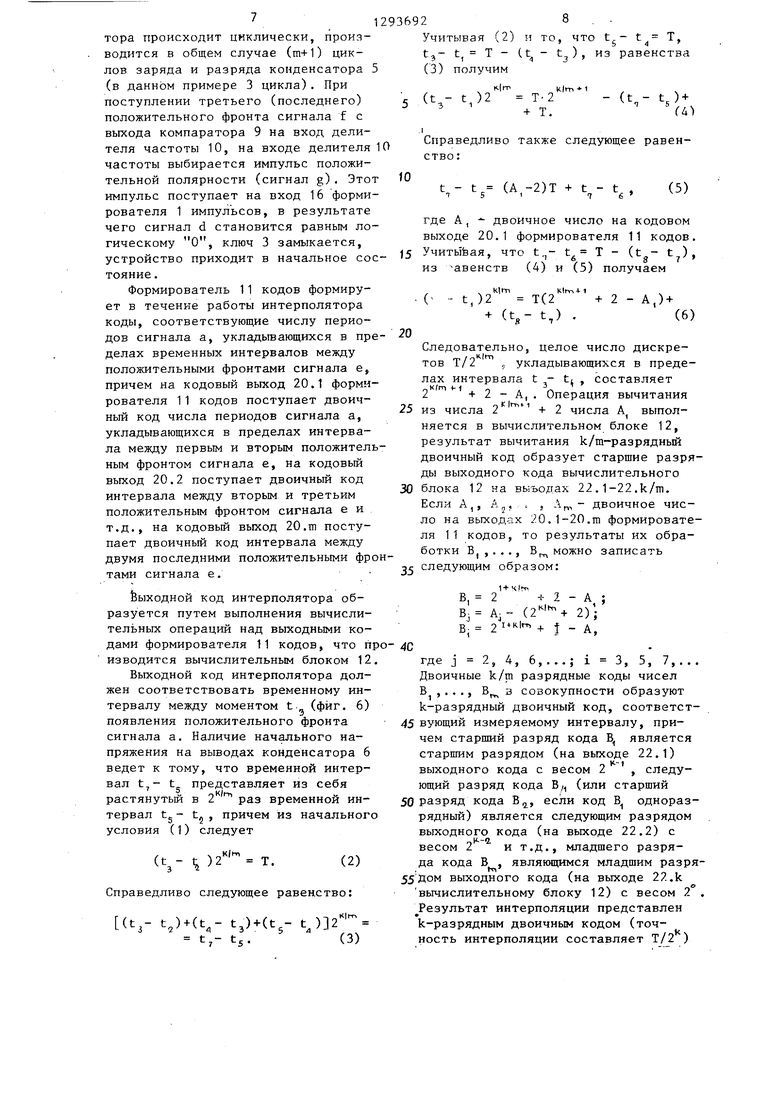

На фиг, 1 изображена блок-схема интерполятора; на фиг. 2 - блок- схема формирователя импульсов; на фиг. 3 - 4 - блок-схема формирователя кодов; на фиг. 5 - блок-схема вычислительного блока; на фиг. 6 временные диаграммы работы устройства.

Интерполятор содержит (фиг. 1) формирователь 1 импульсов, генератор 2 импульсов опорной частоты, ключ 3, резистор 4, накопительный конденсатор 5, переключатель 6 тока, источники 7 и 8 тока, компаратор 9, делитель 10 частоты с коэффициентом деления т+1, формирователь 11 кодов, вычислительный блок 12.

Вход 13 формирователя 1 импульсов является входом устройства. Вход 14 формирователя 1 импульсов соединен с выходом генератора 2 импульсов. Выходы формирователя 1 импульсов подключены соответственно к управляющим входам ключа 3 и переключателя 6 тока. Основной вход ключа 3 соединен с общей шиной, а выход ключа 3 через резистор 4 соединен с выходом исто 1ника 8 тока, с йдним из выводов накопительного конденсатора 5, с первым входом компаратора 9 и с вторым входом переключателя 6, к первому входу которого подключен выход источника тока о Заземленный вывод конденсатора 5 соединен с вторым входом компаратора 9, выход которого соединен с входом 15 формирователя 1 импульсов и с входом делителя 10 частоты. выход которого подключен к входу 16 формирователя 1 импульсов. Вход 17 формирователя 11 кодов соединен с выходом генератора 2, вход.18 фор

22

мирователя 11 кодов соединен с выходом 19 формирователя 1 импульсов, m кодовые выходы 20.1-20.m формирователя 11 кодов подключены к m кодовым входам 21.1-21.ni вычислительного блока 12, k выходы 22.1-22.k которого являются выходом устройства (k-разрядный двоичный код), причем между целыми числами k и m должно выполняться соотношение m k/I, где 1 - некоторое целое число, . Выход 23 формирователя 1 соединен с информационным входом ключа 3.

Формирователь 1 импульсов предназначен для формирователя интервалов несинхронности (фиг. 2). Формирователь 1 содержит три D-тригге- ра 24 - 26. С-вход D-триггера 24 соединен с входом 13 формирователя 1. R-вход D-триггера 24 соединен с входом 16 формирователя 1. D-вход D-триггера 24 соединен с ши- кой логической 1, выход D-триггера 24 соединен с выходом 23 фор- мирователя 1 и с D-входом D-триггера 25, выход которого подключен к D-входу D-триггера 26, вход которого соединен с выходом 19 формирователя 1. С-входы D-триггеров 25 и 26 объединены и соединены с входом 14 формирователя 1, R-входы D-триггеров 25 и 26 также объединены и соединены с входом 15 формирователя 1. Формирователь 11 кодов формирует

коды, соответствующие целому числу периодов генератора 2, укладывающихся в преобразовательные интервалы несинхронности. Формирователь 11 кодов (фиг. 3), состоит из счетчика 27 с коэффициентом счета m+l, коммутатора 28, m счетчиков 29.1-29.т. Основной вход коммутатора 28 соединен с входом 17 формирователя 11, вход 18 которого соединен с входом счетчика 27,кодовый выход которого подключен к управляющему входу коммутатора 28, m выходов которого подключены к счетным входам счетчиков 29.1-29.то. Выходы, счетчиков 29.1-29.m соединены соответственно с выходами 20.1- 20.m формирователя 11.

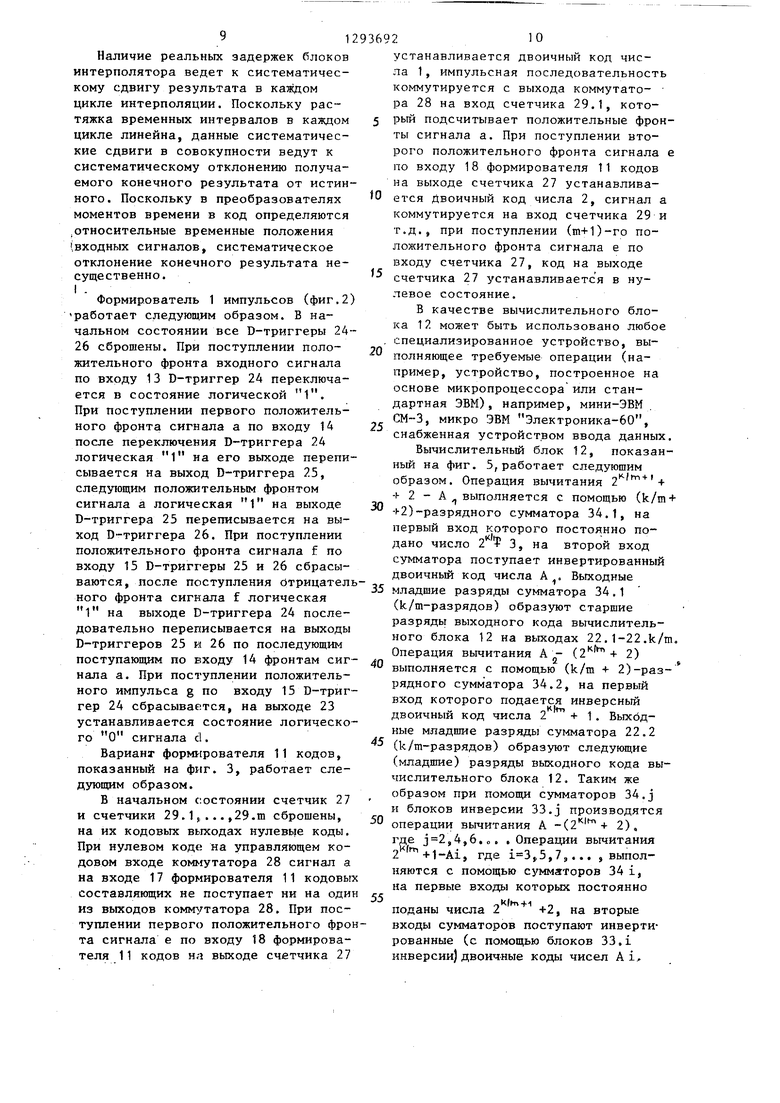

На фиг. 4 представлен другой вариант выполнения формирователя 11 кодов, который содержит счетчик 30, т+1 последовательно соединенных (по прямому выходу) регистров 31.1- 31.m+l фиксации кода и m сумматоров 32.1-32.га. Вход счетчика 30 сое

3

динен с входом 17 формирователя 11, выход - с информационным входом регистра 31.1 фиксации кода. Входы записи регистров 31.1-31.т+1 объединены и соединены с входом 18 формирователя 1 1.. Прямой выход каждого и регистров 31.2-31.т+1 соединен также с первым из входов соответствующго сумматора З2.т-32,1, вторые входы которого соединены с инверсными выходами соответствующих регистров 31.1-31.т, третьи входы сумматоров подключены к шине потенциала логи

ческой 1. Выходы сумматоров 32.1- 32.m соединены с соответствующими выходами 20.1-20.т формирователя 11. Функцией вычислительного блока 12 является получение конечного результата интерполяции путем обработки кодов на выходах формирователя 11 кодов.

На фиг. 5 представлена схема вычислительного блока 12, состоящего из га блоков 33.1-33.тп инверсии и m (k/m+2) разрядных сумматоров 34.1- 34.т. Кодовый вход блока 33.1 инверсии соединен с кодовым входом 21.1 вычислительного блока 12, кодовый выход блока 33.1 инверсии подключен к первому кодовому входу сумматора 34. на второй кодовый вход которого поступает двоичный код числа ., выходы младших k/m разрядов сумматора 34.1 соединены с выходами 22.1- 22.k/m выход самого младшего разряда сумматора 34.I соединен с выходом 22.k/m вычислительного блока 12. Входы 21.j с четными индексами вычислительного блока 12 соединены с первыми входами сумматоров 34.J, вторые входы которых подключены к вы1содам блоков 33.j инверсии, на входы которых поступает двоичный код числа 2 +1, выходы младших k/m-x разрядов сумматоров 34.j соединены с выходами 22.(4.-1)k/m , .. .22.J k/m,причем выхо старшего разряда из этих k/m разрядов является выходом 22.(j-1)k/m+1 вычислительного блока 12j выход следующего младшего разряда сумматора 34. j является выходом 22. (j-1)k/iiH +2 и т.д. Выход самого младшего разряда сумматора 34.j является выходом 22.jk/m. Входы 21.i с нечетными индексами (начиная с третьего) вычислительного блока являются входами блоков 33.1 инверсии, выходы которых подключены к вторым входам сумматоров 34.1, на первые входы которых поступает двоичный код числа 2 -t-2, выходы младших k/m разрядов сумматоров 34.1 соединены с выходами 22. ),... 22.ik/m, причем выход старшего разряда из этих k/m разрядов соединен с выходом 22.(i-1)k/m+1 вычислительного блока 12, выход следующего младшего разряда сумматора 34.1 соединен с выходом 22.(1- -1)k/m+2 и т.д., выход самого млад- щего.,разряда сумматора 34.1 соединен с выходом 22.ik/m, выход самого младшего разряда сумматора 34.m соединен с выходом 22.k вычислительного блока 12.

. гг, .

Двоичные кода чисел 2 +1,

2«/н,1 +2,

2K) 2 формируются на

25

30

указанных входах узлов вычислительного блока 12 известными способами, например подключением входа к общему проводу для формирования логической 1 при использовании элементов транзисторно-транзисторной ло /гической схемы (ТТЛ)серий. Таким же образом формируется логическая 1 на указанных входах узлов формирователя 1 импульсов (фиг. 2) и формирователя 11 кодов.

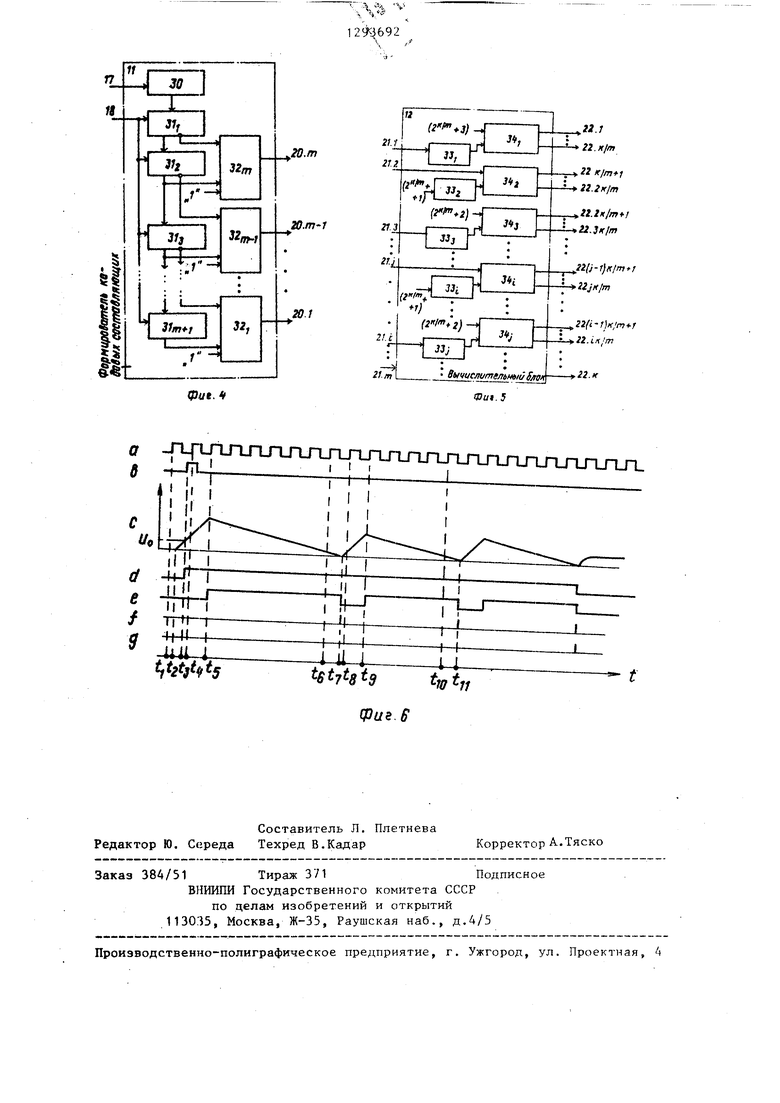

На фиг. 6 показаны временные диаграммы работы интерполятора. На временных диаграммах приняты

35 следукнцие обозначения: сигнал а на выходе генератора 2 импульсов; входной сигнал b на входе 13 фор- ;мироЪателя 1 импульсов; сигнал с на незаземленном выводе конденсатора 5

40 сигнал d на выходе 23 формирователя 1 импульсов; сигнал е на выходе 19 формирователя 1 импульсов; сигнал f на выходе ксмпаратора 9; сигнал g на выходе делителя 10 час45 тоты.

Интерполяция (т.е. измерение временного интервала меяду моментом поступления входного сигнала и бли- с0 жайшим предыдущим положительным фронтом сигнала генератора импульсов опорной частоты) в устройстве производится за счет первоначального преобразования время-амплитуда- время интервала несинхронности меж55

ду моментом постухшения входного сигнала и вторым последующим фронтом сигнала генератора импульсов с последующими циклами преобразования время-амплитуда-время интервалов несинхронности, причем в каждом следующем цикле производится преобразование время-амплитуда-время интервала несинхронности, образующегося после предыдущего цикла и определяемого концом предыдущего преобразованного интервала несинхронности вторым последующим положительным фронтом сигнала генератора импульсов. Количество m рабочих циклов задается делителем 10 частоты (с коэффициентом деления т+1), формирователь 11 кодов формирует коды, которые соответствуют целому числу периодов генератора 2 импульсов, укладывающихся в пределах преобразованных временных интервалов несинхронности. Эти коды обрабатываются вычислительным блоком 12 для получения конечного результата.

Коэффициент m выбирается, исходя из требуемого быстродействия, при обеспечивается минимальное время интерполяции. Исходя из m и k, соотношение токов источников 7 и 8 выбирается следующим:

I, , I - абсолютная величина тока источника 8; 1 - абсолютная величина тока источника 7. Номинал R резистора 4 выбирается следующим образом:

R

(1)

где С - емкость конденсатора 5; Т - величина сигнала на выходе генератора 2 импульсов.

Устройство работает следующим образом (рассматривается случай, когда k 4, m 2, ток источника 8 тока - положительный, ток источни- ,ка 7 тока - отрицательный и превы- щающий по абсолютной величине ток источника 8). „,... .

В исходном состоянии с выхода

генератора 2 импульсов (фиг. 1) на вход 13 формирователя 1 импульсов поступает импульсная последовательность а, сигналы d и е (фиг. 6), на выходах 23 и 19 формирователя 1 импульсов состояния логического О При этом ключ 3 замкнут, переключатель 6 тока коммутирует ток источника 7 тока на общий провод. Ток ис936926

точника В тока поступает через резистор 4 и открытый ключ 3 на общий провод, на выводах накопительного конденсатора 5 устанавливает- с ся начальное напряжение U 1 R.

Сигнал f на выходе компаратора 9 соответствует логическому О.

По положительному фронту входного сигнала (Ь), поступающего на

(О вход 13 формирователя 1 импульсов (сигнал d), на выходе 23 формирователя 1 импульсов устанавливается логическая 1. Ключ 3 размыкается, конденсатор 5 заряжается положительJ5 ным током 1 источника В тока, напряжение с возрастает линейно, начиная с начального напряжения U , При поступлении на вход 14 формирователя 1 импульсов второго положи20 тельного фронта импульсной последовательности а после поступления положительного фронта входного сигнала b , сигнал е на выходе 19 формирователя 1 импульсов устанавли25 вается равным логической 1. Переключатель 6 тока переключает отрицательный ток I источника 7 тока на незаземленный вывод конденсатора 5, в результате чего конденсатор

30 5 разряжается разностным током I -I «Kftn .-11

который в 2 раз (в конкретном

примере в четыре раза) меньше заряжающего тока I,. Напряжение с падает линейно, при достижении 35 уровня нулевого потенциала выходной сигнал f компаратора 9, сравнивающего напряжение с с уровнем нулевого потенциала, переключается в

состояние логической 1

40 туплении логи11еской

При пос- 1 сигнала f на вход 15 формирователя 1, сигнале становится равным логическому О, в результате чего переключатель 6 тока отключает ток источника 7 тока

45 от незаземленного вывода конденсатора 5. Конденсатор 5 начинает заряжаться током источника 8 тока, напряжение с начинает линейно возрастать от уровня нулевого потенциала,

50 на выходе компаратора 9 устанавливается логический О. При цоступ- лении на вход 14 формирователя 1 второго положительного фронта импульсной последовательности а пос55 ле поступления отрицательного фронта сигнала f с выхода компаратора 9 сигнал е становится равным логической 1 денсатора.

, начинается разряд кон-, Далее работа интерполятора происходит циклически, производится в общем случае (т+1) циклов заряда и разряда конденсатора 5 (в данном примере 3 цикла). При поступлении третьего (последнего) положительного фронта сигнала f с выхода компаратора 9 на вход делителя частоты 10, на входе делителя 1 частоты выбирается импульс положительной полярности (сигнал g), Этот импульс поступает на вход 16 формирователя 1 импульсов, в результате чего сигнал d становится равным логическому О, ключ 3 замыкается, устройство приходит в начальное состояние .

Формирователь 11 кодов формирует в течение работы интерполятора коды, соответствующие числу периодов сигнала а, укладьгоающихся в пределах временных интервалов между положительными фронтами сигнала е, причем на кодовый выход 20.1 формирователя 11 кодов поступает двоичный код числа периодов сигнала а, укладывающихся в пределах интервала между первым и вторым положительным фронтом сигнала е, на кодовый выход 20.2 поступает двоичный код интервала между вторым и третьим положительным фронтом сигнала е и т.д., на кодовый вькод 20.m поступает двоичный код интервала между двумя последними положительными фротами сигнала е.

Ёыходной код интерполятора образуется путем выполнения вычислительных операций над выходными кодами формирователя 11 кодов, что про- изводится вычислительным блоком 12.

Выходной код интерполятора должен соответствовать временному интервалу между моментом t. (фиг. 6) появления положительного фронта сигнала а. Наличие начального напряжения на выводах конденсатора 6 ведет к тому, что временной интервал t,- t представляет из себя растянутый в раз временной интервал tj- t , причем из начального

следует

,к/т

условия (1)

( ) Т. (2) Справедливо следующее равенство:

t,).(t,4)(4- t. ts)2

(3)

Учитывая (2) и то, что

tfit. Т,

t, Т - (t - t ) , из равенства (3) получим

).2 + Т.

-

Справедливо также следующее равенство :

t.tj (А,-2)Т +

1

(5)

где А, двоичное число на кодовом выходе 20.1 формирователя 11 кодов. Учитывая, что t Т - (t- t), «-:, -апоиг-т п (4) и (5) получаем

из

авенств

Kim, Klrr,-n

- t,)2 Т(2+ 2 - А,) +

+ (t,- t,) ,(6)

20

Следовательно, целое число дискрегр

тов Т/2 5 укладывающихся в пределах интервала + 2 - А

Ч-

составляет

25 из числа 2

К|гт, 1

Операция вычитания + 2 числа А выполняется в вычислительном блоке 12, результат вычитания k/m-разрядный двоичный код образует старшие разряды выходного кода вычислительного 0 блока 12 на выводах 22.1-22.k/ni. Если А, AJ, , 5 Af,, - двоичное число на выходах 20.1-20.m формирователя 11 кодов, то результаты их обработки В.

1

Б можно записать

2 следующим образом:

24- 2 А- ( 2); 2 н

t - А,

где j 2, 4, 6, . ..; i 3, 5, 7,... Двоичные k/tn разрядные коды чисел

Б

Б 3 совокупности образуют

k-разрядный двоичный код, соответст- 45 вующий измеряемому интервалу, причем старший разряд кода В является старшим разрядом (на выходе 22.1) выходного кода с весом 2 , следующий разряд кода В/, (или старший 50 разряд кода В, если код В одноразрядный) является следующим разрядом

выходного кода (на выходе 22.2) с

тИ--а

весом / и т.д., младшего разряда кода В , являющимся младшим разря 55 дом выходного кода (на выходе 22.k вычислительному блоку 12) с весом 2° результат интерполяции представлен k-разрядным двоичн1)1м кодом (точность интерполяции составляет Т/2 )

Наличие реальных задержек блоков интерполятора ведет к систематическому сдвигу результата в каждом цикле интерполяции. Поскольку растяжка временных интервалов в каждом цикле линейна, данные систематические сдвиги в совокупности ведут к систематическому отклонению получаемого конечного результата от истинного. Поскольку в преобразователях моментов времени в код определяются ,относительные временные положения (входных сигналов, систематическое отклонение конечного результата несущественно.

Формирователь 1 импульсов (фиг.2) работает следующим образом. В начальном состоянии все D-триггеры 24- 26 сброшены. При поступлении положительного фронта входного сигнала по входу 13 D-триггер 24 переключается в состояние логической 1. При поступлении первого положительного фронта сигнала а по входу 14 после переключения D-триггера 24 логическая 1 на его выходе переписывается на выход D-триггера 25, следующим положительным фронтом сигнала а логическая 1 на выходе D-триггера 25 переписывается на выход D-триггера 26. При поступлении положительного фронта сигнала f по входу 15 D-триггеры 25 и 26 сбрасываются, после поступления отрицателного фронта сигнала f логическая 1 на выходе D-триггера 24 последовательно переписывается на выходы D-триггеров 25 и 26 по последующим поступающим по входу 14 фронтам сигнала а. При поступлении положительного импульса g по входу 15 Б-триг гер 24 сбрасывается, на выходе 23 устанавливается состояние логического О сигнала с1.

Вариант фopм tpoвaтeля 11 кодов, показанный на фиг. 3, работает следующим образом.

В начальном состоянии счетчик 27 и счетчики 29.11, ... ,29.1п сброщены, на их кодовых выходах нулевые коды. При нулевом коде на управляющем кодовом входе коммутатора 28 сигнал а на входе 17 формирователя 11 кодовы составляющих не поступает ни на оди из выходов коммутатора 28. При поступлении первого положительного фрота сигнала е по входу 18 формирователя 11 кодов на выходе счетчика 27

5

0

устанавливается двоичный код числа 1, импульсная последовательность коммутируется с выхода коммутато- ра 28 на вход счетчика 29.1, который подсчитывает положительные фронты сигнала а. При поступлении второго положительного фронта сигнала е по входу 18 формирователя 11 кодов на выходе счетчика 27 устанавливается Двоичный код числа 2, сигнал а коммутируется на вход счетчика 29 и т.д., при поступлении (т+1)-го положительного фронта сигнала е по входу счетчика 27, код на выходе счетчика 27 устанавливается в нулевое состояние.

В качестве вычислительного блока 12 может быть использовано любое специализированное устройство, выполняющее требуемые операции (например, устройство, построенное на основе микропроцессора или стандартная ЭВМ), например, мини-ЭВМ . СМ-3, микро ЭВМ Электроника-60, снабженная устройством ввода данных. Вычислительный блок 12, показанный на фиг. 5,работает следующим образом. Операция вычитания + + 2 - А выполняется с помощью (k/m +

-ь2)-разрядного сумматора 34.1, на первый вход которого постоянно подано число 2 Р 3, на второй вход сумматора поступает инвертированный двоичный код числа А. Выходные

5 младшие разряды сумматора 34,1 (k/m-разрядов) образуют старшие разряды выходного кода вычислительного блока 12 на выходах 22.1-22.k/m, Операция вычитания А „- ( 2) выполняется с помощью (k/m 2)-раз- рядного сумматора 34.2, на первый вход которого подается инверсный двоичный код числа 2 + 1. Выходные младшие разряды сумматора 22.2

(k/m-разрядов) образуют следующие (младшие) разряды выходного кода вычислительного блока 12. Таким же образом при помощи сумматоров 34.j и блоков инверсии 33.j производятся

0 операции вычитания А -( 2), где ,4,6.o. .Операции вычитания 2 +1-Ai, где ,5,7.,.., , выполняются с помощью сумматоров 34 i, на первые входы которых постоянно

тК|Ж+-1 . „

поданы числа 2 +2, на вторые входы сумматоров поступают инвертированные (с помощью блоков 33.1 инверсии) двоичные коды чисел А i.

0

Формула из обретения

Устройство для измерения временных интервалов, содержащее генератор импульсов опорной частоты, формирователь импульсов, первый вход которого соединен с входом устройства, два источника тока, выход первого источника тока подключен к первому входу переключателя тока, управляющий вход которого соединен с первым выходом формирователя импульсов, а второй вход подключен к выходу второго источника тока, первому входу компаратора и одному из выводов накопительного конденсатора, другой вьтод которого соединен с общей шиной, выходом переключателя тока и вторым входом компаратора, резистор, отличающееся тем, что, с целью повьппения быстродействия и точности измерений, в него введеO

5

0

ны делитель члстоты, ключ, формирователь кодов и вычислительный блок, причем второй вход формирователя импульсов подключен к выходу генератора импульсов опорной частоты и первому входу формирователя кодов, второй вход которого соединен с первым выходом формирователя импульсов, а выходы подключены к соответствующим входам вычислительного бло ка, выходы которого являются выходами устройства, второй выход фор- мировате ля импульсов подключен к управляющему входу ключа, другой вход которого соединен с общей шиной, а выход через резистор - с первым входом компаратора, выход которого подключен к вьтходу делителя частоты и третьему входу формирователя импульсов, четвертый вход которого подключен к выходу делителя частоты.

фу. 2

(pt/8. 3

V

го.т

20.m 1

W,

X.I

гг.1

n.H/m

22 Л-//77 ; n.2Kjm

n.Zx/mtj ,a.J-r/w

f2(i-) i2jn/m

Z2fi-r)f, ni-r

,W.i/f/OT

-,/г.г

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2218669C1 |

| СКОРОСТНОЙ ПРЕОБРАЗОВАТЕЛЬ "АНАЛОГ - ЦИФРА - АНАЛОГ" С БЕСТАКТОВЫМ ПОРАЗРЯДНЫМ УРАВНОВЕШИВАНИЕМ | 2012 |

|

RU2491715C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Сигнализатор совпадения фаз | 1990 |

|

SU1824595A1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

| Цифровое измерительное устройство для обработки сигналов частотных датчиков | 1989 |

|

SU1659891A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

Изобретение может быть использовано при создании измерителей частотно-временных параметров сигнала на основе преобразователей моментов времени в код, в частности в измерите, их временнъ х интервалов и синхро- нометрах. Цель изобретения - повышение быстродействия и точности измерения - достигается за счет того, что интерполяцию производят в несколько циклов . При этом в каждом последующем цикле происходит уточнение результатов предьщущих циклов. Для этого в устройство введены делитель 10 частоты, ключ 3, формирователь 11 кодов и вычислительный блок 12. Кроме , устройство содержит формирователь 1 импульсов, генератор 2 импульсов опорной частоты, резистор 4, накопительный конденсатор 5, переключатель 6 тока, источники 7 и 8 тока, компаратор 9, вход 13 устройства. Функциональные схемы формирователя импульсов, формирователя кодов и вычислительного блока приводятся в описании изобретения. 6 ил. {Л

a JT-fUlJTJTJiJTJnjTjTJTjTJTj-Lj- tf -1-Д

«7 r

-- f

cpus.$

| Преобразователь моментов времени в код | 1979 |

|

SU855995A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Gary D | |||

| Sasaki and Ronald С | |||

| lensen | |||

| Automatic Measurements with a High - Perfomance Universal Counter - Hewlett - Packarol | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1987-02-28—Публикация

1985-06-11—Подача