фиеЛ

Изобретение относится к технике телевидения и может быть использовано для формирования телевизионных синхросигналов,

Цель изобретения - упрощение устройства путем сокращения объема па мяти блоков постоянной памяти.

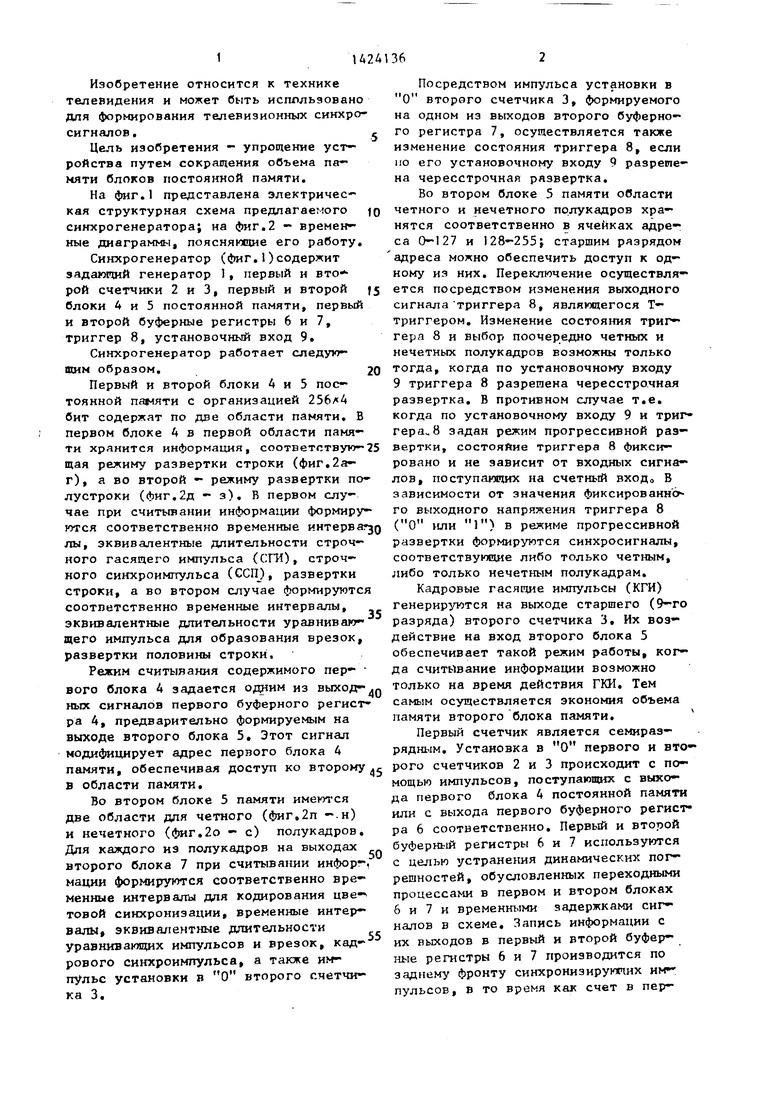

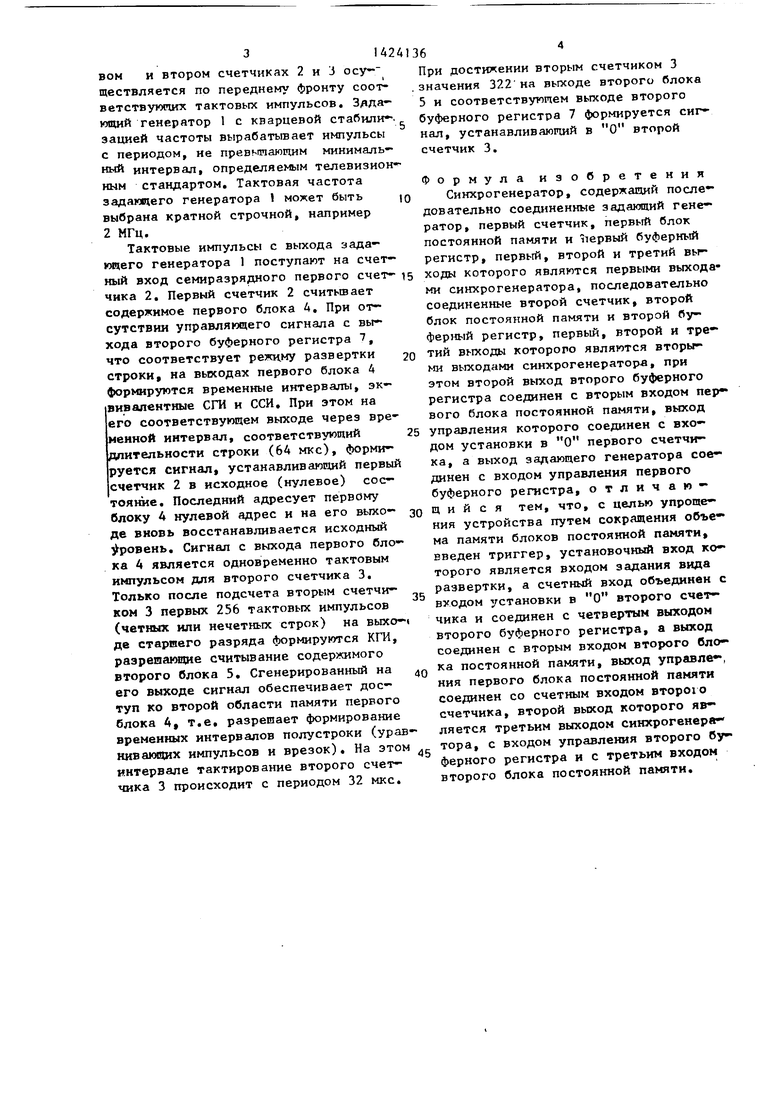

На фиг.1 представлена электричес хая структурная схема предлагаемого синхрогенератора; на фиг.2 - временные диаграммы, поясняющие его работу.

Синхрогенератор (фиг.I)содержит задающий генератор 1, первый и вто рой счетчики 2 и 3, первый и второй блоки 4 и 5 постоянной памяти, первый и второй буферные регистры 6 и 7, триггер 8, установочный вход 9.

Синхрогенератор работает следующим образом.

Первый и второй блоки 4 и 5 постоянной памяти с организацией 256А4 бит содержат по две области памяти, В первом блоке 4 в первой области памяти хранится информация, соответствую- щая режиму развертки строки (фиг.2а- г), а во второй - режиму развертки полустроки (фиг.2д - з). В первом случае при считьпвании информации формируются соответственно временные HHTepBar яы, эквивалентные длительности строчного гасящего импульса (СГИ), строчного синхроимпульса (ССП), развертки строки, а во втором случае формируются соотпетственно временные интервалы, эквивалентные длительности уравнивакг щего импульса для образования врезок, развертки половины строки.

Режим считывания содержимого пер- вого блока 4 задается одаим из выходных сигналов первого буферного регистра 4, предварительно формируемым на выходе второго блока 5, Этот сигнал модифицирует адрес первого блока 4 памяти, обеспечивая доступ ко второму в области памяти.

Во втором блоке 5 памяти имеются две области для четного (фиг.2п --н) и нечетного (фиг,2о - с) полукадров. Для каждого из полукадров на выходах второго блока 7 при считывании инфор-, мации формируются соответственно временные интервалы для кодирования цве- ТОБОЙ синхронизации, временные интервалы, эквнвапентные длительности уравнивающих импульсов и врезок, кадрового синхроимпульса, а также импульс установки в О второго счетчика 3,

,

fg

15

0

5 Q

Q с

5

Посредством импульса установки в О второго счетчика 3, формируемого на одном из выходов второго буферного регистра 7, осуществляется также изменение состояния триггера 8, если 110 его установочному входу 9 разрешена чересстрочная развертка.

Во втором блоке 5 памяти области четного и нечетного полукадров хранятся соответственно в ячейках адреса 0-127 и 128-255; старшим разрядом адреса можно обеспечить доступ к одному из них. Переключение осуществляется посредством изменения выходного сигнала триггера 8, являющегося Т- триггером. Изменение состояния триггера 8 и выбор поочередно четных и нечетных полукадров возможны только тогда, когда по установочному входу 9 триггера 8 разрешена чересстрочная развертка, В противном случае т.е. когда по установочному входу 9 и триг гера.8 задан режим прогрессивной развертки, состояйие триггера В фиксировано и не зависит от входных сигналов, поступающих на счетный вход В зависимости от значения фиксированно го выходного напряжения триггера 8 (О или 1) в режиме прогрессивной развертки формируются синхросигналы, соответствующие либо только четным, либо только иечетным полукадрам.

Кадровые гасящие импульсы (КГИ) генерируются на вьпсоде старшего (9-го разряда) второго счетчика 3, Их воздействие на вход второго блока 5 обеспечивает такой режим работы, когда считывание информации возможно только на время действия ГКИ, Тем самым осуществляется экономия объема памяти второго блока памяти.

Первый счетчик является семиразрядным. Установка в О первого и второго счетчиков 2 и 3 происходит с помощью импульсов, поступающих с выхода первого блока 4 постоянной памяти или с выхода первого буферного регистра 6 соответственно. Первый и второй буферный регистры 6 и 7 используются с целью устранения динамических погрешностей, обусловленных переходными процессами в первом и втором блоках 6 и 7 и временными задержками сигналов в схеме. Запись информации с их выходов в первый и второй буфер- ныв регистры 6 и 7 производится по заднему фронту синхронизирующих им пульсов, в то время как счет в перBOM и втором счетчиках 2 и 3 осу- ществляется по переднему фронту соот- ветствукяптс тактовых импульсов, ющий генератор 1 с кварцевой стабили -. зацией частоты вырабатьшает импульсы с периодом, не превышающим минимальный интервал, определяемым телевизионным стандартом. Тактовая частота задающего генератора 1 может быть выбрана кратной строчной, например 2 МГц,

Тактовые импульсы с выхода задающего генератора 1 поступают на счет-

При достижении вторым счетчиком 3 значеиня 322 на выходе второго блока 5 и соответствующем выходе второго буферного регистра 7 формируется сигнал, устанавливающий в О второй счетчик 3.

Формула изобретения

Синхрогенератор, содержавши последовательно соединенные задающий генератор, первый счетчик, первый блок постоянной памяти и Чтервый буферный регистр, первый, второй и третий вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхрогенератор | 1989 |

|

SU1672586A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Устройство для ввода изображения в ЭВМ | 1988 |

|

SU1644402A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2018977C1 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

| Блок буферной памяти для терминального устройства | 1987 |

|

SU1418812A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1986 |

|

SU1387038A1 |

Изобретение относится к телевидению. Цель изобретения - упрощение устр-ва. Синхрогенератор содержит за- даюишй г-р 1, счетчики 2 и 3, блоки 4 и 5 постоянной памяти (КПП), буферные регистры 6 и 7 и триггер 8 с установочным входом 9. Цель достигается путем сокращения объема памяти БПП 4 и 5. Это обеспечивается установкой такого режима работы, при котором считывание информации возможно только на время действия кадровых гасящих импульсов. 2 ил.

ный вход семиразрядного первого счет- is ходы которого являются первыми выходачика 2, Первый счетчик 2 считьшает содержимое первого блока А, При отсутствии управляющего сигнала с выхода второго буферного регистра 7, что соответствует режнму развертки строки, на выходах первого блока 4 формируются временные интервалы, эквивалентные СГИ и ССИ, При этом на его соответствующем выходе через временной интервал, соответствующий длительности строки (6А мкс), формируется сигнал, устанавливающий первый счетчик 2 в исходное (нулевое) состояние. Последний адресует первому блоку А нулевой адрес и на его выходе вновь восстанавливается исходный вровень. Сигнал с выхода первого блока А является одновременно тактовым импульсом для второго счетчика 3, Только после подсчета вторым счетчиком 3 первых 256 тактовых импульсов (четных или нечетных строк) на выхо-i де старшего разряда формируются КГИ, разрешающие считывание содержимого второго блока 5, Сгенерированный на его выходе сигнал обеспечивает доступ ко второй области памяти первого блока А, т,е, разрешает формирование

20

25

30

35

40

ни синхрогенератора, последовательно соединенные второй счетчик, второй блок постоянной памяти и второй буферный регистр, первый, второй и третий выходы которого являются вторыми выходами синхрогенератора, при этом второй выход второго буферного регистра соединен с вторым входом пер вого блока постоянной памяти, выход управления которого соединен с входом установки в О первого счетчика, а выход задающего генератора соединен с входом управления первого буферного регистра, отличающийся тем, что, с целью упрощения устройства путем сокращения объема памяти блоков постоянной памяти введен триггер, установочный вход которого является входом задания вида развертки, а счетный вход объединен с входом установки в О второго счетчика и соединен с четвертым выходом второго буферного регистра, а выход соединен с вторым входом второго блока постоянной памяти, выход управле -, ния первого блока постояниой памяти соединен со счетным входом второю счетчика, второй выход которого является третьим выходом синхрогенерввременных интервалов полустроки (уравнивающих импульсов и врезок). На этом тора, с входом управлеиия второго бу- интервале тактирование второго счет-ферного регистра и с третьим вxoдo l чика 3 происходит с периодом 32 мкс,второго блока постоянной памяти.

0

5

0

5

0

ни синхрогенератора, последовательно соединенные второй счетчик, второй блок постоянной памяти и второй буферный регистр, первый, второй и третий выходы которого являются вторыми выходами синхрогенератора, при этом второй выход второго буферного регистра соединен с вторым входом пер вого блока постоянной памяти, выход управления которого соединен с входом установки в О первого счетчика, а выход задающего генератора соединен с входом управления первого буферного регистра, отличающийся тем, что, с целью упрощения устройства путем сокращения объема памяти блоков постоянной памяти введен триггер, установочный вход которого является входом задания вида развертки, а счетный вход объединен с входом установки в О второго счетчика и соединен с четвертым выходом второго буферного регистра, а выход соединен с вторым входом второго блока постоянной памяти, выход управле -, ния первого блока постояниой памяти соединен со счетным входом второю счетчика, второй выход которого является третьим выходом синхрогенерв тора, с входом управлеиия второго бу- ферного регистра и с третьим вxoдo l второго блока постоянной памяти.

0123П20 1М

а / плгlJmллллJlГlЛJlллnлляпш

« /«

а 1т 1 Шлллш1Г1гигягц1

, 5S

inj

е г

ж 3

и

ШЛЛШШМЛШШШШШ1Г1ЛПЛЛПЯГ1ЛШУ/

г

ери г. г

, 5Sff«

injiTuinjuimirLnjijmjiJL

Г1

V

гт

| Техника средств связи | |||

| Серия Техника телевидения, вып | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| с. | |||

Авторы

Даты

1988-09-15—Публикация

1986-07-22—Подача