ИзоГ ретение относится к вычилли- тельног технике и может быть использовано при построении быстродействующих запоминающих устройств большого объема для обработки, ввода в ЭВМ и отображения графических изображений

Цель изобретения - упрощение блока .

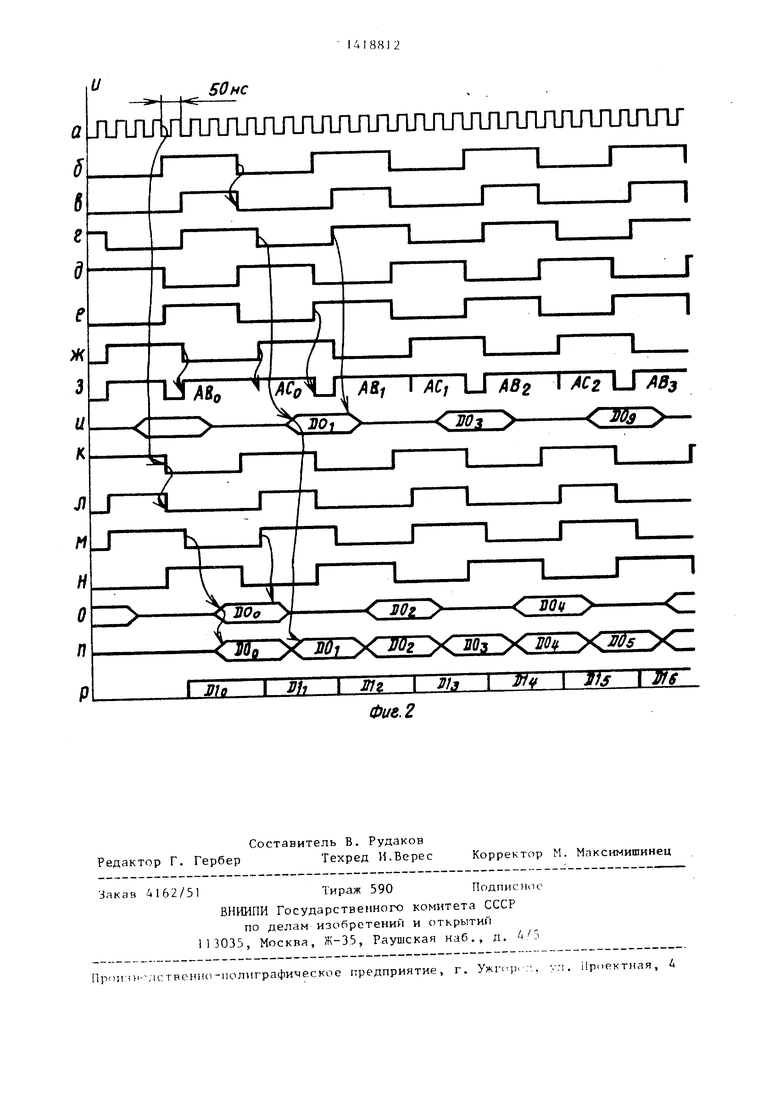

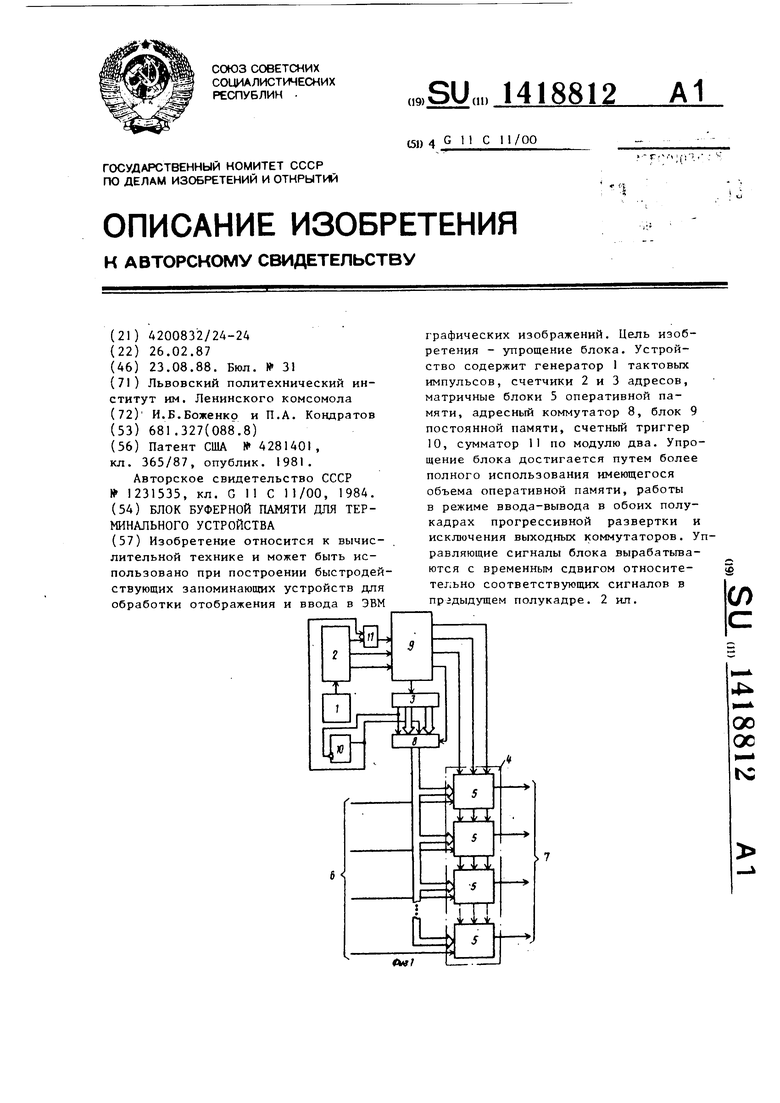

На фиг. 1 представлена функциональная схема блока буферной памяти для терминального устройства; на фиг. 2 - временные диаграммы его работы.

Блок содержит (фиг. 1) генератор 1 тактовых импульсов, первый 2 и второй 3 счетчики адресов, блок 4 памят состоящий из отдельных, по числу разрядов, матричных блоков 5 оперативно памяти, информационные входы 6 и вы- ходы 7, адресньй коммутатор 8, блок управления записью (считыванием, выполненным, например, в виде блока 9 постоянной памяти), счетный триггер 10 и сумматор 11 по модулю два. На фиг. 2 обозначены: а - сигнал тактовой частоты 20 МГц; б - сигналы блока в первом полукадре развертки; сЬ - сигнал на выходе сумматора 11 по модулю два; в,г, - соответственно сигналы выборки строк RAS и столбцов CAS блока 4; д - сигналы управления записью; е - сигналы модификации счетчика 3 адресов; ж - с гналы управления коммутатором 8; 3 - последовательность поступления сигналов с выхода коммутатора 8; и - сигналы на выходах блока) к-о - сигналы блока во полукадре развертки; к - сигнал на выходе сумматора 11; л-и - соответ- ctBeHHo сигналы RAS, GAS, WE, о - сигнал на выходе блока; п - последовательность отображения выходной информации; р - последовательность по- ступления входной информации.

Устройство работает следующит- образом.

Выходным сигналом генератора 1 тактовых импульсов (фиг. 2,а) запускается счетчик 2. Выходные напряжения счетчика 2 подаются на адресные входы блока 9. Сумматор 11 по состояниь: счетного триггера 10 управляет полярностью поступающего на вх(1Д блока 9 сигнала старшего разряда счегчика 2,

При (1янии 1 триггера 10 сигипл ст,чршего разридя счетчика 2

o

5

0

5 0 5

5

0

0

5

передается на вход блока 9 не инвертируясь (фиг. 2,6), при состоянии О он инвертируется (фиг. 2,к).|

К фронтам сигналов счетчика 2 привязаны управляющие сигналы, генерируемые блоком 9 с периодом 400 не: RAS, CAS, WE, модификации счетчика 3 и управления коммутатором 8.

Счетчик 3 модифицируется по переднему фронту сигнала с четвертого выхода блока 9 (фиг.2,е). По состоянию О сигнала на пятом выходе блока 9 (фиг. 2,ж) коммутатор 8 подключает к адресным входам блоков 5 семь младших разрядов счетчика 3 (сигналы ) и сигнал состояния триггера 10 - ЛЕо (фиг. 2,3). По отрица0

тельному фронту сигнала MS с первого входа блока 9 (фиг. 2,в) ;сигнал AR заносится в адресные регистры блоков 5. По состоянию 1 сигнала управления коммутатором 8 (фиг.2,ж) к адресным входам блоков 5 подключаются старшие разряды счетчика 3 - сигналы АС,-АС(фиг. 2 , з). .По отрицательному фронту сигнала CAS с второго входа блока 9 (фиг.2,г) сигнал АС заносится в адресные регистры блоков 5, производится выборка микросхем памяти блоков 5 и на выход 7 блока поступает считанная информация (фиг.2,и). По положительному фронту сигнала CAS выходы блоков 5 переходят в третье состояние.

По отрицательному фронту сигнала WE с третьего выхода блока 9(фиг.2,д) информация, поступающая на входы 6 блока (фиг. 2,р), заносится в выбранные ячейки памяти.

В первом полукадре (при состоянии 1 триггера 10) выборка ячеек бло- кой 5 производится перебором адресов Af,-AR,,AC-,-ACj при I. Так об- рабатьшается первый гголукадр изображения .

По переполнению счетчика 3 отрицательным фронтом старшего разряда счетчика 8 триггера 10 устанавливается в состояние О и начинается обработка второго пплукадра. Сигнал, поступающий на вход блока 9 с тора II, инвертируотся. Тем самым обеспечивается слвпг на 400 не сигналов, генерируемых Р.- оком 9 во втором полукадре (фиг. 2,л-н). Выборка ячеек памяти прои ммится перебором адресов при (;. П:1г| поступает на выход 7 с, i -iniu OM на 400 не

14

относительно информации, считанной , в первом полукадре. Затем по переполнению счетчика 3 триггер 10 вновь устанавливается в состояние 1 и начитается обработка первого полукадра .

Последовательность отображения изображения, образованного положением первого и второго полукадров прогрессивной развертки (фиг. 2,п)« Требование регенерации информции в. блоке 4 памяти обеспечивается путем перебора адресов в течение строки п олукадра развертки за 64 мс.

Формула изобретения

Блок буферной памяти для терминального устройства, содержащий генератор тактовых импульсов, первый и второй счетчики адресов, блок управления записью-считыванием, адресный коммутатор и матричные блоки оперативной памяти, информационные входы которых являются информацвон- ными входами устройства, информационные выходы устройства, информационные выходы матричных блоков оперативной памяти являются информационными выходами устройства, адресные входы матричных блоков оперативной памяти поразрядно объединены и подключены к выходам адресного коммутатора, выход генератора тактовых

812

импульсов подключен к счетному входу первого счетчика адресов, выходы младших разрядов которого подключены к младшим адресным входам блока управления записью-считыванием, первый, второй и третий выходы которого соединены соответственно с входами выборки строк, выборки столбцов

10 и вход ами записи матричных блоков оперативной памяти, четвертый и пятый выходы блока управления записью-считыванием соединены соответственно со счетным входом второго счетчика адресов

15 и управляющим входом адресного коммутатора, выходы младших и старших разрядов второго счетчика адресов подключены соответственно к информационным входам первой и второй групп адресно20 го коммутатора, отличающий- с я тем, что, с целью упрощения блока, в него введены счетный триггер и сумматор по модулю два, выход которого подключен к старшему адресному входу

25 блока управления записью-считыванием, первый вход сумматора по модулю два и информационный вход адресного коммутатора соединены с выходом счетного триггера, счетный вход которого под3( ключен к выходу старшего разряда второго счетчика адресов, второй вход сумматора по модулю два соединен с выходом старшего разряда первого счетчика адресов.

50нс

I JJlo nil 1Пг л Sfa lfs Шб

Фиг. 2

сж

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок буферной памяти для терминального устройства | 1989 |

|

SU1633454A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих запоминающих устройств для обработки отображения и ввода в ЭВМ графических изображений. Цель изобретения - упрощение блока. Устройство содержит генератор 1 тактовых импульсов, счетчики 2 и 3 адресов, матричные блоки 5 оперативной памяти, адресный коммутатор 8, блок 9 постоянной памяти, счетный триггер 10, сумматор 11 по модулю два. Упрощение блока достигается путем более полного использования имеющегося объема оперативной памяти, работы в режиме ввода-вывода в обоих полукадрах прогрессивной развертки и исключения выходных коммутаторов. Управляющие сигналы блока вырабатьгаа- ются с временным сдвигом относите- тельно соответствующих сигналов в пр адыдущем полукадре. 2 ил. (Л СХ) 00 tc Ф

| Патент США 4281401, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Авторское свидетельство СССР № 1231535, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-26—Подача