Фиг.1

15 ЮП

Изобретение относится к вычислительной технике, в частности к устройствам распределения заданий между процессорами, и может быть исполь эовано в многомашинных вычислительных системах для распределения нагрузки между процессорами (ЭВМ).

Цель изобретения - расширение области применения устройства за счет возможности дерераспределения . заданий между процессорами.

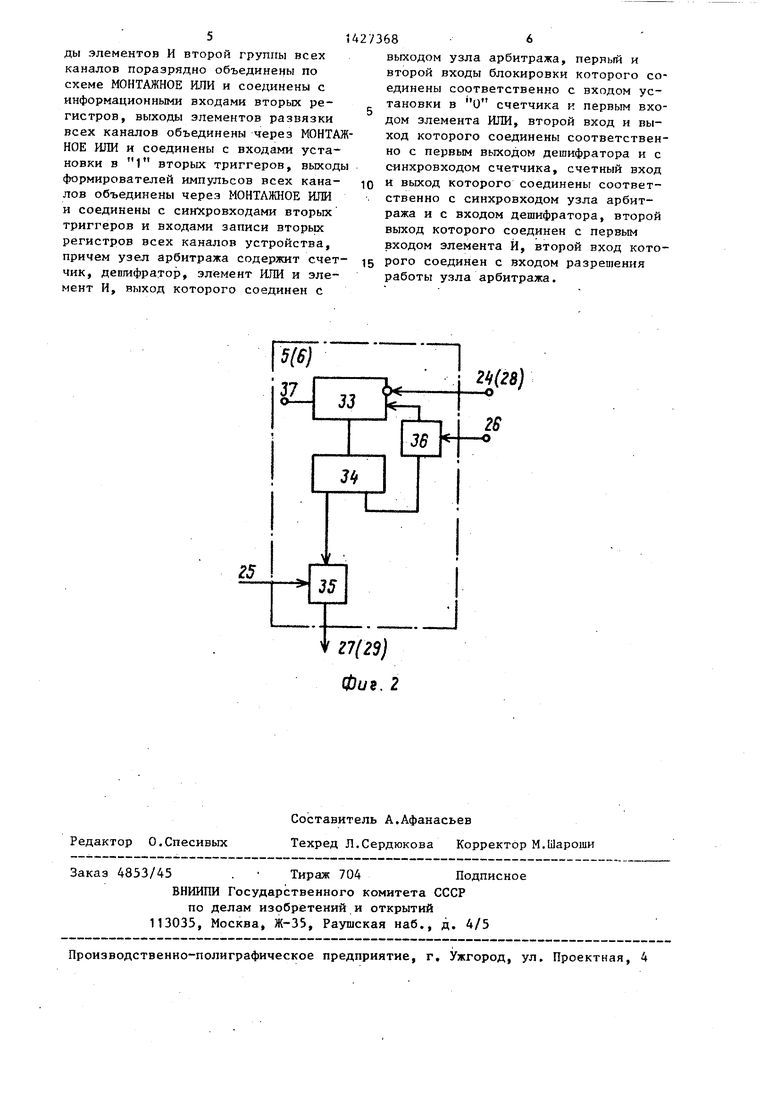

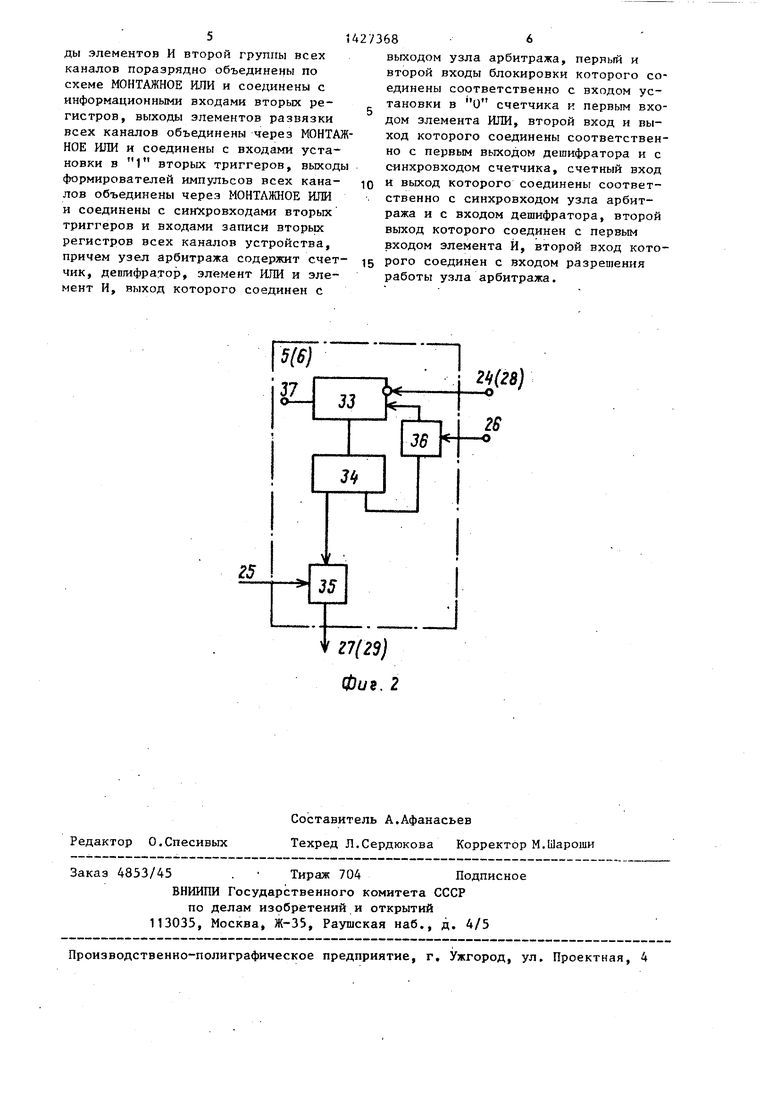

На фиг.1 представлена структурная схема одного канала устройства; на фиг.2 - схема узла арбитража.

Устройство (фиг.1) содержит регистры 1,2, группы элементов И 3,4, .узлы 5,6 арбитража, триггеры 7-9, формирователь 10 импульса, элементы И 11-13, элемент 14 развязки, общую магистраль 15, общие линии 16,17 сопровождения, вход 18 запроса, первый и второй управляющие входы 19, 20, сигнальные выходы 21,22 канала, кодовый выход V.3, вход 24- начальной установки, первый узел 5 арбитража имеет входы 25 разрешения работы, блокировки 26 и выход 27, второй узел 6 арбитража имеет вход 28 блокировки и выход 29, триггер 7 имеет входы установки 3U, 31, в устройстве имеется вход 32 кода запроса. Узел 5.(6) арбитража (фиг.2) содержит счетчик 33, дешифратор 34, элемент И 35, ИЛИ 36, вход 37 синхронизации (фиг.2).

Работа устройства заключается в следующем.

Для начальной установки подается сигнал на вход 24, в триггеры 8, 9, записываются .О, а счетчик 33 узла 5 устанавливается в нулевое состояние. При состоянии О триггера 9 счетчик ЗЗ узла 6 устанавливается в нулевое состояние, при этом его счатньм режим блокируется.

Запрос от К-го источника запросо (абонента) заносится в регистр 1 с входа 32 nd .сигналу на входе 18.

Если К-й процессор, закрепленньй для обслуживания запросов от К-го абонента, исправен, о чем свидетельтвует состояние триггера 1 триггера 7, то через элемент И 11 подается сигнал на вход 21 прерывания К-го процессора. Вектор прерывания (код запроса) процессор считьгоает с регистра 1 через группу элементов И 3 по сигналу с входа 19. Если К-й

Q

0 5 О

0 5

5

0

5

процессор неисправе), о чем свидетельствует состояние О триггера 7, то по сигналу на входе 18 через элемент И 12 производится запись 1 в триггер 8. Единичное состояние триггера 8 К-го канала соответствует запросу от К-го канала устройства (от К-го абонента) на захват магистрали 15. 11ри состоянии 1 триггера 8 на вход 25 узла 5 арбитража подается 1, разрешающая захват общей, магистрали 15 К-м каналом при Е-м состоянии счетчика 33 К-го канала. Счетчики 33 всех каналов начинают счет с одинакового состояния (нулевого), изменен1 е состояний счетчиков 33 производится с одной частотой на входах 37, поэтому сигналы на выходах узлов арбитража различных каналов формируются в разные моменты времени, так как к входу элемента И 35 К-го канала подключается К-й выход дешифратора 34. При появлении 1 на К-м выходе дешифратора 34 при состоянии 1 триггера 8 на выходе элемента И 35 К-го канала вырабатьшается сигнал, подаваемый на выход 27, причем длительность, этого сигнала равна длительности синхросигнала на входе 37. По сигналу на выходе 27 узла 5 код запроса (вектор прерывания), занесенный в регистр 1, через группу элементов И 4 (магистральные усилители) выдается на общую магистраль 15. Код запроса, передаваемьй через общую магистраль 15, сопровождается сигналом, формируемым формирователем 10 и выдаваемым на общую линию 16. По заднему фронту сигнала на выходе 27 узла 5 арбитража триггер 8 устанавливается в состояние О (выход 27 узла 5 подключен к С-входу триггера 8, на D-вход которого постоянно подается О). По сигналу сопровождения на общей линии 16 во всех каналах в триггер 9 заносятся О, работа счетчиков 33 узлов 5 арбитража блокируется (подается сигнал на вход установки), а работа счетчиков 33 узлов 6 арбитража разрешается (снимается сигнал установки счетчиков 33). Узлы .6 предназначены для исключения распределения запросов, передаваемых через общую магистраль 15, в несколько процессоров,

Все счетчики 33 узлов 6 арбитража начинают счет с одинакового соетояния (о), а наращивание их со- держимого производится с одинаковой частотой с входа 37. Загрузка запроса в К-й процессор разрешается при его исправности (1 в триггере 7) и К-м состоянии счетчика 33 узла 6, при этом на выходе 29 узла 6 формируется сигнал (для Е-го канала к входу элемента И 35 подключен К-й выход дешифратора 34), если К-й процессор исправен (1 в триггере 7), то на выходе элемента И 13 формируется сигнал 22 прерывания К-го процессора, вектор прерывания с регистра 2 по сигналу 2U. В регистр 2 в ек тор прерывания занесен с общей магистрали 15 по сигналу сопровояаде- ния на линии 16, Сигнал с выхода элемента И 13 через элемент 14 развязки вьщается на общую линию 17, в триггеры 9 всех каналов записываются О. При состоянии О триггеров 9 разрешается счетный режим счетчиков 33 узлов 5 арбитража, а счетный режим счетчиков 33 узлов 6 арбитража блокируется (производится их установка в исходное состояние) . При этом начинается распределение очередного запроса через общую магистраль в случае требований от источников запросов, подключенны к неисправным процессорам.

Формула изобретени

Многоканальное устройство для распределения заданий процессорам, содержащее К каналов, каждый из ко- Topbix содержит первый и второй регистры, первую и вторую группы элементов И, с первого по третий элементы И, причем информационный вход канала соединен с информационным входом первого регистра, соответствующего канала, выход которого соединен с первыми входами элементов И первой и второй групп, выходы элементов И первой группы М-го канала (,К) соединены с информационным выходами канала для подключения к входам М-го процессора, вход запрос М-го канала устройства соединен с первыми входами первого и второго элементов И М-го кангша, отличающееся тем, что, с целью расширения области применения за счет возможности перераспределения заданий между процессорами, каждый

0

5

0

5

0

5

0

5

0

5

канал дополнительно содержит первый и второй узлы арбитража, элемент развязки, с первого по третий триггеры и формирователь импульса, в каждом канале вход формирователя импульса соединен с вторыми входами элементов И BTOpoii группы, с выходом первого узла арбитража и с синхро- входом первого триггера, вход установки в О которого соединен с входом установки второго триггера, с первым входом блокировки первого узла арбитража и с входом начальной установки соответствующего канала устро1 ства, вход запроса которого соединен с входом записи первого регистра, входы установки в 1 и в О третьего триггера соединены соответственно с входами признака исправности и признака неисправности процессора соответствующего канала устройства, в каждом канале прямой выход третьего триггера соединен с вторым входом первого и первым входом третьего элементов И, второй вход третьего элемента И соединен с выходом второго узла арбитража, первый вход блокировки которого соединен с вторым входом блокировки первого узла арбитража, третьим входом третье- . го элемента И и с выходом второго триггера, выход третьего элемента И М-го канала соединен с входом элемента развязки и первым сигнальным вьссодом М-го канала для подключения к первому входу прерывания М-го процессора, выход первогб элемента И М-го канала соединен с вторым сигнальным выходом М-го канала для подключения к второму входу прерывания М-го процессора, инверсный выход третьего триггера соединен с вторым входом второго элемента И, выход которого соединен с входом установки в 1 первого триггера, выхрд которого соединен с входом разрешения работы первого узла арбитража, информационные входы первого и второго триггеров соединены соответственно с шинами логического нуля и единицы устройства, первый и второй входы чтения М-го канала устройства соединены соответственно с вторыми входами элементов И первой группы и с входом чтения второго регистра, выходы которого поразрядно объединены с информационнь ми выходами М-го канала по схеме МОНТАЖНОЕ ИЛИ, выходы элементов И второй группы всех каналов поразрядно объединены по схеме МОНТАЖНОЕ ИЛИ и соединены с информационными входами вторых регистров, выходы элементов развязки всех каналов объединены через МОНТАЖ НОЕ ИЛИ и соединены с входами установки в 1 вторых триггеров, выходы формирователей импульсов всех каналов объединены через МОНТАЖНОЕ ИЛИ и соединены с сиюсровходами вторьпс триггеров и входами записи вторьрс регистров всех каналов устройства, причем узел арбитража содержит счетчик, депгафратор, элемент ИЛИ и элемент И, выход которого соединен с

273686

выходом узла арбитража, перяый и второй входы блокировки которого соединены соответственно с входом установки в О счетчика и первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с первьпу выходом дешифратора и с синхровходом счетчика, счетный вход 0 и выход которого соединены соответственно с синхровходом узла арбитража и с входом дешифратора, второй выход которого соединен с первым входом элемента И, второй вход кото- 15 рого соединен с входом разрешения работы узла арбитража.

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах для распределения заданий между процессорами. Цель изобретения - расширение области применения устройства за счет перераспределения заданий между процессорами. Многоканальное устройство для распределения заданий процессорам содержит К каналов, в каждьгй из которых входят регистры 1 и 2, группы элементов И 3 и 4, узлы арбитража 4 и 5, триггеры 7,8 и 9, формирователь импульса 10, элементы И 11, 12 и 13, элемент развязки 14. В случае нормальной работы процессора задание, поступившее на вход 32 канала, распределяется в процессор своего канала. Если же процессор вьш1ел из строя, то задание через группу элементов И 4 по магистрали 15 распределяется в исправный процессор устройства. 2 ил. с (Л 4 СО О 00

HZte

Фиг. 2

Л

2(28) -о

| Устройство для распределения заданий процессорам | 1985 |

|

SU1278848A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1124309A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-30—Публикация

1987-03-30—Подача